# **3-Phase Power MOSFET Controller for Automotive Applications**

### Features and Benefits

- Drives wide range of N-channel MOSFETs in 3-phase bridges

- PFM boost converter for use with low-voltage battery supplies

- Internal LDO regulator for gate-driver supply

- Bootstrap circuits for high-side gate drivers

- Current monitor output

- Adjustable battery overvoltage detection

- Diagnostic outputs

- Motor lead short-to-battery, short-to-ground, and bridgeopen protection

- Undervoltage protection

- –40°C to 150°C T<sub>I</sub> operation

- Thermal shutdown

### Package 36-pin QSOP (LQ):

### Description

The A3935 is designed specifically for automotive applications that require high-power motors. Each provides six high-current gate drive outputs capable of driving a wide range of N-channel power MOSFETs.

A requirement of automotive systems is steady operation over a varying battery input range. The A3935 integrates a pulsefrequency modulated boost converter to create a constant supply voltage for driving the external MOSFETs. Bootstrap capacitors are utilized to provide the above battery supply voltage required for N-channel FETs.

Direct control of each gate output is possible via six TTLcompatible inputs. A differential amplifier is integrated to allow accurate measurement of the current in the three-phase bridge.

Diagnostic outputs can be continuously monitored to protect the driver from short-to-battery, short-to-supply, bridge-open, and battery under/overvoltage conditions. Additional protection features include dead-time, VDD undervoltage, and thermal shutdown.

The A3935 is supplied in a 36-lead 0.8 mm pitch QSOP (package LQ, similar to SOICW). The lead (Pb) free variants (suffix -T) have 100% matte tin leadframe plating.

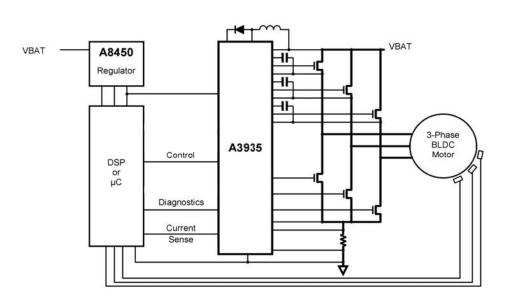

### **Typical Application**

#### **Selection Guide**

| Part Number  | Pb-free | Packing          | Terminals | Package              |  |

|--------------|---------|------------------|-----------|----------------------|--|

| A3935KLQTR*  | _       | 1E00 pieces/real | 26        | QSOP (similar to     |  |

| A3935KLQTR-T | Yes     | 1500 pieces/reel | 36        | SOICW) surface mount |  |

\* Variant is in production but has been determined to be NOT FOR NEW DESIGN. This classification indicates that sale of the variant is currently restricted to existing customer applications. The variant should not be purchased for new design applications because obsolescence in the near future is probable. Samples are no longer available. Status change: November 2, 2009.

#### **Absolute Maximum Ratings**

| Parameter                                 | Symbol              | Conditions                                                                                                                                                              | Rating      | Units |  |

|-------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|--|

|                                           | V <sub>BAT</sub>    | VBAT pin                                                                                                                                                                |             |       |  |

|                                           | V <sub>DRAIN</sub>  | VDRAIN pin                                                                                                                                                              | 0.0 to 40   |       |  |

| Load Supply Voltage                       | V <sub>BOOST</sub>  | VBOOST pin                                                                                                                                                              | -0.6 to 40  | V     |  |

|                                           | V <sub>BOOSTD</sub> | VBOOSTD pin                                                                                                                                                             |             |       |  |

|                                           | V <sub>GHx</sub>    | GHA, GHB, and GHC pins                                                                                                                                                  | -4 to 55    | V     |  |

|                                           | V <sub>Sx</sub>     | SA, SB, and SC pins                                                                                                                                                     | -4 to 40    | V     |  |

| Output Voltage Range                      | V <sub>GLx</sub>    | GLA, GLB, and GLC pins                                                                                                                                                  | -4 to 16    | V     |  |

|                                           | V <sub>Cx</sub>     | CA, CB, and CC pins                                                                                                                                                     | –0.6 to 55  | V     |  |

|                                           | V <sub>CSx</sub>    | CSN and CSP pins                                                                                                                                                        | 4 1- 0 5    |       |  |

| Sense Circuit Voltage                     | V <sub>LSS</sub>    | LSS pin                                                                                                                                                                 | -4 to 6.5   | V     |  |

| Logic Supply Voltage                      | V <sub>DD</sub>     | VDD pin                                                                                                                                                                 |             |       |  |

|                                           | V <sub>OVSET</sub>  | OVSET pin                                                                                                                                                               |             |       |  |

|                                           | V <sub>BOOSTS</sub> | V <sub>BOOSTS</sub> BOOSTS pin                                                                                                                                          |             | V     |  |

| Logic Input/Output                        | V <sub>CSOUT</sub>  | CSOUT pin                                                                                                                                                               | -0.3 to 6.5 | V     |  |

|                                           | V <sub>DSTH</sub>   | VDSTH pin                                                                                                                                                               |             |       |  |

|                                           |                     | remaining logic pins                                                                                                                                                    |             |       |  |

| ESD Rating – Human Body Model             |                     | AEC-Q100-002; all pins                                                                                                                                                  | 2.5         | kV    |  |

| ESD Rating – Charged Device Model         |                     | AEC-Q100-011; all pins                                                                                                                                                  | 1050        | V     |  |

| Operating Temperature                     | T <sub>A</sub>      | Range K                                                                                                                                                                 | -40 to 135  | °C    |  |

| Junction Temperature* T <sub>J(max)</sub> |                     | Fault conditions that produce excessive junction temperature will activate device thermal shutdown circuitry. These conditions can be tolerated, but should be avoided. | 150         | °C    |  |

| Storage Temperature Range                 | T <sub>stg</sub>    |                                                                                                                                                                         | –55 to 150  | °C    |  |

Functional Block Diagram

# ELECTRICAL CHARACTERISTICS at $T_J = -40^{\circ}$ C to 150°C, $V_{BAT} = 7$ to 16 V, $V_{DD} = 4.75$ to 5.25 V, ENABLE = 22.5 kHz, 50% duty cycle, two phases active;unless otherwise noted

| Characteristics                            | Symbol               | Conditions                                                                                                                      | Min.                       | Typ <sup>1</sup> . | Max.      | Units |

|--------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|-----------|-------|

| Power Supply                               | ·                    |                                                                                                                                 |                            |                    |           |       |

| V <sub>DD</sub> Supply Current             | I <sub>DD</sub>      | All logic inputs = 0 V                                                                                                          | _                          | -                  | 7.0       | mA    |

| V <sub>BAT</sub> Supply Current            | I <sub>BAT</sub>     | All logic inputs = 0 V                                                                                                          | _                          | -                  | 3.0       | mA    |

| Battery Voltage Operating Range            | V <sub>BAT</sub>     |                                                                                                                                 | 7.0                        | -                  | 40        | V     |

| Postatran Diado Fonward Valtago            | N                    | $I_{DBOOT} = -I_{Cx} = 10 \text{ mA}, V_{DBOOT} = V_{REG} - V_{Cx}$                                                             | 0.8                        | -                  | 2.0       | V     |

| Bootstrap Diode Forward Voltage            | V <sub>DBOOT</sub>   | $I_{\text{DBOOT}} = -I_{\text{Cx}} = 100 \text{ mA}$                                                                            | 1.5                        | -                  | 2.3       | V     |

| Bootstrap Diode Resistance                 | r <sub>DBOOT</sub>   | $r_{DBOOT}(100 \text{ mA}) = (V_{DBOOT}(150 \text{ mA})) - V_{DBOOT}(50 \text{ mA})) / 100 \text{ mA}$                          | 2.5                        | -                  | 7.5       | Ω     |

| Bootstrap Diode Current Limit <sup>2</sup> | I <sub>DM</sub>      | $3 V < V_{REG} - V_{Cx} < 12 V$                                                                                                 | -150                       | -                  | -1150     | mA    |

| Bootstrap Quiescent Current                | I <sub>Cx</sub>      | $V_{Cx}$ = 40 V, GHx = ON                                                                                                       | 10                         | -                  | 30        | μA    |

| Bootstrap Refresh Time                     | t <sub>refresh</sub> | $V_{Sx}$ = low, to guarantee $\Delta V$ = +0.5 V refresh of 0.47 µF<br>Bootstrap Capacitor, CBOOT, to $V_{Cx} - V_{Sx}$ = +10 V | -                          | -                  | 2.0       | μs    |

| VREG Output Voltage <sup>3</sup>           | V <sub>REG</sub>     | V <sub>BAT</sub> = 7 to 40 V, V <sub>BOOST</sub> from Boost Regulator                                                           | 12.7                       | -                  | 14        | V     |

| VREG Dropout Voltage <sup>4</sup>          | V <sub>REGDO</sub>   | $V_{\text{REGDO}} = V_{\text{BOOST}} - V_{\text{REG}}$ , $I_{\text{REG}} = 40 \text{ mA}$                                       | -                          | 0.9                | _         | V     |

| Gate Drive Average Supply Current          | I <sub>REG</sub>     | No external dc load at VREG, C <sub>REG</sub> = 10 µF                                                                           | -                          | -                  | 40        | mA    |

| VREG Input Bias Current                    | I <sub>REGbias</sub> | Current into V <sub>BOOST</sub> , ENABLE = 0                                                                                    | -                          | -                  | 4.0       | mA    |

| Boost Supply                               |                      | 1                                                                                                                               |                            |                    |           |       |

| VBOOST Output Voltage Limit                | VBOOSTM              | V <sub>BAT</sub> = 7 V                                                                                                          | 14.9                       | -                  | 16.3      | V     |

| VBOOST Output Voltage Limit Hysteresis     | ΔV <sub>BOOSTM</sub> |                                                                                                                                 | 35                         | -                  | 180       | mV    |

| Boost Switch On Resistance                 | r <sub>DS(on)</sub>  | I <sub>BOOSTD</sub> < 300 mA                                                                                                    | -                          | 1.4                | 3.3       | Ω     |

| Boost Switch Maximum Current               | I <sub>BOOSTSW</sub> |                                                                                                                                 | -                          | -                  | 300       | mA    |

| Boost Current Limit Threshold Voltage      | V <sub>BI(th)</sub>  | Increasing V <sub>BOOSTS</sub>                                                                                                  | 0.45                       | -                  | 0.55      | V     |

| Off Time                                   | t <sub>off</sub>     |                                                                                                                                 | 3.0                        | -                  | 8.0       | μs    |

| Blanking Time                              | t <sub>blank</sub>   |                                                                                                                                 | 100                        | -                  | 220       | ns    |

| Control Logic                              |                      | 1                                                                                                                               |                            |                    |           |       |

|                                            | V <sub>I(1)</sub>    | Minimum high level input for logic 1                                                                                            | 2.0                        | -                  | _         | V     |

| Logic Input Voltage                        | V <sub>I(0)</sub>    | Maximum low level input for logic 0                                                                                             | _                          | -                  | 0.8       | V     |

| Legis Japant Current                       | I <sub>I(1)</sub>    | $V_{I} = V_{DD}$                                                                                                                | _                          | -                  | 500       | μA    |

| Logic Input Current                        | I <sub>I(0)</sub>    | V <sub>1</sub> = 0.8 V                                                                                                          | 50                         | -                  | -         | μA    |

| Logic Input Hysteresis                     | V <sub>lhys</sub>    |                                                                                                                                 | 100                        | -                  | 300       | mV    |

| Logic Output High Voltage                  | V <sub>O(H)</sub>    | I <sub>O(H)</sub> = -800 μA                                                                                                     | V <sub>DD</sub> -<br>0.8   | -                  | _         | V     |

| Logic Output Low Voltage                   | V <sub>O(L)</sub>    | I <sub>O(L)</sub> = 1.6 mA                                                                                                      | _                          | -                  | 0.4       | V     |

| Gate Drives, GHx (internal source, or uppe |                      |                                                                                                                                 |                            |                    |           |       |

|                                            |                      | GHx: $I_{xU} = -10$ mA, $V_{Sx} = 0$                                                                                            | V <sub>REG</sub> -<br>2.26 | -                  | $V_{REG}$ | V     |

| Output High Voltage                        | V <sub>DSL(H)</sub>  | GLx: I <sub>xU</sub> = -10 mA, V <sub>LSS</sub> = 0                                                                             | V <sub>REG</sub> -<br>0.26 | -                  | $V_{REG}$ | V     |

| Source Current (pulsed)                    | 1                    | V <sub>SDU</sub> = 10 V, T <sub>J</sub> = 25°C                                                                                  | _                          | 800                | _         | mA    |

| Source Current (pulsed)                    | I <sub>xU</sub>      | V <sub>SDU</sub> = 10 V, T <sub>J</sub> = 135°C                                                                                 | 400                        | -                  | _         | mA    |

| Source On Posistance                       | r                    | $I_{xU} = -150 \text{ mA}, T_J = 25^{\circ}\text{C}$                                                                            | 4.0                        | -                  | 10        | Ω     |

| Source On Resistance                       | r <sub>SDU(on)</sub> | I <sub>xU</sub> = -150 mA, T <sub>J</sub> = 135°C                                                                               | 7.0                        | _                  | 15        | Ω     |

Continued on the next page...

# ELECTRICAL CHARACTERISTICS (continued) at $T_J = -40^{\circ}$ C to 150°C, $V_{BAT} = 7$ to 16 V, $V_{DD} = 4.75$ to 5.25 V, ENABLE = 22.5 kHz, 50% duty cycle, two phases active;unless otherwise noted

Characteristics Symbol Conditions Min. Typ<sup>1</sup>. Max. Units Gate Drives, GLx (internal sink or lower switch stages)6 V<sub>DSL</sub> = 10 V, T<sub>J</sub> = 25°C 850 mΑ \_ \_ Sink Current (pulsed)  $I_{xL}$ V<sub>DSL</sub> = 10 V, T<sub>J</sub> = 135°C 550 mΑ I<sub>xl</sub> = 150 mA, T<sub>l</sub> = 25°C 1.8 6.0 Ω \_ Sink On Resistance r<sub>DSL(on)</sub> I<sub>xl</sub> = 150 mA, T<sub>l</sub> = 135°C 3.0 7.5 Ω Gate Drives, GHx, GLx (General)5,6 Propagation Delay, Logic only Logic input to unloaded GHx, GLx t<sub>pd</sub> \_ \_ 150 ns Output Skew Time t<sub>sk(o)</sub> Grouped by edge, phase-to-phase \_ 50 ns Dead Time (shoot-through prevention) Between GHx, GLx transitions of same phase 75 \_ 180 t<sub>dead</sub> ns Sense Amplifier CSP = CSN = 0 V Input Bias Current<sup>2</sup> -180 -360 μA I<sub>bias</sub> \_ CSP = CSN = 0 V Input Offset Current<sup>2</sup> ±35 μΑ \_ IIO \_ CSP with respect to GND 80 kΩ \_ \_ Input Resistance ri CSN with respect to GND 4.0 kΩ \_ Diff. Input Operating Voltage VID  $V_{ID} = CSP - CSN, -1.3V < CSP,N < 4V$ \_ ±200 mV \_ V<sub>OO</sub> Output Offset Voltage CSP = CSN = 0V450 77 250 mV Output Offset Voltage Drift CSP = CSN = 0 VuV/°C 100  $\Delta V_{OO}$ \_ \_ Input Common Mode Operating Range  $V_{IC}$ CSP = CSN -1.5 4.0 V \_  $A_V$ Voltage Gain V<sub>ID</sub> = 40 to 200 mV 18.6 19.2 19.8 V/V  $V_{ID}$  = 0 to 40 mV,  $V_{O}$  = (19.2 ×  $V_{ID}$ ) +  $V_{O}$  +  $E_{v}$ Low Output Voltage Error E<sub>V</sub> ±25 \_ \_ mV A<sub>VC</sub> DC Common Mode Attenuation CSP = CSN = 200 mV 28 dB \_ Output Resistance 8.0 Ω V<sub>CSOUT</sub> = 2.0 V r<sub>O</sub> \_ \_ V<sub>DD</sub>-Output Dynamic Range  $I_{CSOUT} = -100 \ \mu A$  at top rail, 100  $\mu A$  at bottom rail 0.075 V V<sub>CSOUT</sub> 0.25 Output Current, Sink I<sub>sink</sub> V<sub>CSOUT</sub> = 2.5 V 20 \_ mΑ \_ Output Current, Source<sup>2</sup>  $V_{CSOUT} = 2.5 V$ -1.0mΑ Isource \_ PSRR<sub>VDD</sub> CSP = CSN = GND, frequency = 0 to 1 MHz VDD Supply Ripple Rejection 20 dB PSRR<sub>VREG</sub> CSP = CSN = GND, frequency = 0 to 300 kHz VREG Supply Ripple Rejection 45 dB \_ \_ Small Signal 3 dB Bandwidth BW<sub>f3db</sub> 10 mV input 1.6 MHz \_ \_ V<sub>cm</sub> = 250 mV(pp), frequency = 0 to 800 kHz AC Common Mode Attenuation 26 \_ dB \_ A<sub>VC(ac)</sub> 200 mV step input, measured at 10/90% points Output Slew Rate (positive or negative) 10 SR \_ V/µs \_ Fault Logic Decreasing V<sub>DD</sub> VDD Undervoltage 3.8 V V<sub>DD(uv)</sub> 43 \_  $\Delta V_{DD(uv)}$ VDD Undervoltage Hysteresis  $V_{DD(recovery)} - V_{DD(uv)}$ 100 \_ 300 mV OVSET Operating Voltage Range V<sub>SET(ov)</sub> 0 \_  $V_{DD}$ V OVSET Calibrated Voltage Range V<sub>SET(ov)cal</sub> 0 \_ 2.5 V OVSET Input Current Range<sup>2</sup> -1.01.0 I<sub>SET(ov)</sub> μΑ 0 V < V<sub>SET(ov)</sub> < 2.5 V 19.4 40 V \_ VBAT Overvoltage Range V<sub>BAT(ov)</sub> Increasing V<sub>BAT</sub>, V<sub>SET(ov)</sub> = 0 V 19.4 25.4 V 22.4 VBAT Overvoltage Hysteresis  $\Delta V_{BAT(ov)}$ Percent of V<sub>BAT(ov)</sub> value set by V<sub>SET(ov)</sub> % 90 15

Continued on the next page ...

#### ELECTRICAL CHARACTERISTICS (continued) at $T_J = -40^{\circ}$ C to 150°C, $V_{BAT} = 7$ to 16 V, $V_{DD} = 4.75$ to 5.25 V, ENABLE = 22.5 kHz, 50% duty cycle, two phases active; unless otherwise noted

| Characteristics                       | Symbol                | Conditions                                                                                                                          | Min.                       | Typ <sup>1</sup> . | Max.                       | Units |

|---------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|----------------------------|-------|

| VBAT Overvoltage Gain Constant        | K <sub>BAT(ov)</sub>  | $V_{BAT(ov)} = (K_{BAT(ov)} \times V_{SET(ov)}) + V_{BAT(ov)}(0);$<br>$V_{BAT(ov)(0)} \text{ at } V_{SET(ov)} = 0$                  | _                          | 12                 | -                          | V/V   |

| VBAT Undervoltage                     | V <sub>BAT(uv)</sub>  | Decreasing V <sub>BAT</sub>                                                                                                         | 5.0                        | 5.25               | 5.5                        | V     |

| VBAT Undervoltage Hysteresis          | V <sub>BAT(uv)</sub>  | Percent of V <sub>BAT(uv)</sub>                                                                                                     | 8.0                        | -                  | 12                         | %     |

| VREG Undervoltage                     | V <sub>REG(uv)</sub>  | Decreasing V <sub>REG</sub>                                                                                                         | 9.9                        | -                  | 11.1                       | V     |

| VDSTH Input Range                     | V <sub>DSTH</sub>     |                                                                                                                                     | 0.5                        | -                  | 3.0                        | V     |

| VDSTH Input Current                   | IDSTH                 | V <sub>DSTH</sub> > 0.8 V                                                                                                           | 40                         | -                  | 100                        | μA    |

| Short-to-Ground Threshold             | V <sub>STG(th)</sub>  | With a high–side driver on, as V <sub>SX</sub> decreases,<br>V <sub>DRAIN</sub> – V <sub>SX</sub> > V <sub>STG</sub> causes a fault | V <sub>DSTH</sub> –<br>0.3 | -                  | V <sub>DSTH</sub> +<br>0.2 | V     |

| Short-to-Battery Threshold            | V <sub>STB(th)</sub>  | With a low–side driver on, as V <sub>SX</sub> increases,<br>V <sub>Sx</sub> – V <sub>LSS</sub> > V <sub>STB</sub> causes a fault    | V <sub>DSTH</sub> –<br>0.3 | -                  | V <sub>DSTH</sub> +<br>0.2 | V     |

| VDRAIN-Open Bridge Operating Range    | V <sub>DRAIN</sub>    | 7 V < V <sub>BAT</sub> < 40 V                                                                                                       | -0.3                       | -                  | V <sub>BAT</sub> + 2.0     | V     |

| VDRAIN_Open Bridge Current            | I <sub>VDRAIN</sub>   | 7 V < V <sub>BAT</sub> < 40 V                                                                                                       | 0                          | -                  | 1.0                        | mA    |

| VDRAIN /Open Bridge Threshold Voltage | V <sub>BDGO(th)</sub> | If V <sub>DRAIN</sub> < V <sub>BDGOTH</sub> then a bridge fault occurs                                                              | 1.0                        | -                  | 3.0                        | V     |

| Thermal Shut Down Temperature         | TJ                    |                                                                                                                                     | 160                        | 170                | 180                        | °C    |

| Thermal Shutdown Hysteresis           | $\Delta T_{J}$        |                                                                                                                                     | 7.0                        | 10                 | 13                         | °C    |

<sup>1</sup>Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions. Performance may vary for individual units, within the specified maximum and minimum limits.

<sup>2</sup>Negative current is defined as coming out of (sourcing) the specified device terminal.

<sup>3</sup>For  $V_{BOOSTM} < V_{BOOST} < 40$  V power dissipation in the  $V_{REG}$  LDO increases. Observe T<sub>J</sub> < 150°C limit.

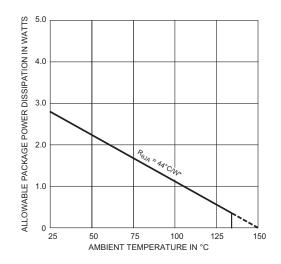

## **Thermal Characteristics**

| Characteristic             | Symbol           | Test Conditions*                        | Value | Units |

|----------------------------|------------------|-----------------------------------------|-------|-------|

| Package Thermal Resistance | R <sub>θJA</sub> | On 4-layer PCB, based on JEDEC standard | 44    | °C/W  |

\*Additional thermal information available on Allegro Web site.

### Power Dissipation versus Ambient Temperature

## **Terminal Descriptions**

**AHI, BHI, and CHI.** Direct control of high-side gate outputs GHA, GHB, and GHC. Logic 1 drives the gate on. Logic 0 pulls the gate down, turning off the external power MOSFET. Internally pulled down when the terminal is open.

**ALO, BLO, and CLO.** Direct control of low-side gate outputs GHA, GHB, and GHC. Logic 1 drives the gate on. Logic 0 pulls the gate down, turning off the external power MOSFET. Internally pulled down when the terminal is open.

**BOOSTD.** Boost converter switch drain connection.

**BOOSTS.** Boost converter switch source connection.

**CA, CB, and CC.** High-side connection for the bootstrap capacitors, CBOOT*x*, positive supply for high-side gate drive. The bootstrap capacitor is charged to  $V_{REG}$  when the output S*x* terminal is low. When the output swings high, the voltage on this terminal rises with the output to provide the boosted gate voltage needed for N-channel power MOSFETs.

**CSN.** Input for current-sense differential amplifier, on the inverting, negative side. Kelvin connection for the ground side of the current-sense resistor, RSENSE.

**CSOUT.** Amplifier output voltage proportional to the current sensed across an external low-value resistor placed in the ground side of the power MOSFET bridge.

**CSP.** Input for current-sense differential amplifier, on the noninverting, positive side. Connected to the positive side of the sense resistor, RSENSE.

**ENABLE.** Logic 0 disables the gate control signals and switches off all the gate drivers (low) causing a coast condition. Can be used in conjunction with the gate inputs to PWM (pulse wave modulate) the load current. Internally pulled down when the terminal is open.

**FAULT.** Diagnostic logic output signal. When low, indicates that one or more fault conditions have occurred.

**GHA, GHB, and GHC.** High-side gate drive outputs for N-channel MOSFET drivers. External series gate resistors can control the slew rate seen at the power driver gate, thereby controlling the di/dt and dv/dt of Sx outputs.

**GLA, GLB, and GLC.** Low-side gate drive outputs for external, N-channel MOSFET drivers. External series gate resistors can control slew rate.

GND. Ground, or negative, side of VDD and VBAT supplies.

**LSS.** Low-side gate driver return. Connects to the common sources on the low sides of the power MOSFET bridge.

**OVFLT.** Logic 1 indicates that the  $V_{BAT}$  level exceeded the VBAT overvoltage trip point set by the OVSET level. It will recover after exceeding a hysteresis below that maximum value. Normally, it has a high-impedance state. If OVFLT and UVFLT are both in high-impedance state; then, at least, a thermal shutdown or VDD undervoltage has occurred.

**OVSET.** A positive dc level that controls the VBAT overvoltage trip point. Usually, set by a precision resistor divider network between VDD and GND, but can be held grounded for a preset value. When this terminal is open, it sets an unspecified but high overvoltage trip point.

**SA**, **SB**, **and SC**. Directly connected to the motor terminals, these terminals sense the voltages switched across the load and are connected to the negative side of the bootstrap capacitors, CBOOT*x*. Also, are the negative supply connection for the floating high-side drivers.

**UVFLT.** Logic 1 indicates that the  $V_{BAT}$  level is below its minimum value. It will recover after exceeding a hysteresis above that minimum value. Has a high-impedance state. If UVFLT and OVFLT are both in high-impedance state; then, at least, a thermal shutdown or VDD undervoltage has occurred.

**VBAT.** Battery voltage. Positive input. usually connected to the motor voltage supply.

**VBOOST.** Boost converter output, 16 V nominal, is also the input to the regulator for VREG. Has internal boost-current and boost-voltage control loops. In high-voltage systems is approximately one diode drop below  $V_{BAT}$ .

VDD. Logic supply, +5 V nominal.

**VDRAIN.** Kelvin connection for drain-to-source voltage monitor. Connected to the high-side drains of the MOSFET bridge. High impedance when this terminal is open, and registers as a short-toground fault on all motor phases.

**VDSTH.** A positive dc level that sets the drain-to-source monitor threshold voltage. Internally pulled down when this terminal is open.

**VREG.** High-side gate driver supply, 13.5 V nominal. Has low-voltage dropout (LDO) feature.

## **Functional Description**

**Motor Lead Protection.** A fault detection circuit monitors the voltage across the drain-to-source of the external MOSFETs. A fault is asserted low on the output terminal, FAULT, if the drain-to-source voltage of any MOSFET that is instructed to turn on is greater than the voltage applied to the  $V_{DSTH}$  input terminal. When a high-side switch is turned on, the voltage from  $V_{DRAIN}$  to the appropriate motor phase output,  $V_{SX}$ , is examined. If the motor lead is shorted to ground before the high-side is turned on, the measured voltage will exceed the threshold and the FAULT terminal will go low. Similarly, when a low-side MOSFET is turned on, the differential voltage between the motor phase (drain) and the LSS terminal (source) is monitored.  $V_{DSTH}$ is set by a resistor divider to  $V_{DD}$ .

The V<sub>DRAIN</sub> is intended to be a Kelvin connection for the high-side, drain-to-source monitor circuit. Voltage drops across the power bus are eliminated by connecting an isolated PCB trace from the V<sub>DRAIN</sub> terminal to the drain of the MOSFET bridge. This allows improved accuracy in setting the V<sub>DSTH</sub> threshold voltage. The low-side, drain-to-source monitor uses the LSS terminal, rather than V<sub>DRAIN</sub>, for comparison with V<sub>DSTH</sub>. The A3935 just reports these motor faults.

**Fault Outputs.** Transient faults on any of the fault outputs are to be expected during switching, and will not disable the gate drive outputs. External circuitry or controller logic must determine if the faults represent a hazardous condition. **FAULT.** This terminal will go active low when any of the following conditions occur:

- V<sub>BAT</sub> overvoltage

- Motor lead short-to-supply or short-to-battery

- $V_{BAT}$  undervoltage

- Bridge (or V<sub>DRAIN</sub>) open

- V<sub>REG</sub> undervoltage

- V<sub>DD</sub> undervoltage

- Motor lead short-to-ground

Thermal shut down

**OVFLT.** Asserts high when a  $V_{BAT}$  overvoltage fault occurs and resets low after a recovery hysteresis. It has a high-impedance state when a thermal shutdown or  $V_{DD}$  undervoltage occurs. The voltage at the OVSET terminal,  $V_{OVSET}$ , controls the  $V_{BAT}$  overvoltage set point  $V_{BAT(ov)}$ , as follows:

$V_{\text{BAT(ov)}} = (A_{\text{BAT(ov)}} \times V_{\text{SET(ov)}}) + V_{\text{BAT(ov)}(0)},$ where  $A_{\text{BAT(ov)}}$  is the gain (12) and  $V_{\text{BAT(ov)}(0)}$  is the value of  $V_{\text{BAT(ov)}}$  when  $V_{\text{SET(ov)}} = 0$  ( $V_{\text{BAT(ov)}} \approx 22.4$ ). For the above formula to be valid, all variables must be in range and below the maximum operating specification.

**UVFLT.** Asserts high when a  $V_{BAT}$  undervoltage fault occurs and resets low after exceeding a recovery hysteresis. It has a high-impedance state when a thermal shut down or  $V_{DD}$  undervoltage occurs. OVFLT and UVFLT are mutually exclusive by definition.

**Current Sensing.** A current-sense amplifier is provided to allow system monitoring of the load current. The differential amplifier inputs are intended to be Kelvin-connected across a low-value sense resistor or current shunt. The output voltage is represented by:

$V_{\text{CSOUT}} = (I_{\text{LOAD}} \times A_{\text{V}} \times R_{\text{SENSE}}) + V_{\text{OS}}$ where  $V_{\text{OS}}$  is the output voltage calibrated at zero load current and  $A_{\text{V}}$  is the differential amplifier gain of about 19.2. If either the CSP or CSN pin is open, the CSOUT pin will go to its maximum positive level.

**Shut Down.** If a fault occurs because of excessive junction temperature or undervoltage on  $V_{DD}$  or  $V_{BAT}$ , all gate driver outputs are driven low until the fault condition is removed. In addition, the boost supply switch and VREG are turned off until those undervoltages and junction temperatures recover.

**Boost Supply.**  $V_{BOOST}$  is controlled by an inner currentcontrol loop, and by an outer voltage-feedback loop. The current-control loop turns off the boost switch for 5 µs whenever the voltage across the boost current-sense resistor exceeds 500 mV. A diode reverse-recovery current flows through the sense resistor whenever the boost switch turns on, which could result in turning off the switch again if not for the blanking-time circuit. Adjustment of this external sense resistor determines the maximum current in the inductor. Whenever  $V_{BOOST}$  exceeds the predefined threshold, 16 V nominal the boost switch is inhibited.

#### Input Logic Table

|        | Input      |            | Out | put | Mode of Operation                    |

|--------|------------|------------|-----|-----|--------------------------------------|

| ENABLE | хLО        | хНI        | GLx | GHx |                                      |

| 0      | Don't Care | Don't Care | 0   | 0   | All gate drive outputs low           |

| 1      | 0          | 0          | 0   | 0   | Both gate drive outputs low          |

| 1      | 0          | 1          | 0   | 1   | High-side on                         |

| 1      | 1          | 0          | 1   | 0   | Low-side on                          |

| 1      | 1          | 1          | 0   | 0   | XOR circuitry prevents shoot-through |

#### Fault Response Table

| Operating Condit               | Fa             | ault Outp | ut     | Regulator State |                  | Driver Output    |     |     |

|--------------------------------|----------------|-----------|--------|-----------------|------------------|------------------|-----|-----|

| Fault Mode                     | ENABLE         | FAULT     | OVFLT  | UVFLT           | Boost            | V <sub>REG</sub> | GHx | GLx |

| No Fault                       | Don't Care     | 1         | 0      | 0               | ON               | ON               | а   | а   |

| Short-to-Battery               | 1 <sup>b</sup> | 0         | 0      | 0               | ON               | ON               | а   | а   |

| Short-to-Ground                | 1 <sup>c</sup> | 0         | 0      | 0               | ON               | ON               | а   | а   |

| Bridge (VDRAIN) Fault          | 1 <sup>d</sup> | 0         | 0      | 0               | ON               | ON               | а   | а   |

| VREG Undervoltage              | Don't Care     | 0         | 0      | 0               | ON               | ON               | а   | а   |

| VBAT Overvoltage               | Don't Care     | 0         | 1      | 0               | OFF <sup>e</sup> | ON               | а   | а   |

| VBAT Undervoltage <sup>f</sup> | Don't Care     | 0         | 0      | 1               | OFF              | OFF              | 0   | 0   |

| VDD Undervoltage <sup>f</sup>  | Don't Care     | 0         | High Z | High Z          | OFF              | OFF              | 0   | 0   |

| Thermal Shut Down <sup>f</sup> | Don't Care     | 0         | High Z | High Z          | OFF              | OFF              | 0   | 0   |

<sup>a</sup>Determined by input states: *x*LO, *x*HI, and ENABLE. See Input Logic table.

<sup>b</sup>Short-to-battery can only be detected when the corresponding GLx = 1. This fault is not detected when ENABLE = 0. <sup>c</sup>Short-to-ground can only be detected when the corresponding GHx = 1. This fault is not detected when ENABLE = 0. <sup>d</sup>Bridge fault appears as a short-to-ground fault on all motor phases. This fault is not detected when ENABLE = 0. <sup>e</sup>Off only because  $V_{BOOST} \approx V_{BAT}$ , which is above the voltage threshold of the Boost regulator voltage control loop. <sup>f</sup>These faults are not only reported, but also action is taken by the internal logic to protect the A3935 and the system.

# A3935

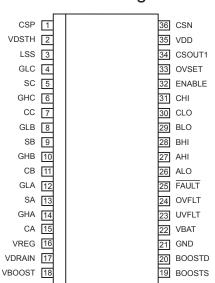

### Pin-out Diagram

## **Terminal List**

| Number | Name   | Function                                            | Number | Name   | Function                                         |

|--------|--------|-----------------------------------------------------|--------|--------|--------------------------------------------------|

| 1      | CSP    | Current-sense input, positive-side                  | 19     | BOOSTS | Boost switch, source                             |

| 2      | VDSTH  | DC input, drain-to-source monitor threshold voltage | 20     | BOOSTD | Boost switch, drain                              |

| 3      | LSS    | Gate-drive source return, low-side                  | 21     | GND    | Ground, dc supply returns, negative              |

| 4      | GLC    | Gate-drive C output, low-side                       | 22     | VBAT   | Battery supply, positive                         |

| 5      | SC     | Load phase C input                                  | 23     | UVFLT  | VBAT undervoltage fault output                   |

| 6      | GHC    | Gate-drive C output, high-side                      | 24     | OVFLT  | VBAT overvoltage fault output                    |

| 7      | CC     | Bootstrap capacitor C                               | 25     | FAULT  | Active-low fault output, primary                 |

| 8      | GLB    | Gate-drive B output, low-side                       | 26     | ALO    | Gate control input A, low-side                   |

| 9      | SB     | Load phase B input                                  | 27     | AHI    | Gate control input A, high-side                  |

| 10     | GHB    | Gate-drive B output, high-side                      | 28     | BHI    | Gate control input B, high-side                  |

| 11     | СВ     | Bootstrap capacitor B                               | 29     | BLO    | Gate control input B, low-side                   |

| 12     | GLA    | Gate-drive A output, low-side                       | 30     | CLO    | Gate control input C, low-side                   |

| 13     | SA     | Load phase A input                                  | 31     | СНІ    | Gate control input C, high-side                  |

| 14     | GHA    | Gate-drive A output, high-side                      | 32     | ENABLE | Gate output enable                               |

| 15     | CA     | Bootstrap capacitor A                               | 33     | OVSET  | DC input, overvoltage threshold setting for VBAT |

| 16     | VREG   | Gate drive supply, positive                         | 34     | CSOUT  | Current-sense amplifier output                   |

| 17     | VDRAIN | Kelvin connection to MOSFET high-side drains        | 35     | VDD    | Logic supply, nominally +5 V                     |

| 18     | VBOOST | Boost supply output                                 | 36     | CSN    | Current-sense input, negative-side               |

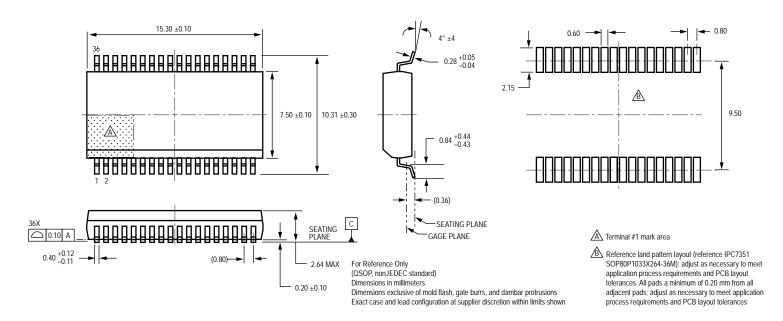

# Package LQ, 36-pin QSOP

Copyright ©2005-2008, Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com