Datasheet

Revision 1.1

# Digital Automotive Pixel Link Transmitter

The INAP125T12/24 is a transmitter for the new Automotive PIXel (APIX) link for display and camera based point-to-point applications. The APIX link features an uni-directional pixel and full-duplex sideband data transmission over one single pair of shielded twisted pair (STP) copper cable. The upstream sideband can also be transmitted over a separate pair of wires to serve the requirements for automotive applications. In addition this wire may be used for power supply.

The INAP125T12 video interface supports color widths of 10 and 12bit, the INAP125T24 widths of 10, 12, 18 and 24bit. The interface can be configured individually to match all popular display and image sensor interfaces. The pixel interface is able to handle a wide spread pixel clock for lowest EMI.

The INAP125T12/24 transmitter features dedicated high-speed outputs with adjustable drive current and pre-emphasis to facilitate the adaptation to different link distances and cable qualities while offering maximum data integrity and full EMI compliance.

#### Packages:

- 48 pin QFN (Quad-Flat No-Leads)

- 64 pin QFN

# INAP125T12 INAP125T24

#### Features:

- Up to 1 GBit/s Downstream Link

- Up to 62.5 MBit/s Upstream Link

- Low EMI, Two- or Four-Wire Full Duplex Link

- Accepts wide spread spectrum pixel clock

- +15 m Distance with low profile STP cables

- 10/12/18/24 bit pixel Interface

- Configurable sampling edge for pixel data

- DC-balanced line coding to support AC coupling

- Line Driver Current and Pre-Emphasis adjustable

- Extended Temp. Range: -40 to +105°C

- AEC-Q100

#### **Applications:**

- Automotive Infotainment Displays

- · Automotive Dashboard Displays

- · Head-Up Displays

- Rear-Seat Entertainment Systems

- Automotive Driver Assistance

- Surveillance Systems

- Machine Vision

- Inspection Systems

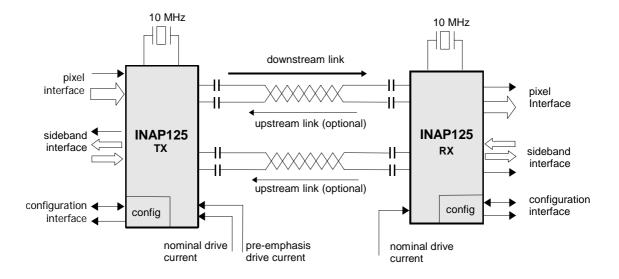

Figure 1: APIX system overview

#### 1.0 Introduction

The APIX link transmits uncompressed pixel data with a sustained and resolution-independent link data rate of either 1 GBit/s or 500 MBit/s over one single pair of STP copper cable. In addition to the pixel data, bidirectional sideband control data can be transmitted over the same pair of wires.

The link supports distances of up to +15m (1 GBit/s mode) and up to +40m (500 MBit/s mode) depending on the output settings (current, pre-emphasis) and the cable properties.

Optimized for low EMI, the APIX link is dedicated for point-to-point applications within vehicles. The highly integrated architecture allows the implementation of video and audio links in applications like central information displays, dashboard and head-up displays, but also camera links as part of driver assistance systems requiring real-time digital video streams.

#### 1.1 Transmission Channels

The APIX link provides three independent channels for data transfer

- · the high speed downstream pixel channel

- the downstream sideband channel

- the upstream sideband channel

The pixel channel and the downstream sideband channel are multiplexed and commonly transmitted over the downstream link.

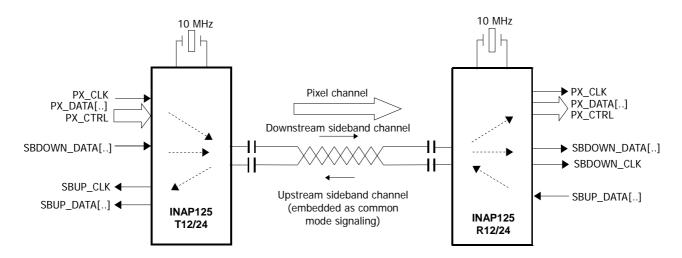

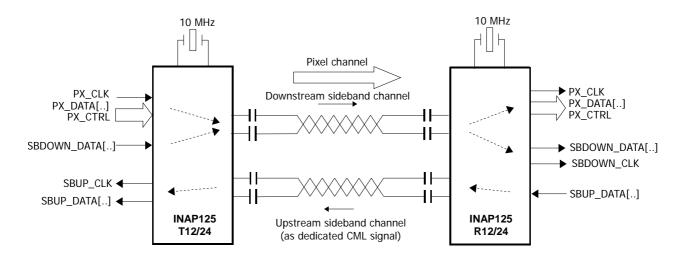

The upstream sideband channel can either be established over the same pair of wires as the downstream link (embedded return channel) or alternatively over a separate pair of wires. The configuration needs to be performed by the configuration vectors (see section 3.1).

Figure 1-1: Single wire transmission channel configuration

Figure 1-2: Two wire transmission channel configuration

#### 1.2 Link Bandwidth

The bandwidth of the downstream link can be selected from these two modes:

- "full bandwidth" mode with a link data rate of 1 GBit/s, providing a net video datarate of 847MBit/s

- "half bandwidth" mode with a link data rate of 500 MBit/s, providing a net video datarate of 423.6MBit/s

The bandwidth also defines the maximum datarate possible for the sideband channels. The downstream sideband channel is transmitted in dedicated slots in the downstream link and therefore offers guaranteed low latency real-time characteristics. The maximum transmission rates is defined by the sampling frequency of the input pins as defined in section 2.3.2.

The upstream sideband channel is transmitted either as common mode signal on the same or as differential signal on a separate line (see Figure 1-2). The upstream channel datarate is configurable by configuration vectors as defined in section 3.1 and is not affected by the signalling method chosen for the upstream sideband channel.

### 2.0 Functional Description

#### 2.1 Block Diagram

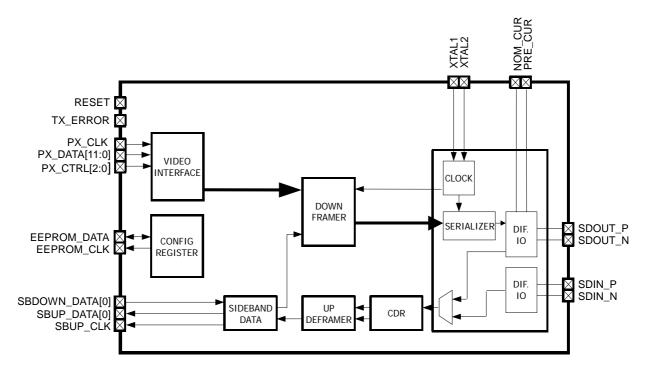

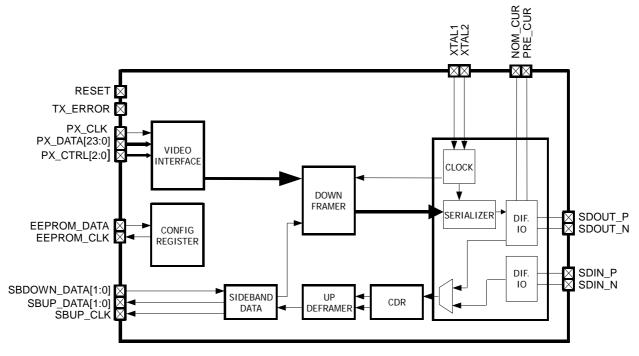

Figure 2-1: INAP125T12 Block Diagram

Figure 2-2: INAP125T24 Block Diagram

#### 2.2 Serial Link Interfaces

#### 2.2.1 Downstream Link Interface

The interface (SDOUT+, SDOUT-) of the downstream serial link (Tx -> Rx) is implemented with differential Current Mode Logic (CML).

#### 2.2.2 Upstream Link Interface

As the upstream serial channel (from Rx to Tx) can alternatively be established over the downlink (embedded back channel) or a separate pair of STP cable, different signalling techniques will be employed.

**Option 1:** Upstream and downstream channels share the same pair of STP cable. The upstream link employs common mode signalling technique.

**Option 2:** Upstream and downstream channels are transmitted over 2 separate pairs of STP cable. The additional upstream interface of the APIX devices (SDIN+, SDIN-) is realized with differential Current Mode Logic (CML).

#### 2.3 Digital Interfaces

#### 2.3.1 Pixel Data Interface

The pixel data interface is the input for the 24 bit parallel pixel data representing the video data. In addition 3 pixel control signals like HSYNC, VSYNC and DATA ENABLE can be transmitted. The interface needs to be driven by an external pixel clock at PX\_CLK, which acts as synchronous clock for the interface. The pixel clock is limited to 62 Mhz as specified in Table 7-6. Data width and the configuration for the pixel control data are defined by configuration vectors (see section 3.1).

| Channels       |               | control signal transmit mode configuration of transmission of pixel control signal |                  |            |  |

|----------------|---------------|------------------------------------------------------------------------------------|------------------|------------|--|

| Downstream     | PX_DATA Width | never                                                                              | even pixels only | each pixel |  |

| Bandwidth mode | 10 bit        | 62.0 MHz                                                                           | 62.0 MHz         | 62.0 MHz   |  |

| 1GBit/s        | 12 bit        | 62.0 MHz                                                                           | 62.0 MHz         | 56.4 MHz   |  |

|                | 18 bit        | 47.0 MHz                                                                           | 43.4 MHz         | 40.3 MHz   |  |

|                | 24 bit        | 35.3 MHz                                                                           | 33.2 MHz         | 31.3 MHz   |  |

| Bandwidth mode | 10 bit        | 42.3 MHz                                                                           | 36.8 MHz         | 32.5 MHz   |  |

| 500MBit/s      | 12 bit        | 35.2 MHz                                                                           | 31.3 MHz         | 28.2 MHz   |  |

|                | 18 bit        | 23.5 MHz                                                                           | 21.7 MHz         | 20.1 MHz   |  |

|                | 24 bit        | 17.6 MHz                                                                           | 16.6 MHz         | 15.6 MHz   |  |

Table 2-1: Maximum pixel clock frequency for different PX\_CTRL and data width settings

The parallel pixel interface supports pixel formats of 10, 12, 18 and 24 bit + 3 control signals. Pixel data and control signals are sampled with the pixel clock. The active edge can be configured to either rising or falling.

It is recommended to consider series resistors for all PX\_DATA, PX\_CTRL and PX\_CLK input pins close to the video source device to reduce the risk of data-related emissions and reflections.

| Color Depth | INAP125T12 <sup>a</sup> | INAP125T24    |

|-------------|-------------------------|---------------|

| 10 Bit      | PX_DATA[9:0]            | PX_DATA[9:0]  |

| 12 Bit      | PX_DATA[11:0]           | PX_DATA[11:0] |

| 18 Bit      | -                       | PX_DATA[17:0] |

| 24 Bit      | -                       | PX_DATA[23:0] |

Table 2-2: Pixel data interface options

a. 18 and 24 bit configurations also possible for INAP125T12 devices, most significant bits PX\_DATA[23:12] internally pulled high.

| Control Function    | INAP125T12 | INAP125T24 |

|---------------------|------------|------------|

| HSYNC / lineSync    | PX_CTRL[0] | PX_CTRL[0] |

| VSYNC / frameSync   | PX_CTRL[1] | PX_CTRL[1] |

| DATA ENABLE / valid | PX_CTRL[2] | PX_CTRL[2] |

Table 2-3: Pixel control interface

Please note that PX\_CTRL[2] is required by the APIX link to synchronize the serial transmission to the pixel data. Therefore it is mandatory to toggle the pin at least once at the beginning of the transmission to ensure the correct operation of the APIX link.

#### 2.3.2 Sideband Channel Downstream Interface

The sideband data downstream interface provides either one (INAP125T12) or two (INAP125T24) input pins to sample sideband data. Both pins are sampled at a specific frequency and transmitted as 2 bit data packet. The sampling frequency depends on the bandwidth mode selected for the downstream link as shown in Table 2-4.

| Downstream | Sampling  | Inpu           | ıt pins          |

|------------|-----------|----------------|------------------|

| speed      | frequency | INAP125T12     | INAP125T24       |

| 1 GBit/s   | 13.89 MHz | SBDOWN DATA[0] | SBDOWN DATA[1:0] |

| 500 MBit/s | 6.94 MHz  | 3BDOWN_DATA[0] | SBDOWN_DATA[1.0] |

Table 2-4: Downstream Sideband channel sampling frequency

#### 2.3.3 Sideband Channel Upstream Interface

The sideband data upstream interface provides the sideband data at either one (INAP125T12) or two (INAP125T24) output pins. The pins are provided synchronously to SBUP\_CLK, which reflects the upstream sample clock at the INAP125R12/24 receiver devices. The maximum datarate is limited by the upstream serial line clock, which is defined by a configuration vector (see Table 3-1). Please see Table 2-5 for a complete list of available data rates.

| Upstream Serial | Maximum Output     | Output pins   |                |  |

|-----------------|--------------------|---------------|----------------|--|

| Line Clock      | Datarate (per pin) | INAP125T12    | INAP125T24     |  |

| 62.5 MHz        | <10.40 MBit/s      |               |                |  |

| 41.61 MHz       | <6.94 MBit/s       | CDLID DATAIOI | CDUD DATAMA    |  |

| 31.25 MHz       | <5.20 MBit/s       | SBUP_DATA[0]  | SBUP_DATA[1:0] |  |

| 20.83 MHz       | <3.48 MBit/s       |               |                |  |

Table 2-5: Upstream sideband channel datarate with INAP125R12/24 receiver

#### 2.4 Signal Description

Note: Unused CMOS inputs should be tied to GND

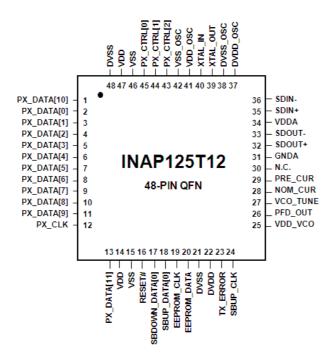

| Signal Name    | Pin#                               | Туре   | Description                                                                                                                      |

|----------------|------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| PX_DATA[11:0]  | 13,1,11,<br>10,9,8,7,6,<br>5,4,3,2 | IN     | Pixel data input, sampled with respect to the rising or falling edge of PX_CLK. Inputs should be connected via series resistors. |

| PX_CLK         | 12                                 | IN     | Pixel clock input                                                                                                                |

| PX_CTRL[2:0]   | 43,44,45                           | IN     | Pixel control signals                                                                                                            |

| SBDOWN_DATA[0] | 17                                 | IN     | Downstream sideband data                                                                                                         |

| SBUP_DATA[0]   | 18                                 | OUT    | Upstream sideband data                                                                                                           |

| SBUP_CLK       | 24                                 | OUT    | Sideband channel upstream clock                                                                                                  |

| RESET#         | 16                                 | IN     | Asynchronous reset (active low)                                                                                                  |

| TX_ERROR       | 23                                 | OUT    | Upstream Link Sync Error Indicator (active high)                                                                                 |

| EEPROM_DATA    | 20                                 | IN/OUT | Configuration data                                                                                                               |

| EEPROM_CLK     | 19                                 | OUT    | Configuration clock                                                                                                              |

| XTAL_IN        | 40                                 | IN     | Oscillator input or reference clock input                                                                                        |

| XTAL_OUT       | 39                                 | OUT    | Oscillator output                                                                                                                |

| NOM_CUR        | 28                                 | PASSIV | Serial Downstream: Nominal current control                                                                                       |

| PRE_CUR        | 29                                 | PASSIV | Serial Downstream: Pre-emphasis current control                                                                                  |

Table 2-6: INAP125T12 Pinout description, 48-pin QFN

| Signal Name           | Pin#   | Туре | Description                                                                  |

|-----------------------|--------|------|------------------------------------------------------------------------------|

| SDOUT+                | 32     | OUT  | CML serial data interface downstream. Interface                              |

| SDOUT-                | 33     | OUT  | to differential transmission line with Zdiff = 100 Ohm.                      |

| SDIN+                 | 35     | IN   | CML serial data interface upstream. Interface to                             |

| SDIN-                 | 36     | IN   | differential transmission line with Zdiff = 100 Ohm. Leave open if not used. |

| VCO_TUNE              | 27     | IN   | VCO loop filter tuning voltage                                               |

| PFD_OUT               | 26     | OUT  | Current output for VCO loop filter                                           |

| VDD                   | 14, 47 | PWR  | 1.8 V core supply                                                            |

| DVDD                  | 22     | PWR  | 3.3 V I/O supply                                                             |

| VDD_VCO               | 25     | PWR  | Regulated power supply for VCO 1.8 V, 7 mA                                   |

| VDDA                  | 34     | PWR  | 1.8 V analog supply                                                          |

| VDD_OSC               | 41     | PWR  | 1.8 V oscillator supply                                                      |

| DVDD_OSC              | 37     | PWR  | 3.3 V oscillator supply                                                      |

| VSS <sup>a</sup>      | 15, 46 | GND  | Digital core ground                                                          |

| DVSS <sup>a</sup>     | 21,48  | GND  | Digital I/O ground                                                           |

| GNDA <sup>a</sup>     | 31     | GND  | Analog ground                                                                |

| VSS_OSC <sup>a</sup>  | 42     | GND  | Oscillator ground                                                            |

| DVSS_OSC <sup>a</sup> | 38     | GND  | Oscillator I/O ground                                                        |

| NC                    | 30     |      | not connected                                                                |

Table 2-6: INAP125T12 Pinout description, 48-pin QFN

a. All VSS, DVSS and GND pins should be connected as common ground

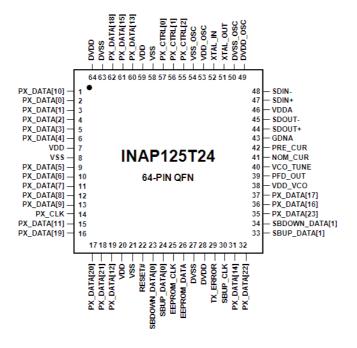

| Signal Name      | Pin#                                                                                 | Туре | Description                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------|

| PX_DATA[23:0]    | 35,32,18,17<br>,16,62,37,<br>36,61,31,60<br>,19,15,1,13,<br>12,11,10,9,<br>6,5,4,3,2 | IN   | Pixel data input, sampled with respect to the rising or falling edge of PX_CLK. Inputs should be connected via series resistors. |

| PX_CLK           | 14                                                                                   | IN   | Pixel clock input                                                                                                                |

| PX_CTRL[2:0]     | 55,56,57                                                                             | IN   | Pixel control signals                                                                                                            |

| SBDOWN_DATA[1:0] | 34,23                                                                                | IN   | Downstream sideband data                                                                                                         |

| SBUP_DATA[1:0]   | 33,24                                                                                | OUT  | Upstream sideband data                                                                                                           |

Table 2-7: INAP125T24 Pin description, 64-pin QFN

| Signal Name           | Pin #   | Туре   | Description                                             |

|-----------------------|---------|--------|---------------------------------------------------------|

| SBUP_CLK              | 30      | OUT    | Sideband channel upstream clock                         |

| RESET#                | 22      | IN     | Asynchronous reset (active low)                         |

| TX_ERROR              | 29      | OUT    | Upstream Link Sync Error Indicator (active high)        |

| EEPROM_DATA           | 26      | IN/OUT | Configuration data                                      |

| EEPROM_CLK            | 25      | OUT    | Configuration clock                                     |

| XTAL_IN               | 52      | IN     | Oscillator input or reference clock input               |

| XTAL_OUT              | 51      | OUT    | Oscillator output                                       |

| NOM_CUR               | 41      | PASSIV | Serial Downstream: Nominal current control              |

| PRE_CUR               | 42      | PASSIV | Serial Downstream: Pre-emphasis current control         |

| SDOUT+                | 44      | OUT    | CML serial data interface downstream. Interface         |

| SDOUT-                | 45      | OUT    | to differential transmission line with Zdiff = 100 Ohm. |

| SDIN+                 | 47      | IN     | CML serial data interface upstream. Interface to        |

| SDIN-                 | 48      | IN     | differential transmission line with Zdiff = 100 Ohm.    |

| VCO_TUNE              | 40      | IN     | VCO loop filter tuning voltage                          |

| PFD_OUT               | 39      | OUT    | Current output for VCO loop filter                      |

| VDD_VCO               | 38      | PWR    | Regulated power supply for VCO 1.8 V, 7 mA              |

| VDD                   | 7,20,59 | PWR    | 1.8 V core supply                                       |

| DVDD                  | 28,64   | PWR    | 3.3 V I/O supply                                        |

| VDDA                  | 46      | PWR    | 1.8 V analog supply                                     |

| VDD_OSC               | 53      | PWR    | 1.8 V oscillator supply                                 |

| DVDD_OSC              | 49      | PWR    | 3.3 V oscillator supply                                 |

| VSS <sup>a</sup>      | 8,21,58 | GND    | Digital core ground                                     |

| DVSS <sup>a</sup>     | 27,63   | GND    | Digital I/O ground                                      |

| GNDA <sup>a</sup>     | 43      | GND    | Analog ground                                           |

| VSS_OSC <sup>a</sup>  | 54      | GND    | Oscillator ground                                       |

| DVSS_OSC <sup>a</sup> | 50      | GND    | Oscillator I/O ground                                   |

Table 2-7: INAP125T24 Pin description, 64-pin QFN

a. All VSS, DVSS and GND pins should be connected as common ground

#### 3.0 Configuration, Reset, Power-Up and Error Detection

#### 3.1 Configuration

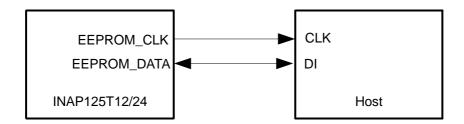

The device parameters and settings are configured through a two-wire serial interface which is compatible to the MicroChip MicroWire™ interface. After power-up or reset, the INAP125T12/24 expects a serial EEPROM at the interface EEPROM\_DATA and EEPROM\_CLK, to read in the configuration vectors. In case no EEPROM is used, the chip needs to be stimulated with the PROM\_start and PROM\_stop bytes as shown in Table 3-1. If the initialization fails the default values will be used. Please see section 3.1.2 for more details on the programming flow.

#### 3.1.1 Configuration vectors

| Address<br>byte | Bit# | Parameter                             | Recommended value | Default<br>value | Comment                                                                                                                 |

|-----------------|------|---------------------------------------|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|

| 00              | 7:0  | PROM_start                            | 10111101          |                  | PROM valid byte 0                                                                                                       |

| 01              | 2:0  | pre-emphasis control                  | 000               | 000              | regulates the delay until pre-emphasis gets active. 000 means pre-emphasis active with first bit. (recommended)         |

|                 | 3    | dedicated<br>upstream                 |                   | 0                | 0: enable dedicated upstream link 1: disable Note: in case bit 3 and 4 are set to '0', the upstream channel is disabled |

|                 | 4    | embedded<br>upstream                  |                   | 1                | 0: enable embedded upstream link 1: disable Note: in case bit 3 and 4 are set to '0', the upstream channel is disabled  |

|                 | 5    | reserved                              | 1                 | 1                | reserved                                                                                                                |

|                 | 6    | bandwidth<br>mode                     |                   | 0                | 0: 500 MBit/s mode<br>1: 1 GBit/s mode                                                                                  |

|                 | 7    | wait period<br>after<br>configuration | 1                 | 1                | 0: no delay 1: 50 ms delay after configuration to stabilize the PLL                                                     |

| 02              | 1:0  | pixel data<br>width <sup>a</sup>      |                   | 00               | selects the width of pixel data to be transmitted 00: 10 bit 01: 12 bit 10: 18 bit 11: 24 bit                           |

**Table 3-1: Configuration vectors**

| Address<br>byte | Bit# | Parameter                        | Recommended value | Default<br>value | Comment                                                                                                        |

|-----------------|------|----------------------------------|-------------------|------------------|----------------------------------------------------------------------------------------------------------------|

|                 | 3:2  | control signal<br>transmit mode  | 11                | 11               | transmission of pixel control signals 00: never 01: unused 10: on every second (even) pixels 11: on each pixel |

|                 | 4    | reserved                         | 1                 | 1                |                                                                                                                |

|                 | 5    | pixel clock<br>active edge       |                   | 1                | 0: falling edge<br>1: rising edge                                                                              |

|                 | 7:6  | upstream<br>serial link<br>clock |                   | 10               | See Table 3-2 and Table 3-3                                                                                    |

| 03              | 3:0  | upstream link<br>data recovery   |                   | 0001             | See Table 3-4                                                                                                  |

|                 | 4    | reserved                         | 0                 | 0                |                                                                                                                |

|                 | 7:5  | TX_Error config                  |                   | 000              | Configuration of TX_Error pin<br>See Table 3-5                                                                 |

| 04              | 0    | pll status                       | 0                 | 0                | loss of PLL synchronization resets device 0: enable 1: disable                                                 |

|                 | 4:1  | reserved                         | 1000              | 1000             |                                                                                                                |

|                 | 7:5  | reserved                         | 100               | 100              |                                                                                                                |

| 05              | 7:0  | PROM_end                         | 10011001          |                  | PROM valid byte 1                                                                                              |

**Table 3-1: Configuration vectors**

a. 18 and 24 bit configurations also possible for INAP125T12 devices, most significant bits PX\_DATA[23:12] internally pulled high.

| Bandwidth mode | Configuration<br>Byte 2, Bit 7:6 | Upstream serial line clock |

|----------------|----------------------------------|----------------------------|

| 1 Gbit/s       | 00                               | 62.5 MHz                   |

| 1 Gbit/s       | 01                               | 41.67 MHz                  |

| 1 Gbit/s       | 10                               | 31.25 MHz                  |

Table 3-2: Sideband upstream configuration for full bandwidth mode

| Bandwidth mode | Configuration<br>Byte 2, Bit 7:6 | Upstream serial line clock |

|----------------|----------------------------------|----------------------------|

| 500 MBit/s     | 00                               | 62.5 MHz                   |

| 500 MBit/s     | 10                               | 31.25 MHz                  |

| 500 MBit/s     | 11                               | 20.83 MHz                  |

Table 3-3: Sideband upstream configuration for half bandwidth mode

| Upstream serial line clock | Configuration<br>Byte 3, Bit 3:0 |

|----------------------------|----------------------------------|

| 62.5 MHz                   | 0011                             |

| 41.67 MHz                  | 0001                             |

| 31.25 MHz                  | 0001                             |

| 20.83 MHz                  | 0011                             |

Table 3-4: Upstream link data recovery configuration

| Status       | Configuration<br>Byte 3, Bit 7:5 | Comment                            |

|--------------|----------------------------------|------------------------------------|

| SBUP_Error   | 000                              | Loss of upstream synchronization   |

| SBUP_Restart | 001                              | Upstream synchronization restarted |

| (reserved)   | 010:111                          |                                    |

Table 3-5: TX Error pin configuration

#### 3.1.2 Configuration procedure

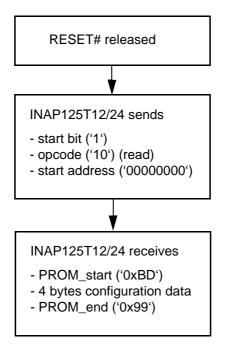

The configuration of the INAP125T12/24 is performed through the MicroWire<sup>TM</sup> compatible interface. In general, the configuration may be performed by connecting a standard EEPROM or by serving the data from a micro controller or FPGA. The INAP125T12/24 expects the configuration vector data in 8-bit data format. In case of invalid PROM\_start or PROM\_end bytes, the devices uses the default values.

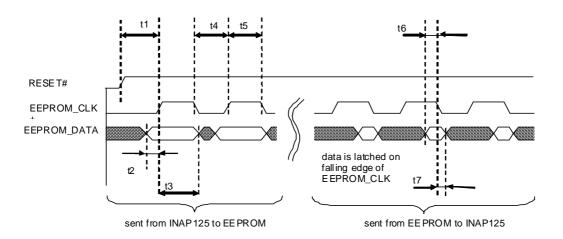

Please see Figure 3-1 for the general communication flow.

Figure 3-1: Configuration Flow

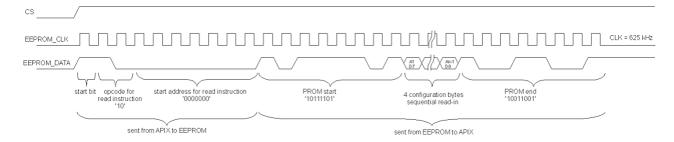

Figure 3-2: Configuration Interface Timing

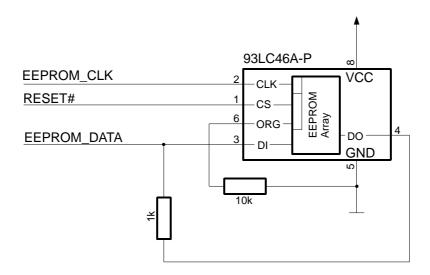

Recommended EEPROMs are the 93L46A or 93L46C from Microchip Technology Inc. with selected word size of 8 bit. Since the INAP125T12/24 does not provide a dedicated CS signal, the EEPROM needs to support to send all data on just one rising edge of CS as shown in Figure 3-2. Please see Figure 3-3 for a typical connection circuitry for the EEPROM.

Figure 3-3: EEPROM connection circuitry

In order to connect the INAP125T12/24 configuration interface to the host controller, the host needs to be able to accept the interface clock from the APIX device.

Please note: The INAP125T12/24 is only able to respond to the PROM\_Start and PROM\_End command. No other Microwire commands supported.

Figure 3-4: Host Connection diagram

#### 3.2 Reset

The Reset pin triggers an asynchronous reset (active low) which can be activated at any time and sets the INAP125T12/24 into a defined state. The minimum low pulse width is 4 reference clock cycles.

During reset the serial output pins SDOUT-, SDOUT+ are held on VDDA level. All parallel outputs pins are at low level. EEPROM\_DATA is set to Hi-Z.

#### 3.3 Power-Up

#### 3.3.1 Power-Up Sequence and Timing

The INAP125T12/24 power supplies do not require a specific power-up sequence. The device tolerates the supplies to be ramped simultaneously or in any order within the ramping time as defined in Table 3-6. Reset has to be held low until all supplies reached recommended operating conditions.

| Supply       | Ra   | mp-Up time |

|--------------|------|------------|

| Зирріу       | Min  | Max        |

| All supplies | 50µs | 10ms       |

Table 3-6: Power supply ramping requirements

#### 3.3.2 Power Supply Filtering

To achieve best transmission performance a noise level of less than 50mV on all analog and digital supply voltages VDD, VDDA, VDD\_OSC and DVDD is recommended. The loop filter supply VDD\_VCO requires lowest possible noise for best performance. See also section 6.0 for recommendations on power supply filtering.

#### 3.4 Error detection

The INAP125T12/24 device includes an automatic error detection, which, with upstream channel enabled, indicates an upstream link synchronization error on pin TX\_ERROR. The TX\_ERROR output can be configured to different options using configuration vectors as described in section 3.1.

### 4.0 Electrical Specification

#### **4.1 Interface Timing**

#### 4.1.1 Pixel Interface

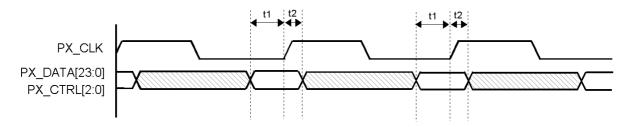

Figure 4-1: Pixel Interface timing at rising edge

| Parameter      | Description                                             | Min. | Тур. | Max. | Unit |

|----------------|---------------------------------------------------------|------|------|------|------|

| t <sub>1</sub> | Pixel data and control signal setup time to pixel clock | 1.5  | 2    | -    | ns   |

| t <sub>2</sub> | Pixel data and control signal hold time to pixel clock  | -    | 0    | 1    | ns   |

Table 4-1: Pixel interface timing at rising edge

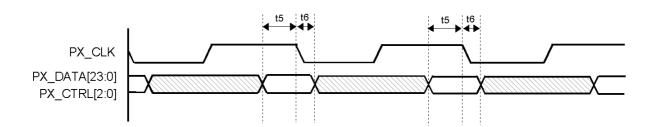

Figure 4-2: Pixel interface timing at falling edge

| Parameter      | Description                                             | Min. | Тур. | Max. | Unit |

|----------------|---------------------------------------------------------|------|------|------|------|

| t <sub>5</sub> | Pixel data and control signal setup time to pixel clock | 1.5  | 2    | -    | ns   |

| t <sub>6</sub> | Pixel data and control signal hold time to pixel clock  | ı    | 0    | 1    | ns   |

Table 4-2: Pixel interface timing at falling edge

#### 4.1.2 Sideband Interface Timing

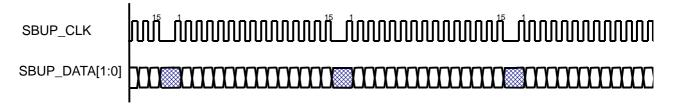

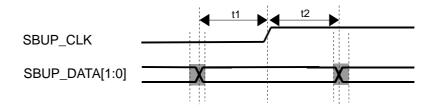

The upstream interface clock SBUP\_CLK provides the internal sampling clock used at the APIX receiver to sample the data at SBUP\_DATA[1:0]. In general the clock is defined as 1/3 of the upstream serial line clock as defined in Table 2-5. Due to the framing structure of the upstream link, the sideband clock is not available every 16<sup>th</sup> clock cycle as shown in Figure 4-3.

Figure 4-3: Upstream sideband interface

Figure 4-4: Upstream sideband Interface Timing

| Parameter      | Description                                | Min. | Тур. | Max. | Unit |

|----------------|--------------------------------------------|------|------|------|------|

| t <sub>1</sub> | Sideband data setup time to sideband clock | -    | 60   | -    | ns   |

| t <sub>2</sub> | Sideband data hold time to sideband clock  | -    | 60   | -    | ns   |

Table 4-3: Upstream sideband Interface Timing at 20.83Mhz upstream serial line clock

| Parameter      | Description                                | Min. | Тур. | Max. | Unit |

|----------------|--------------------------------------------|------|------|------|------|

| t <sub>1</sub> | Sideband data setup time to sideband clock | -    | 40   | -    | ns   |

| t <sub>2</sub> | Sideband data hold time to sideband clock  | -    | 40   | -    | ns   |

Table 4-4: Upstream Interface Timing at 31.25Mhz upstream serial line clock

| Parameter      | Description                                | Min. | Тур. | Max. | Unit |

|----------------|--------------------------------------------|------|------|------|------|

| t <sub>1</sub> | Sideband data setup time to sideband clock | -    | 30   | -    | ns   |

| t <sub>2</sub> | Sideband data hold time to sideband clock  | -    | 30   | -    | ns   |

Table 4-5: Upstream Interface Timing at 41.67Mhz upstream serial line clock

| Parameter      | Description                                | Min. | Тур. | Max. | Unit |

|----------------|--------------------------------------------|------|------|------|------|

| t <sub>1</sub> | Sideband data setup time to sideband clock | -    | 20   | -    | ns   |

| t <sub>2</sub> | Sideband data hold time to sideband clock  | -    | 20   | -    | ns   |

Table 4-6: Upstream Interface Timing at 62.5 Mhz upstream serial line clock

#### 4.1.3 Configuration interface timing

Figure 4-5: Configuration interface timing

| Parameter      | Description                          | Min.                            | Тур. | Max. | Unit |

|----------------|--------------------------------------|---------------------------------|------|------|------|

| t <sub>1</sub> | RESET high to first EEPROM clk       | 6xt <sub>OSC</sub> <sup>a</sup> | 650  | -    | ns   |

| t <sub>2</sub> | setup time EEPROM_DATA to EEPROM_CLK | -                               | 400  | -    | ns   |

| t <sub>3</sub> | hold time EEPROM_DATA to EEPROM_CLK  | -                               | 1200 | -    | ns   |

| t <sub>4</sub> | EEPROM_CLK low time                  | -                               | 800  | -    | ns   |

| t <sub>5</sub> | EEPROM_CLK high time                 | -                               | 800  | -    | ns   |

| t <sub>6</sub> | setup time EEPROM_DATA to EEPROM_CLK | -                               | 20   | -    | ns   |

| t <sub>7</sub> | hold time EEPROM_DATA to EEPROM_CLK  | -                               | 10   | -    | ns   |

**Table 4-7: Configuration interface timing**

a.  $t_{OSC}$  reflects one clock cycle as defined by the external reference clock, see section 5.2.4.

#### 5.0 External circuits

#### **5.1 External Termination Resistors**

There are no external termination resistors required – for both Upstream and Downstream the dedicated 50 Ohm termination resistors are integrated in the circuit.

#### **5.2 External Coupling Capacitors**

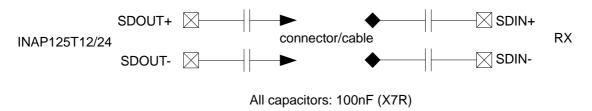

#### **5.2.1 Downstream Coupling Capacitors**

Figure 5-1: External coupling capacitors in downstream

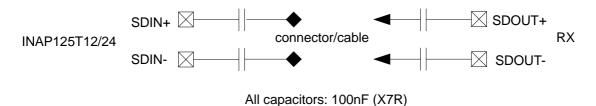

#### **5.2.2 Upstream Coupling Capacitors**

Figure 5-2: External coupling capacitors in upstream

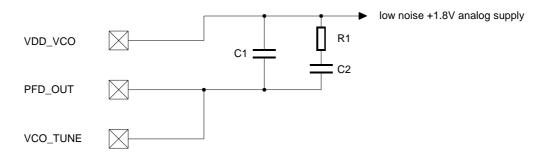

#### 5.2.3 External Loop Filter

The INAP125T12/24 PLL circuit for the core system requires and external loop filter which should be implemented as shown in Figure 5-3.

Figure 5-3: External loop filter circuit for the system clock VCO

| Symbol         | Description              | Value | Unit |

|----------------|--------------------------|-------|------|

| C <sub>1</sub> | Capacitor C <sub>1</sub> | 1.5   | nF   |

| $C_2$          | Capacitor C <sub>2</sub> | 10    | nF   |

| R <sub>1</sub> | Resistor R <sub>1</sub>  | 220   | kΩ   |

Table 5-1: Loop filter values for the system clock VCO

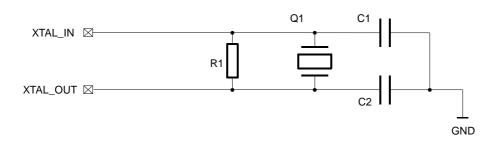

#### 5.2.4 External Reference Clock

The INAP125T12/24 core clock frequency is generated by an internal PLL controlled by an external 10 MHz crystal. Alternatively a stable 10 MHz clock signal (3.3V CMOS TTL) can be directly connected to XTAL\_IN with XTAL\_OUT left open. Figure 5-4 shows a typical crystal design required for the oscillator circuit. The values for C1, C2 and R1 need to be selected to match the oscillation requirements of the crystal Q1. Please see Table 5-2 for the external crystal.

Figure 5-4: Crystal clock schematic example

| Parameter                       | Symbol           | Min           | Тур | Max  | Unit |

|---------------------------------|------------------|---------------|-----|------|------|

| Nominal Frequency               | f <sub>OSC</sub> | -             | 10  | -    | MHz  |

| Frequency Tolerance             | F <sub>tol</sub> | -100          | -   | +100 | ppm  |

| Equivalent Series<br>Resistance | ESR              | -             | -   | 80   | Ohm  |

| Drive Level                     |                  | see Table 5-3 |     |      |      |

Table 5-2: Crystal requirements

For resonance at the correct frequency, the crystal needs to be loaded with its specified load capacitance  $C_L$ , which is the value of capacitance used in conjunction with the oscillation unit. The INAP125T12/24 oscillator provides some of the load with internal capacitance which is specified with in the range of 10pF to 12.5pF. The remainder is generated by the external capacitors and tuning capacitors labeled C1 and C2.

The load capacitance CL can be calculated from CL = Cint + C1//C2. E.g. selecting C1 and C2 with 15pF, CL can be calculated to CL = 12.5pF + 7.5pF = 20pF.

The crystal needs to be able to withstand the power dissipation, produced by the INAP125T12/24. The power dissipation depends on the ESR of the crystal and is reflected by the maximum drive level of the crystal. Table 5-3 illustrates the power dissipation of the INAP125T12/24 and therefore the minimum drive level capabilities of the crystal at different crystal ESR levels.

| Crystal ESR | INAP125T12/24 Power dissipation /<br>Minimum crystal drive level | Unit |

|-------------|------------------------------------------------------------------|------|

| 30          | 77                                                               | μW   |

| 50          | 121                                                              | μW   |

| 80          | 179                                                              | μW   |

Table 5-3: Minimum Drive level vs. Crystal ESR

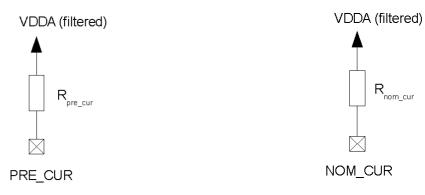

#### 5.2.5 Pre-Emphasis and Nominal Current

For optimized signal integrity and lowest EMI in dependence of the quality and length of the STP cable used, the output nominal current and the pre-emphasis current of the INAP125T12/24 can be set individually by means of external resistors.

Figure 5-5: Pre-emphasis Current

Figure 5-6: Nominal current

| Symbol               | Pin                          | Description                  | Min<br>(recomm.) | Max<br>(recomm.) | Unit |

|----------------------|------------------------------|------------------------------|------------------|------------------|------|

|                      |                              | resistor value               | 500              | 10000            | Ohm  |

| R <sub>pre_cur</sub> | R <sub>pre_cur</sub> PRE_CUR | typ. current of pre-emphasis | 0.05             | 1                | mA   |

|                      |                              | resistor value               | 500              | 10000            | Ohm  |

| $R_{nom\_cur}$       | NOM_CUR                      | typ. add-on output current   | 0.5              | 5                | mA   |

Table 5-4: Recommended component values for nominal and pre-emphasis

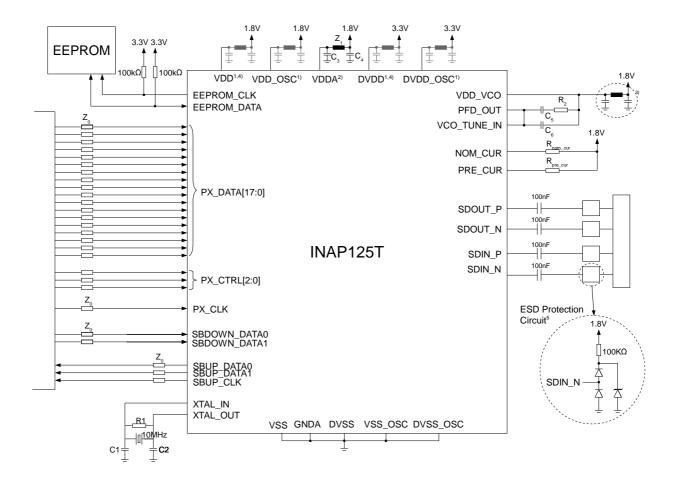

#### 6.0 Application Example

Z<sub>0</sub>. Trace impedance

R1,C1,C2: Please check crystal requirements for component values

Z1,C3,C4: Filter design must be designed to eliminate oscillation on high dynamic currents

with VDDA meeting specification requirements

R2,C5,C6: Please check Table 5-1 for component values

- 1) Filter not required for functional reasons, but might be considered for EMI performance

- 2) Filter not required for functional reasons, but strongly recommended for EMI performance

- 3) Filter recommended for performance reasons

- 4) Filter recommended on all DVDD, VDD input pins, if required for EMI performance

- 5) ESD protection design implementation example, please check available circuitry

Figure 6-1: Application example

#### 7.0 Electrical Characteristics

#### 7.1 Absolute Maximum ratings

The absolute maximum ratings define values beyond which damage to the device may occur. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The functional operation of the device at these or any other conditions beyond the recommended operating ratings is not guaranteed.

| Parameter                             | Symbol                                       | Min. | Max. | Units | Note                |

|---------------------------------------|----------------------------------------------|------|------|-------|---------------------|

| DC Supply Voltage                     | V <sub>DVDD</sub> ,<br>V <sub>DVDD_OSC</sub> | -0.5 | 5.0  | V     |                     |

| Input Voltage                         | $V_{VDD},V_{VDDA},\ V_{VDD\_OSC}$            | -0.5 | 3.0  | V     |                     |

| I/O Current (DC or transient any pin) | I <sub>D</sub>                               | -20  | +20  | mA    |                     |

| Storage Temperature                   | T <sub>stg</sub>                             | -55  | +150 | ° C   |                     |

| Max Soldering Temperature             | T <sub>SLD</sub> / T <sub>SLD</sub>          |      | 260  | ° C   | 40 seconds maximum  |

| ESD Voltage HBM                       | V <sub>ESDHBM</sub>                          |      | 3000 | V     | Human Body Model    |

| ESD Voltage CDM                       | V <sub>ESDCDM</sub>                          |      | 750  | V     | Charge Device Model |

Table 7-1: Absolute maximum ratings

#### 7.2 Recommended operating conditions

| Parameter           | Symbol                | Min. | Тур. | Max. | Units | Note                       |

|---------------------|-----------------------|------|------|------|-------|----------------------------|

| Digital Core supply | V <sub>VDD</sub>      | 1.71 | 1.8  | 1.89 | V     |                            |

| Analog supply       | $V_{VDDA}$            | 1.71 | 1.8  | 1.89 | V     |                            |

| Oscillator supply   | V <sub>VDD_OSC</sub>  | 1.71 | 1.8  | 1.89 | V     |                            |

| Digital IO Supply   | $V_{DVDD}$            | 2.97 | 3.3  | 3.63 | V     |                            |

| Oscillator supply   | V <sub>DVDD_OSC</sub> | 2.97 | 3.3  | 3.63 | V     |                            |

| CML Current         | I <sub>CML</sub>      | 0.8  | -    | 24   | mA    | Internal Current<br>Source |

| Ambient Temperature | T <sub>a</sub>        | -40  | -    | +105 | ° C   |                            |

Table 7-2: Recommended operating conditions

#### 7.3 DC Characteristics

under recommended operating conditions. Unused inputs should be tied to ground.

| Parameter                | Symbol              | Test Condition                  | Min. | Тур. | Max.       | Unit |

|--------------------------|---------------------|---------------------------------|------|------|------------|------|

| CMOS Input High Voltage  | ViH                 | V <sub>DVDD</sub> = 3.3 V       | 2.0  | -    | $V_{DVDD}$ | V    |

| CMOS Input Low Voltage   | Vıl                 | V <sub>DVDD</sub> = 3.3 V       | 0    | -    | 0.8        | V    |

| CMOS Input High Current  | Іін                 | $V_{IN} = V_{DVDD}$             | -10  | -    | 10         | μA   |

| CMOS Input Low Current   | lıL                 | Vin = 0 V                       | -15  | -    | -77        | μA   |

| CMOS Output High Voltage | Vон                 | Iон = -4 mA                     | 2.4  | -    | -          | V    |

| CMOS Output Low Voltage  | Vol                 | IoL = 4 mA                      | -    | -    | 0.4        | V    |

| CMOS Output High Current | Іон                 | Vон = 0.9 x DVDD                | -    | -    | 4          | mA   |

| CMOS Output Low Current  | loL                 | Vol = 0.1 x DVDD                | -    | -    | -4         | mA   |

| Power Dissipation Tx     | P <sub>max_Tx</sub> | max data transmis-<br>sion rate | -    | 170  | -          | mW   |

Table 7-3: DC characteristics

#### 7.3.1 Supply Current

| Parameter                   | min. | typ. | max. | Units |

|-----------------------------|------|------|------|-------|

| I vdd/vdd_osc               | -    | 11   | 14   | mA    |

| I <sub>vdda/vdd_vco</sub> a | -    | 82   | 95   | mA    |

| I dvdd/dvdd_osc             | -    | 7    | 8    | mA    |

**Table 7-4: Supply Current**

a. values at maximum serial drive current NOM\_CUR, configurable as described in section 5.2.5

#### 7.4 AC-Characteristics

| Parameter                                        | Min. | Тур. | Max. | Units  |

|--------------------------------------------------|------|------|------|--------|

| Input Capacitance, any pin                       | -    | 3    | 5    | pF     |

| Serial Transmission Gross Data Rate (Downstream) | 500  | -    | 1000 | MBit/s |

| Serial Transmission Gross Data Rate (Upstream)   | 20.8 | -    | 62.5 | MBit/s |

| CMOS Output Rise / Fall Time (CL = 10 pF)        | -    | 5    | 10   | ns     |

**Table 7-5: AC-Characteristics**

#### 7.5 Pixel Clock Range

| Parameter             | Symbol           | Min. | Тур. | Max. | Unit | Note                                            |

|-----------------------|------------------|------|------|------|------|-------------------------------------------------|

| Pixel Clock Frequency | f <sub>PIX</sub> | 6    |      | 62   | MHz  | Maximum frequency depends on selected bit width |

Table 7-6: Pixel Clock Range

## 8.0 Package Options / Ordering information

| Device / Ordering<br>Code | Description                              | Package | Minimum Order<br>Quantity |

|---------------------------|------------------------------------------|---------|---------------------------|

| INAP125T12                | Tx w/1012 bit Interface + 1 bit Sideband | QFN48   | 416 pcs/tray              |

| INAP125T12-R2             | Tx w/1012 bit Interface + 1 bit Sideband | QFN48   | 2000 pcs/reel             |

| INAP125T12-R4             | Tx w/1012 bit Interface + 1 bit Sideband | QFN48   | 4000 pcs/reel             |

| INAP125T24                | Tx w/1024 bit Interface + 2 bit Sideband | QFN64   | 260 pcs/tray              |

| INAP125T24-R2             | Tx w/1024 bit Interface + 2 bit Sideband | QFN64   | 2000 pcs/reel             |

| INAP125T24-R4             | Tx w/1024 bit Interface + 2 bit Sideband | QFN64   | 4000 pcs/reel             |

**Table 8-1: Package Options**

#### 8.1 RoHS compliance

The devices INAP125T12 and INAP125T24 are released as RoHS compliant.

# 9.0 Soldering information

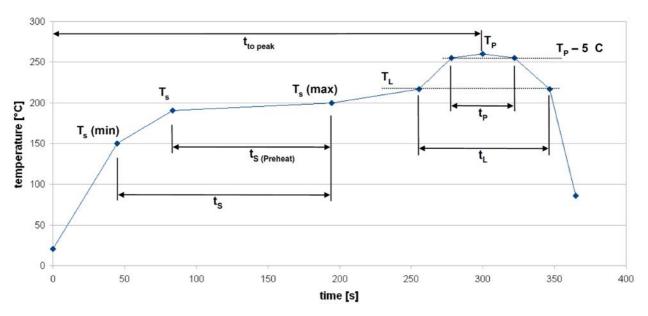

Figure 9-1: Reflow profile

| Phase    | Process parameter                                | target | unit |

|----------|--------------------------------------------------|--------|------|

| Pre-heat | ramp-up rate to 150°C (average value over 10s)   |        | K/s  |

|          | T <sub>s</sub> (min)                             | 150    | °C   |

|          | T <sub>s</sub>                                   | 190    | °C   |

|          | T <sub>s</sub> (max)                             | 200    | °C   |

|          | t <sub>s</sub>                                   | 150    | s    |

|          | t <sub>s (Pre-heat)</sub>                        | 110    | s    |

| Peak     | T <sub>L</sub>                                   | 217    | °C   |

|          | t <sub>L</sub> = time above T <sub>L</sub>       | 90     | s    |

|          | T <sub>P</sub>                                   | 260    | °C   |

|          | t <sub>P</sub> = time above T <sub>P</sub> - 5°C | 40     | s    |

| Cooling  | Ramp-down rate from TL (average value over 10s)  | 6      | K/s  |

| General  | t <sub>to peak</sub>                             | 300    | S    |

|          | number of soldering cycles                       | 3      |      |

Table 9-1: Reflow profile parameters

#### 10.0 Package information

#### 10.1 Pinout diagrams

Figure 10-1: INAP125T12 pinout diagram

Figure 10-2: INAP125T24 pinout diagram

#### 10.2 Package dimensions

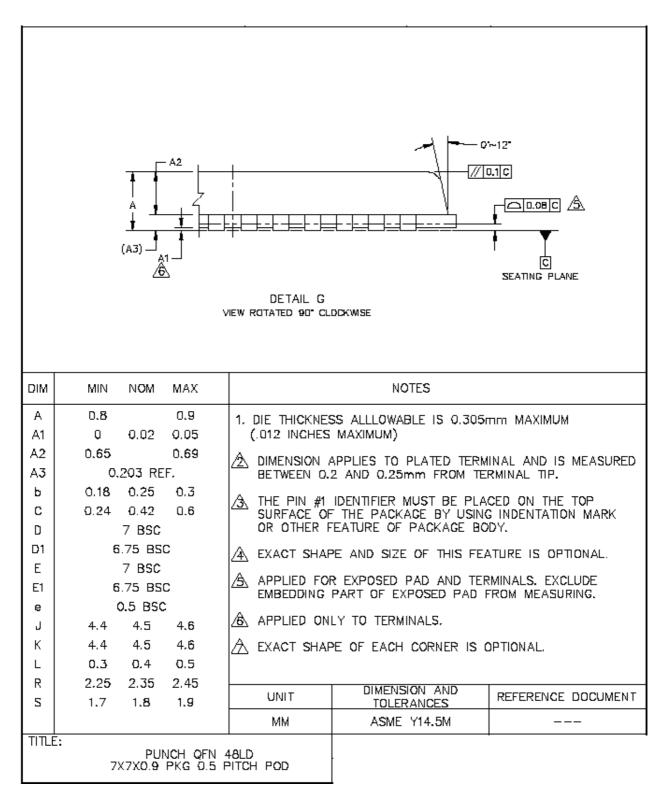

all values in millimeter

# 10.2.1 48-pin QFN A Ō G E1 E PIN 1 CORNER \_\_\_\_\_O.1 C **⊕** 0.1 C A B EXPOSED DIE ATTACH PAD <del>ΦΦΦΦΨ!ΦΦΦΦΦΦ</del> **⊕** 0.1 C A B RO.2 (PIN1 I.D.) 13 48X L -48X b VIEW M-M TITLE: PUNCH QFN 48LD 7X7X0.9 PKG 0.5 PITCH POD

Figure 10-3: 48-pin QFN package dimensions

Figure 10-4: 48-pin QFN package dimensions

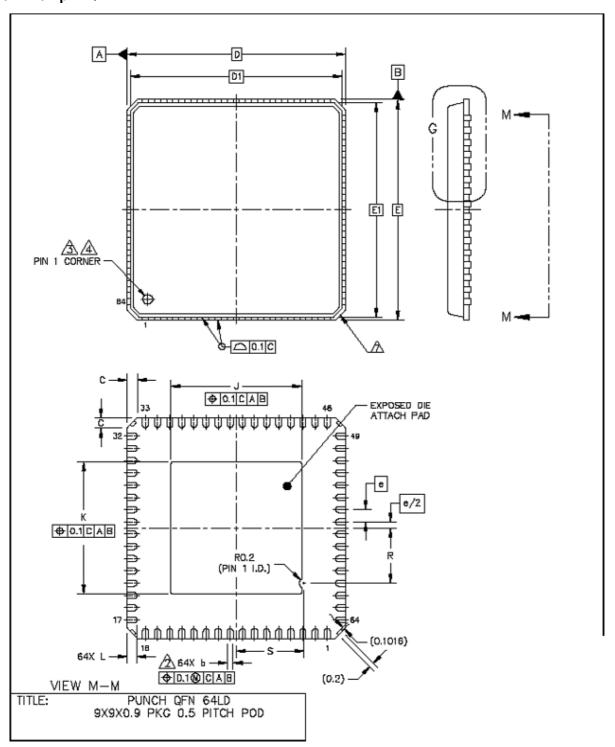

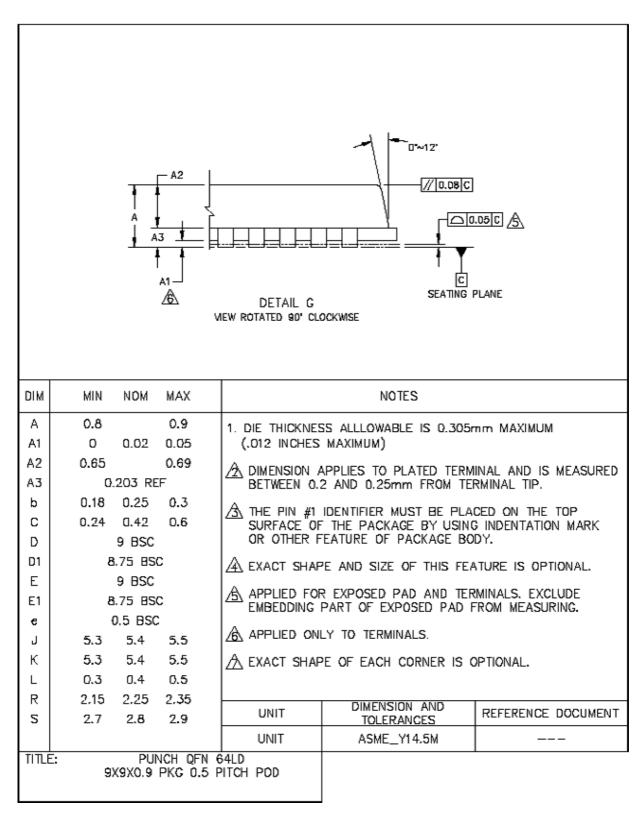

#### 10.2.2 64-pin QFN

Figure 10-5: 64-pin QFN package dimensions

Figure 10-6: 64-pin QFN package dimensions

# 11.0 Revision History

| Revision | Date          | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | February 2008 | Released Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.1      | December 2008 | <ul> <li>Separated Transmitter and Receiver Datasheet</li> <li>Various updates on general description and formatting</li> <li>Added separate block diagrams for T12 and T24</li> <li>Updated Section "Pixel Data Interface" at page 5</li> <li>Updated Section "Sideband Channel Downstream Interface" at page 6</li> <li>Updated Table 2-6, "INAP125T12 Pinout description, 48-pin QFN," on page 7</li> <li>Updated Table 2-7, "INAP125T24 Pin description, 64-pin QFN," on page 8</li> <li>Updated Section "Configuration vectors" at page 10</li> <li>Added Table 3-5, "TX Error pin configuration," on page 12</li> <li>Updated Section "External Reference Clock" at page 20</li> <li>Added Section "Application Example" at page 23</li> <li>Updated Section "Electrical Characteristics" at page 24</li> <li>Added Section "Soldering information" at page 28</li> </ul> |

**Table 11-1: Revision History**

#### **Inova Semiconductors GmbH**

Grafinger Str. 26

D-81671 Munich / Germany

Phone: +49 (0)89 / 45 74 75 - 60 +49 (0)89 / 45 74 75 - 88

Email: info@inova-semiconductors.de

URL: http://www.inova-semiconductors.com

All other trademarks or registered trademarks are the property of their respective holders.

Inova Semiconductors GmbH does not assume any liability arising out of the applications or use of the product described herein; nor does it convey any license under its patents, copyright rights or any rights of others.

Inova Semiconductors products are not designed, intended or authorized for use as components in systems to support or sustain life, or for any other application in which the failure of the product could create a situation where personal injury or death may occur. The information contained in this document is believed to be current and accurate as of the publication date. Inova Semiconductors GmbH reserves the right to make changes at any time in order to improve reliability, function or performance to supply the best product possible.

Inova Semiconductors GmbH assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made.

© Inova Semiconductors 2008