# **DS28DG02**

# 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

#### www.maxim-ic.com

#### GENERAL DESCRIPTION

The DS28DG02 combines 2kb (256 x 8) EEPROM with 12 PIO lines, a real-time clock (RTC) and calendar with alarm function, a CPU reset monitor, a battery monitor, and a watchdog. Communication with the device is accomplished with an industrystandard SPI™ interface. The user EEPROM is organized as four blocks of 64 bytes each with single-byte and up to 16-byte page write capability. Additional registers provide access to PIOs and to setup functions. Individual PIO lines can be configured as inputs or outputs. The power-on state of PIOs programmed as outputs is stored in nonvolatile (NV) memory. All PIOs may be reconfigured by the user through the serial interface. The RTC/calendar operates in the 12/24-hour format and automatically corrects for leap years. Battery monitor threshold and watchdog timeout are userprogrammable through NV registers. The reset monitor generates a reset to the CPU if the voltage at the V<sub>CC</sub> pin falls below the factory-set limit. The reset output includes a debounce circuit for manual pushbutton reset.

## **APPLICATIONS**

Asset-Tracking Systems

Broadband Access Network Equipment

Patient-Monitoring Systems

Home Lighting Control Systems

Holter Heart Monitors

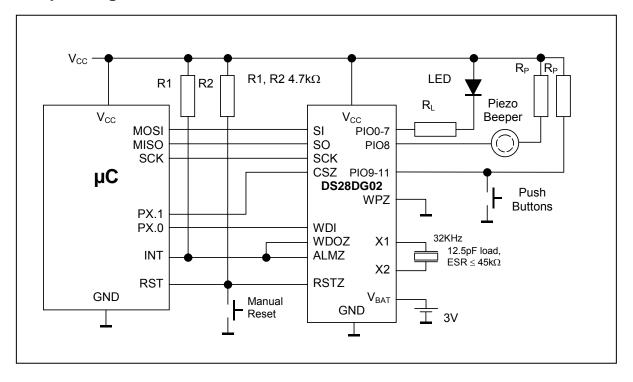

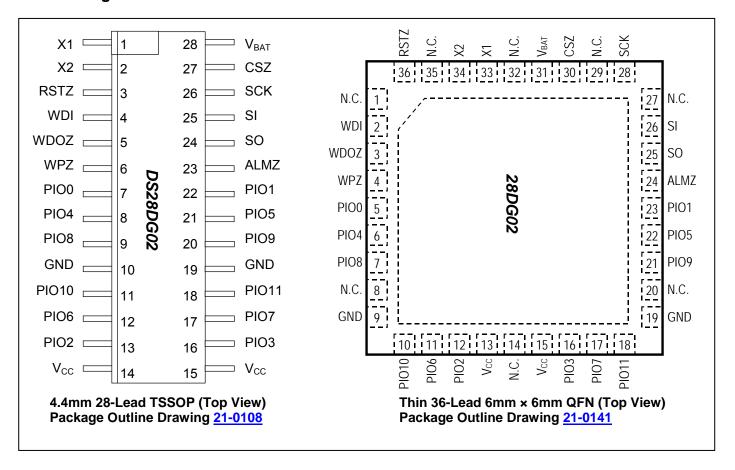

Typical Operating Circuit appears on page 32. Pin Configuration appears on page 33.

## **FEATURES**

- 2kb (256 x 8) EEPROM Organized in Four 64-Byte Blocks

- Single Byte and Up to 16-Byte EEPROM Write Sequences

- EEPROM Write-Protect Control Pin Protects

1, 2, or All 4 Blocks

- Endurance 200k Cycles per Page at +25°C;

10ms (max) EEPROM Write Cycle

- SPI Serial Interface Supporting Modes (0,0) and (1,1) at Up to 2MHz Clock Frequency

- 12 PIO Lines with LED Drive Capability

- Each PIO is Configured to Input or Output, Open-Drain/Push-Pull on Startup by Stored Value

- All PIOs are Reconfigurable After Startup

- RTC/Calendar/Alarm with BCD Format and Leap-Year Compensation

- RTC Controlled Through 32.768kHz, 12.5pF Crystal or External TCXO

- CPU Reset Through Fast-Response Precision

V<sub>CC</sub> Monitor with Hysteresis or Pushbutton

- Battery Monitor 2.5V, 2.25V, 2.0V, 1.75V, -5%

- Watchdog Timer 1.6s, 0.8s, 0.4s, 0.2s (typ)

- Unique Factory-Programmed 64-Bit Device Registration Number

- Operating Range: 2.2V to 5.25V, -40°C to +85°C

- ±4kV IEC 1000-4-2 ESD Protection Level (Except Crystal Pins)

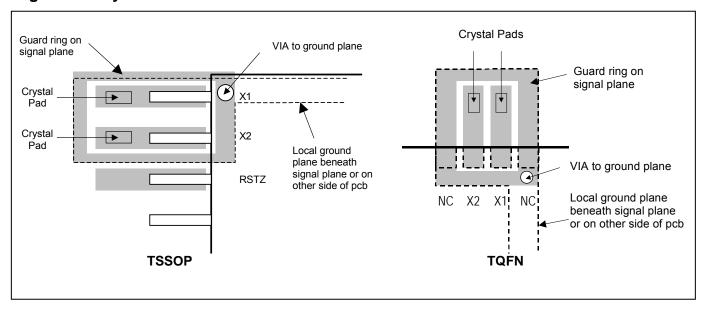

- Available in 28-Lead, 4.4mm TSSOP or 36-Lead 6mm × 6mm QFN Package

## ORDERING INFORMATION

| TEMP RANGE     | V <sub>CC</sub> TRIP                               | PIN-PACKAGE                                                                   | PKG CODE                                                                                                                              |

|----------------|----------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| -40°C to +85°C | 3.3V -5%                                           | 28 TSSOP-EP* (4.4mm)                                                          | U28E+5                                                                                                                                |

| -40°C to +85°C | 3.3V -5%                                           | 28 TSSOP-EP <sup>*</sup> T&R                                                  | U28E+5                                                                                                                                |

| -40°C to +85°C | 3.3V -5%                                           | 36 TQFN-EP* (6mm × 6mm)                                                       | T3666+3                                                                                                                               |

| -40°C to +85°C | 3.3V -5%                                           | 36 TQFN-EP <sup>*</sup> T&R                                                   | T3666+3                                                                                                                               |

|                | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C | -40°C to +85°C 3.3V -5%<br>-40°C to +85°C 3.3V -5%<br>-40°C to +85°C 3.3V -5% | -40°C to +85°C 3.3V -5% 28 TSSOP-EP* (4.4mm) -40°C to +85°C 3.3V -5% 28 TSSOP-EP* T&R -40°C to +85°C 3.3V -5% 36 TQFN-EP* (6mm × 6mm) |

<sup>\*</sup>EP = Exposed Paddle.

For additional  $V_{CC}$  monitor trip points or other device options, contact the factory.

Note: Registers are capitalized for clarity.

SPI is a trademark of Motorola, Inc.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <a href="www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

1 of 33 REV: 061907

<sup>+</sup> Denotes lead-free/RoHS compliant device.

## **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on Any Pin Relative to Ground -0.5V, +6V Maximum Current SO, ALMZ, RSTZ, WDOZ Pins  $\pm 20 mA$ Maximum Current Each PIO Pin ±50mA Maximum GND and V<sub>CC</sub> Current 270mA **Operating Temperature Range** -40°C to +85°C Junction Temperature +150°C Storage Temperature Range -55°C to +125°C Soldering Temperature See IPC/JEDEC J-STD-020

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device.

# **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                                    | PARAMETER SYMBOL CONDITIONS |                                          | MIN         | TYP  | MAX             | UNITS              |

|----------------------------------------------|-----------------------------|------------------------------------------|-------------|------|-----------------|--------------------|

|                                              |                             | Battery monitor off                      | 2.2         |      | 5.25            | V                  |

| Supply voltage                               | V <sub>CC</sub>             | Battery monitor enabled                  | 2.7         |      | 5.25            | ] V                |

| Battery Voltage                              | $V_{BAT}$                   | (Note 1)                                 | 1.5         | 3.0  | V <sub>CC</sub> | V                  |

| Potton/Current ()/ = 2.0\/                   |                             | RTC oscillator off                       |             |      | 2               |                    |

| Battery Current ( $V_{BAT} = 3.0V$ , Note 1) | I <sub>BAT</sub>            | RTC oscillator on                        |             | 0.4  | 10              | μA                 |

| Note 1)                                      |                             | RTC oscillator on, +25°C                 |             |      | 4.7             |                    |

|                                              |                             | SPI idle, ALMZ, WDOZ,                    |             |      |                 |                    |

| Standby Current (Note 2)                     |                             | RTSZ high, $V_{CC} = 5.25V$ ,            |             | 60   | 100             | μA                 |

| Standby Current (Note 2)                     | I <sub>ccs</sub>            | RTC oscillator on, all                   |             | 00   | 100             | μΑ                 |

|                                              |                             | PIOs grounded                            |             |      |                 |                    |

|                                              |                             | Reading EEPROM at 2                      |             |      |                 |                    |

|                                              |                             | Mbps, ALMZ, WDOZ,                        |             |      |                 |                    |

| Operating Current                            | I <sub>CCA</sub>            | RTSZ high, $V_{CC} = 5.25V$ ,            |             | 550  | 800             | μΑ                 |

|                                              |                             | RTC oscillator on, all                   |             |      |                 |                    |

|                                              |                             | PIOs grounded                            |             |      |                 |                    |

| Programming Current                          | I <sub>PROG</sub>           | V <sub>CC</sub> = 5.25V                  |             | 600  | 1000            | μA                 |

| V <sub>CC</sub> Monitor Trip Point           | $V_{TRIP}$                  | (Note 3)                                 | 2.97        | 3.05 | 3.14            | V                  |

| V <sub>CC</sub> Monitor Trip-Point           | V <sub>TRIPTOL</sub>        | +25°C                                    | -1.5        |      | +1.5            | %V <sub>TRIP</sub> |

| Tolerance                                    | V TRIPTOL                   | -40°C to +85°C                           | -2.5        |      | +2.5            |                    |

| V <sub>CC</sub> Monitor Hysteresis           | $V_{HYST}$                  |                                          | 0.4         | 0.5  | 0.6             | %V <sub>TRIP</sub> |

| Power-Up Wait Time                           | t <sub>POIP</sub>           |                                          |             |      | 60              | μs                 |

| EEPROM                                       |                             |                                          |             |      |                 |                    |

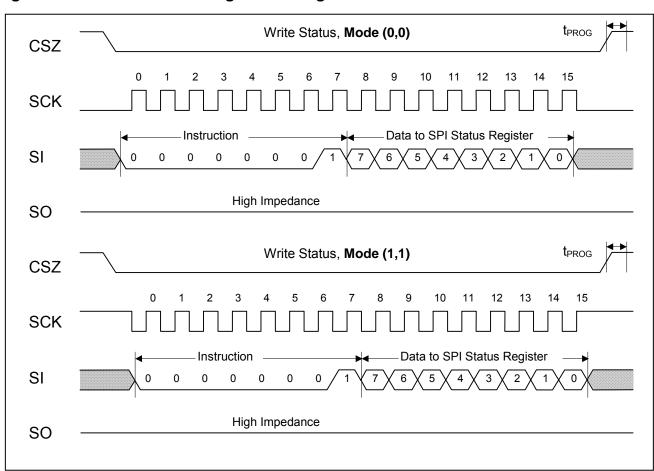

| Programming Time                             | t <sub>PROG</sub>           |                                          |             |      | 10              | ms                 |

| Endurance                                    | N <sub>CYCLE</sub>          | At +25°C (Notes 4, 5)                    | 200k        |      |                 | _                  |

| Data Retention                               | t <sub>RET</sub>            | At +85°C (Notes 5, 6)                    | 40          |      |                 | years              |

| REAL-TIME CLOCK                              |                             |                                          |             |      |                 |                    |

| Frequency Deviation                          | $\Delta_{F}$                | (Notes 5, 7)                             | -46         |      | +46             | PPM                |

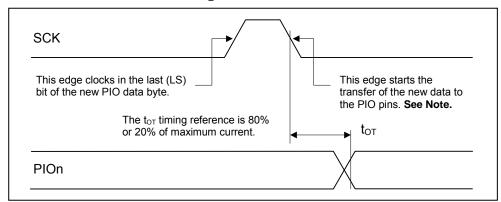

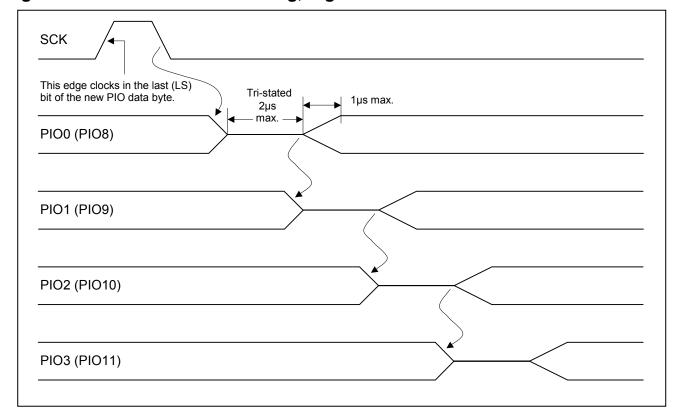

| PIO PINS (See Figures 21, 22,                | 23)                         |                                          |             |      |                 |                    |

| LOW-Level Output Current at                  |                             | V <sub>CC</sub> = 2.2V                   | 6           | 9.5  |                 |                    |

| $V_{OL} = 0.5V$ (Note 8)                     | I <sub>OL</sub>             | $V_{CC} = 3.3V$                          | 12.5        | 22.0 |                 | mA                 |

| · · · · · · · · · · · · · · · · · · ·        |                             | V <sub>CC</sub> = 5.25V                  | 19          | 30   |                 |                    |

| HIGH-Level Output Current                    | la                          | $V_{OH} = 2.4V, V_{CC} = 3.3V$           | 6.5<br>12.5 | 11.0 |                 | mA                 |

| (Note 8)                                     | IOH                         | $I_{OH}$ $V_{OH} = 4.5V, V_{CC} = 5.25V$ |             | 18.0 |                 | 111/5              |

| PARAMETER                                      | SYMBOL            | CONDITIONS                                                | MIN                          | TYP                                   | MAX                          | UNITS    |

|------------------------------------------------|-------------------|-----------------------------------------------------------|------------------------------|---------------------------------------|------------------------------|----------|

| LOW-Level Input Voltage                        | $V_{IL}$          |                                                           |                              |                                       | 8.0                          | V        |

| HIGH-Level Input Voltage                       | V <sub>IH</sub>   |                                                           | 0.7 ×<br>V <sub>CC</sub>     |                                       | V <sub>CC</sub> + 0.5V       | V        |

| Output Transition Time                         | t <sub>OT</sub>   | Low-current mode<br>(Note 9)<br>High-current mode         | 700                          |                                       | 1 25                         | μs       |

| Power-On Setting Time                          | t <sub>POS</sub>  | (Note 10) High-current mode                               |                              |                                       | 25                           | μs       |

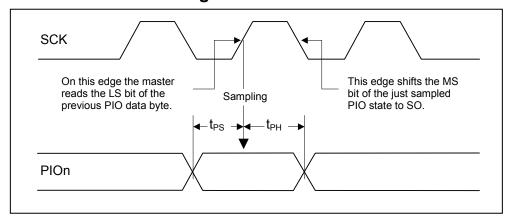

| PIO Read Setup Time                            |                   | (Note 11)                                                 | 100                          |                                       |                              | -        |

| PIO Read Selup Time PIO Read Hold Time         | t <sub>PS</sub>   | (Note 5)<br>(Note 5)                                      | 100                          |                                       |                              | ns       |

| Leakage Current                                | t <sub>PH</sub>   | High impedance, at V <sub>CCMAX</sub>                     | -1                           |                                       | +1                           | ns<br>µA |

| RSTZ PIN (Note 12) (See Figure                 | es 6, 7)          | Odwirok                                                   |                              |                                       |                              |          |

| LOW-Level Output Voltage                       | V <sub>OL</sub>   | At 4mA sink current                                       |                              |                                       | 0.3                          | V        |

| LOW-Level Input Voltage                        | V <sub>IL</sub>   |                                                           |                              |                                       | 0.3 ×<br>V <sub>CC</sub>     | V        |

| Input Leakage Current                          | IL                |                                                           | -1                           |                                       | +1                           | μA       |

| Minimum V <sub>CC</sub> for Valid RSTZ         | V <sub>POR</sub>  | (Notes 5, 13)                                             |                              |                                       | 2.13                         | ·V       |

| RSTZ Pulse Duration                            | t <sub>RST</sub>  |                                                           | 176                          | 328                                   | 532                          | ms       |

| Manual Reset Pulse Width  Manual Reset Release | t <sub>MPW</sub>  | (1)-1-44)                                                 | 1                            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |                              | μs       |

| Threshold                                      | V <sub>TRMS</sub> | (Note 14)                                                 |                              | V <sub>IL</sub>                       |                              | V        |

| Manual Reset Debounce Time                     | t <sub>DEB</sub>  | \/ falliag balant\/                                       |                              | t <sub>RST</sub>                      |                              | ms       |

| RSTZ Delay                                     | $t_{DEL}$         | V <sub>CC</sub> falling below V <sub>TRIP</sub> (Note 15) |                              |                                       | 90                           | μs       |

| ALMZ, WDOZ PINS                                |                   |                                                           |                              |                                       |                              |          |

| LOW-Level Output Voltage                       | V <sub>OL</sub>   | At 4mA sink current                                       |                              |                                       | 0.3                          | V        |

| WDI PIN                                        |                   |                                                           |                              |                                       |                              |          |

| LOW-Level Input Voltage                        | V <sub>IL</sub>   |                                                           |                              |                                       | 0.3 ×<br>V <sub>CC</sub>     | V        |

| HIGH-Level Input Voltage                       | V <sub>IH</sub>   |                                                           | 0.7 ×<br>V <sub>CC</sub>     |                                       | V <sub>CC</sub> + 0.5V       | ٧        |

| Input Leakage Current                          | IL                |                                                           | -1                           |                                       | +1                           | μΑ       |

| Minimum Input Pulse Width                      | t <sub>MPW</sub>  |                                                           | 1                            |                                       |                              | μs       |

| Watchdog Timeout                               | t <sub>WD</sub>   | User programmable                                         | 0.88<br>0.44<br>0.22<br>0.11 | 1.64<br>0.82<br>0.41<br>0.20          | 2.66<br>1.33<br>0.67<br>0.33 | S        |

| WPZ, SI, SCK, CSZ PINS                         |                   |                                                           |                              |                                       |                              |          |

| LOW-Level Input Voltage                        | V <sub>IL</sub>   |                                                           |                              |                                       | 0.3 ×<br>V <sub>CC</sub>     | V        |

| HIGH-Level Input Voltage                       | V <sub>IH</sub>   |                                                           | 0.7 × V <sub>CC</sub>        |                                       | V <sub>CC</sub> + 0.5V       | V        |

| Input Leakage Current                          | IL                |                                                           | -1                           |                                       | +1                           | μA       |

| SO PIN                                         | <del></del>       |                                                           | •                            |                                       |                              |          |

| LOW-Level Output Voltage                       | V <sub>OL</sub>   | At 1mA sink current and V <sub>CCmin</sub>                |                              |                                       | 0.2                          | V        |

| HIGH-Level Output Voltage                      | V <sub>OH</sub>   | At 1mA source current                                     | 0.7 × V <sub>CC</sub>        |                                       |                              | V        |

| Output Leakage Current                         | IL                | High impedance, at V <sub>CCmax</sub>                     | -1                           |                                       | +1                           | μA       |

|                                                | _I                | OUIIIAA                                                   | 1                            |                                       |                              | <u> </u> |

| PARAMETER                                     | SYMBOL               | SYMBOL CONDITIONS                                                       |                              | TYP                          | MAX                          | UNITS             |

|-----------------------------------------------|----------------------|-------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|-------------------|

| BATTERY MONITOR (See Fig                      | jure 8)              |                                                                         |                              |                              |                              | •                 |

| V <sub>BAT</sub> Trip Point                   | V <sub>BTP</sub>     | Measured with V <sub>BAT</sub> falling; trip point is user programmable | 2.25<br>2.03<br>1.80<br>1.58 | 2.31<br>2.08<br>1.85<br>1.62 | 2.38<br>2.14<br>1.90<br>1.66 | V                 |

| V <sub>BAT</sub> Monitor Trip-Point Tolerance | V <sub>TRIPTOL</sub> | +25°C<br>-40°C to +85°C                                                 | -1.5<br>-2.5                 |                              | +1.5<br>+2.5                 | %V <sub>BTP</sub> |

| Battery Test Load Current                     | I <sub>LOAD</sub>    |                                                                         | 7.5                          |                              | 20                           | μA                |

| Battery Test Duration                         | t <sub>BTPW</sub>    | Load applied to battery (Notes 5, 16)                                   |                              | 2                            |                              | S                 |

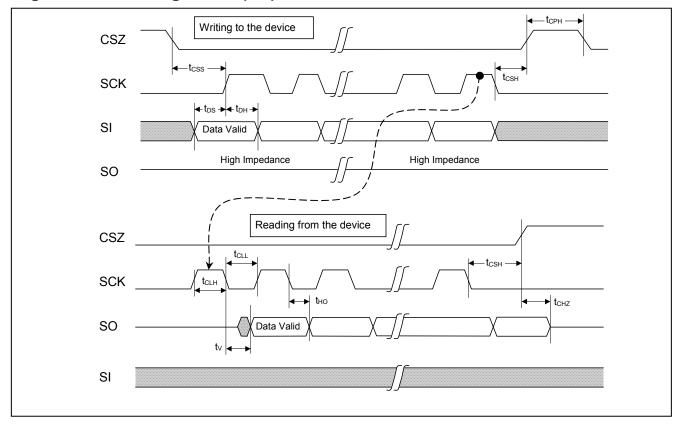

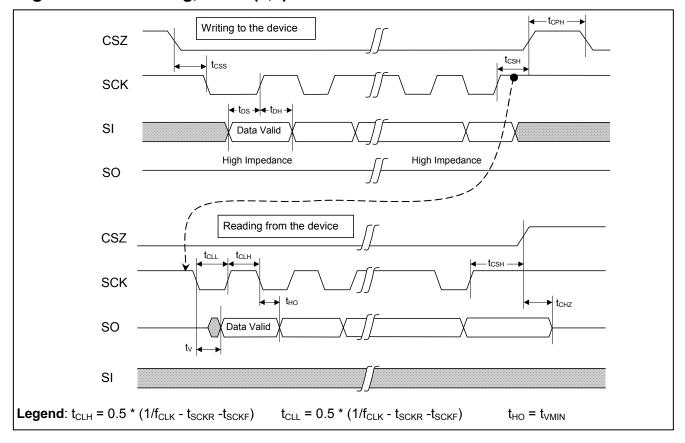

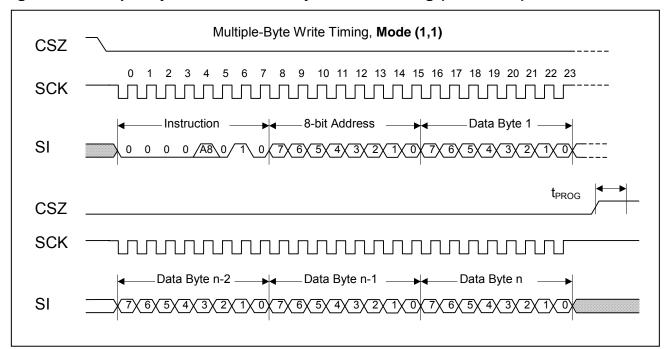

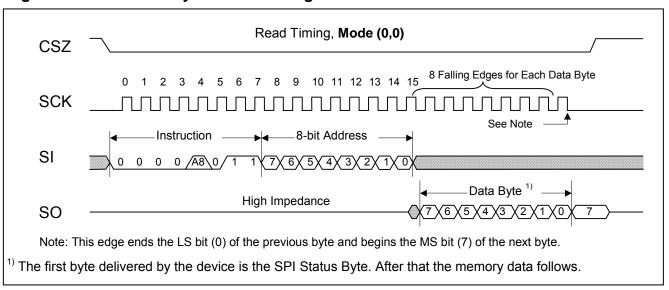

| SPI INTERFACE TIMING (See                     | Figures 9, 10)       |                                                                         |                              |                              |                              |                   |

| CSZ Setup Time                                | t <sub>CSS</sub>     | (Note 5)                                                                | 0.4                          |                              |                              | μs                |

| CSZ Hold Time                                 | t <sub>CSH</sub>     | (Note 5)                                                                | 0.4                          |                              |                              | μs                |

| CSZ Standby Pulse Width (Note 5)              | t <sub>CPH</sub>     | Normal communication (Note 17)                                          | 0.25<br>2.0                  |                              |                              | μs                |

| CSZ to High-Z at SO                           | t <sub>CHZ</sub>     | ,                                                                       |                              |                              | 0.25                         | μs                |

| SCK Clock Frequency                           | f <sub>CLK</sub>     |                                                                         |                              |                              | 2                            | MHz               |

| Data Setup Time                               | t <sub>DS</sub>      | (Note 5)                                                                | 50                           |                              |                              | ns                |

| Data Hold Time                                | t <sub>DH</sub>      | (Note 5)                                                                | 50                           |                              |                              | ns                |

| SCK Rise Time                                 | t <sub>SCKR</sub>    | (Note 5)                                                                |                              |                              | 1                            | μs                |

| SCK Fall Time                                 | t <sub>SCKF</sub>    | (Note 5)                                                                |                              |                              | 1                            | μs                |

| Output Valid time                             | $t_V$                | (Note 5)                                                                | 0                            |                              | 120                          | ns                |

- Note 1: If no battery is used, connect the V<sub>BAT</sub> pin to V<sub>CC</sub>. The RTC is powered by V<sub>BAT</sub> if V<sub>CC</sub> falls below V<sub>CCmin</sub>.

- **Note 2:** To the first order, this current is independent of the supply voltage value.

- Note 3: Nominal values: 3.3V -5%, set at factory. Measured with V<sub>CC</sub> falling; for V<sub>CC</sub> rising, the actual threshold is V<sub>TRIP</sub> + V<sub>HYST</sub>.

- **Note 4:** This specification is valid for each 16-byte memory page.

- **Note 5:** Not production tested. Either guaranteed by design (GBD) or guaranteed by a reliability study (EEPROM lifetime parameters).

- Note 6: EEPROM writes can become nonfunctional after the data-retention time is exceeded. Long-time storage at elevated temperatures is not recommended; the device can lose its write capability after 10 years at +125°C or 40 years at +85°C.

- **Note 7:** Valid with 32KHz crystal. 12.5pF. ESR  $\leq$  45k $\Omega$ . +25°C.

- **Note 8:** Total PIO sink and source currents through all PIO pins must be externally limited to less than the absolute maximum rating of 270mA minus 1.5mA for EEPROM programming and SPI communication. Exceeding the absolute maximum rating can cause damage.

- Note 9: Assumes the configuration of the system and the part is such that changing GOV<i> (0 ≤ i ≤ 11) between 'b1 and 'b0 switches between sourcing no current and sinking the absolute maximum current at the PIO<i> pin. The limit refers to the switching time between sinking 20% of the DC current and 80% of the DC current. The same is true for changing between 'b0 and 'b1 causing the part to switch from sinking no current to sourcing the absolute maximum current at the PIO<i> pin.

- Note 10: Each output pin transitions in 1µs with a pause of 1µs before the next pin transitions.

- **Note 11:** All PIO are tri-stated at beginning of reset prior to setting to power-on values.

- Note 12: If the part has battery power (normal case) the active pulldown of RSTZ is supported by the battery.

- Note 13: If V<sub>BAT</sub> is tied to V<sub>CC</sub> (no battery supply) the state of the RSTZ pulldown transistor is not guaranteed when V<sub>CC</sub> falls below V<sub>POR</sub>.

- Note 14: Threshold refers to the manual reset function obtained by forcing RSTZ low.

- Note 15: Transient response to a step on  $V_{CC}$  from above  $V_{TRIP}$  down to  $(V_{TRIP} 1mV)$ . Glitches on  $V_{CC}$  that are shorter than tobellimin are guaranteed to be suppressed, regardless of their amplitude. Glitches on  $V_{CC}$  that are longer than tobellimin are guaranteed not to be suppressed. This parameter is tested at high  $V_{CC}$  and guaranteed by design at low.

- Note 16: If enabled, this test takes place every hour on the hour. The battery voltage is compared to V<sub>BTP</sub> during the second half of the t<sub>BTPW</sub> window. The timing is controlled by the RTC.

- Note 17: Extended duration applies to the following cases:

- 1) Aborted WREN, WRDI, RDSR, and WRSR command.

- 2) WRITE command aborted before transmitting the first complete data byte after command and address.

- 3) READ command aborted before reading the first complete data byte after command and address.

- 4) Read aborted before the end of a byte.

## PIN DESCRIPTION

| NAME            | P       | IN                                 | FUNCTION                                                                                                                                                                                                   |  |  |

|-----------------|---------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | TSSOP28 | TQFN36                             | FUNCTION                                                                                                                                                                                                   |  |  |

| X1              | 1       | 33                                 | 32.768kHz Crystal Connection 1 or 32.768kHz Input from TCXO                                                                                                                                                |  |  |

| X2              | 2       | 34                                 | 32.768kHz Crystal Connection 2                                                                                                                                                                             |  |  |

| RSTZ            | 3       | 36                                 | <b>Open-Drain Output Pin (Active Low)</b> for V <sub>CC</sub> power-fail reset, watchdog alarm, and <b>Manual Reset Input</b> . See Multifunction Control/Setup Register description for more information. |  |  |

| WDI             | 4       | 2                                  | Watchdog Input Pin (Active High). See Multifunction Control/Setup Register description at address 134h for more information.                                                                               |  |  |

| WDOZ            | 5       | 3                                  | Open-Drain Output Pin (Active Low) for (user-choice) watchdog alarm. See <i>Multifunction Control/Setup Register</i> description for more information.                                                     |  |  |

| WPZ             | 6       | 4                                  | Hardware Write-Protect Input Pin (Active Low). See the SPI Interface description for more information.                                                                                                     |  |  |

| PIO0            | 7       | 5                                  | PIO Line #0                                                                                                                                                                                                |  |  |

| PIO4            | 8       | 6                                  | PIO Line #4                                                                                                                                                                                                |  |  |

| PIO8            | 9       | 7                                  | PIO Line #8                                                                                                                                                                                                |  |  |

| GND             | 10, 19  | 9, 19                              | Ground Supply                                                                                                                                                                                              |  |  |

| PIO10           | 11      | 10                                 | PIO Line #10                                                                                                                                                                                               |  |  |

| PIO6            | 12      | 11                                 | PIO Line #6                                                                                                                                                                                                |  |  |

| PIO2            | 13      | 12                                 | PIO Line #2                                                                                                                                                                                                |  |  |

| V <sub>CC</sub> | 14, 15  | 13, 15                             | Power Supply Input                                                                                                                                                                                         |  |  |

| PIO3            | 16      | 16                                 | PIO Line #3                                                                                                                                                                                                |  |  |

| PIO7            | 17      | 17                                 | PIO Line #7                                                                                                                                                                                                |  |  |

| PIO11           | 18      | 18                                 | PIO Line #11                                                                                                                                                                                               |  |  |

| PIO9            | 20      | 21                                 | PIO Line #9                                                                                                                                                                                                |  |  |

| PIO5            | 21      | 22                                 | PIO Line #5                                                                                                                                                                                                |  |  |

| PIO1            | 22      | 23                                 | PIO Line #1                                                                                                                                                                                                |  |  |

| ALMZ            | 23      | 24                                 | <b>Open-Drain Output Pin (Active Low)</b> for RTC, battery monitor, and (user-choice) watchdog alarms. See the <i>Multifunction Control/Setup Register</i> description for more information.               |  |  |

| SO              | 24      | 25                                 | SPI Serial Data Output (tristate)                                                                                                                                                                          |  |  |

| SI              | 25      | 26                                 | SPI Serial Data Input                                                                                                                                                                                      |  |  |

| SCK             | 26      | 28                                 | SPI Serial Clock Input                                                                                                                                                                                     |  |  |

| CSZ             | 27      | 30                                 | Chip Select Input (Active Low)                                                                                                                                                                             |  |  |

| $V_{BAT}$       | 28      | 31                                 | Backup Battery Supply for RTC and RSTZ support.                                                                                                                                                            |  |  |

| N.C.            | _       | 1, 8, 14,<br>20, 27,<br>29, 32, 35 | No Connection                                                                                                                                                                                              |  |  |

| GND             | EP      | EP                                 | <b>Exposed Paddle.</b> Solder evenly to the board's ground plane for proper operation. See <u>Application Note 3273</u> for additional information.                                                        |  |  |

## **OVERVIEW**

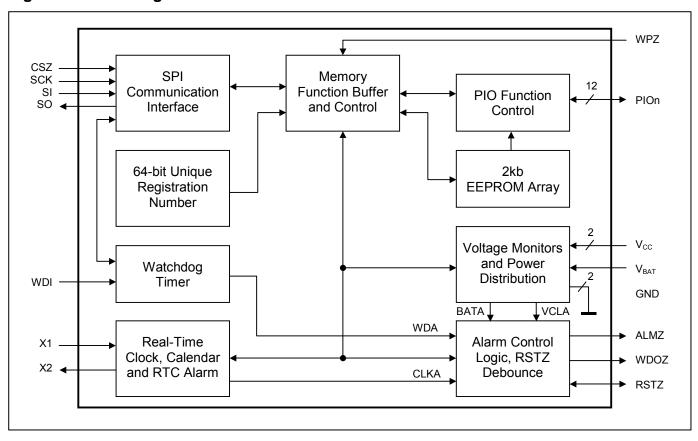

The DS28DG02 features 2kb of EEPROM, 12 bidirectional PIO channels, an RTC with calendar and alarm function, a watchdog timer, two voltage monitors with precision trip points, and three alarm/reset outputs. Each DS28DG02 has its own unique registration number, which serves as identification of the product the device is embedded in. All these resources are accessed through a serial SPI interface, as shown in the block diagram in Figure 1. The SPI interface automatically adjusts to SPI modes (0,0) and (1,1). The  $V_{CC}$  trip point, which controls the power-fail reset output (RSTZ pin), is set at the factory. The user can set the battery monitor threshold and the watchdog time-out through software. The RTC uses the common BCD format for time, calendar and day of the week. The device can be programmed to generate an RTC alarm every second, minute, hour, or day and once a week or once a month at a user-defined time. RTC, watchdog, and battery alarm can be individually enabled.

Figure 1. Block Diagram

The PIO configuration and setup of RTC/calendar with alarm are part of the *Detailed Register Description*. This section also includes specifics of the Multifunction Control/Setup register, which enables/disables several device functions, and the Alarm/Status register. For detailed information on the operation of the  $V_{CC}$  monitor/power-fail reset and the battery monitor see the *Monitoring Functions* section. The *SPI Interface* description explains the communication protocol for memory and register access and the use of the watchdog function. The *PIO Read/Write Access* section illustrates the behavior of the PIOs, in particular the address generation and timing in low- and high-current mode.

The DS28DG02 memory map (Figure 2) begins with 256 bytes of general-purpose user EEPROM, organized as four blocks of 64 bytes. Additional EEPROM is set aside to store power-on defaults for PIO state (high, low, in output mode), data direction (in, out), read-inversion (true, false), port output type (push-pull, open-drain), and output mode (high current, low current). Once powered up, the PIO settings can be overwritten through SRAM registers without affecting the power-on defaults. PIO state, direction, and read-inversion can be set for individual ports. The output type is set for groups of four PIOs and the selected output mode applies to all PIOs in output mode. The RTC/calendar, associated Alarm registers and the Multifunction Control/Status registers are kept nonvolatile through battery backup. Write-protection, if enabled, is available for all four EEPROM blocks, blocks 2 and 3 only, or block 3 only and for all writeable registers from address 120h and higher.

Figure 2. Memory Map

| ADDRESS        | TYPE    | ACCESS  | DESCRIPTION                                                                                                                                             |

|----------------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000h to 03Fh   | EEPROM  | R/W     | User memory block 0.                                                                                                                                    |

| 040h to 07Fh   | EEPROM  | R/W     | User memory block 1.                                                                                                                                    |

| 080h to 0BFh   | EEPROM  | R/W     | User memory block 2.                                                                                                                                    |

| 0C0h to 0FFh   | EEPROM  | R/W     | User memory block 3.                                                                                                                                    |

| 100h to 109h   | _       | _       | Reserved, contents undefined.                                                                                                                           |

| 10Ah           | EEPROM  | R/W     | Power-on default for PIO output state (PIO0 to PIO7).                                                                                                   |

| 10Bh           | EEPROM  | R/W     | Power-on default for PIO output state (PIO8 to PIO11).                                                                                                  |

| 10Ch           | EEPROM  | R/W     | Power-on default for PIO direction (PIO0 to PIO7).                                                                                                      |

| 10Dh           | EEPROM  | R/W     | Power-on default for PIO direction (PIO8 to PIO11).                                                                                                     |

| 10Eh           | EEPROM  | R/W     | Power-on default for PIO read-inversion (PIO0 to PIO7).                                                                                                 |

| 10Fh           | EEPROM  | R/W     | Power-on default for PIO read-inversion (PIO8 to PIO11), PIO output type (PIO0 to PIO11 in groups of 4 PIOs), PIO output mode (same mode for all PIOs). |

| 110h to 117h   | _       | _       | Reserved, contents is undefined.                                                                                                                        |

| 118h to 11Fh   | ROM     | R       | 64-bit unique registration number.                                                                                                                      |

| 120h           | SRAM    | R/W     | PIO output state (PIO0 to PIO7).                                                                                                                        |

| 121h           | SRAM    | R/W     | PIO output state (PIO8 to PIO11).                                                                                                                       |

| 122h           | SRAM    | R/W     | PIO direction (PIO0 to PIO7).                                                                                                                           |

| 123h           | SRAM    | R/W     | PIO direction (PIO8 to PIO11).                                                                                                                          |

| 124h           | SRAM    | R/W     | PIO read-inversion (PIO0 to PIO7).                                                                                                                      |

| 125h           | SRAM    | R/W     | PIO read-inversion (PIO8 to PIO11), PIO output type (PIO0 to PIO11 in groups of 4 PIOs), PIO output mode (same mode for all PIOs).                      |

| 126h           | _       | R       | PIO read access (PIO0 to PIO7).                                                                                                                         |

| 127h           | _       | R       | PIO read access (PIO8 to PIO11).                                                                                                                        |

| 128h           | _       |         | Reserved, contents undefined.                                                                                                                           |

| 129h to 12Fh   | NV SRAM | R/W     | RTC and calendar.                                                                                                                                       |

| 130h to 133h   | NV SRAM | R/W     | RTC alarm.                                                                                                                                              |

| 134h           | NV SRAM | R/W     | Multifunction control/setup register.                                                                                                                   |

| 135h           | NV SRAM | R/Clear | Alarm and status register.                                                                                                                              |

| 136h and above | _       | _       | Reserved, contents undefined.                                                                                                                           |

## **DETAILED REGISTER DESCRIPTIONS**

## Power-On Default for PIO Output State

| ADDR | b7   | b6   | b5   | b4   | b3    | b2    | b1   | b0   |

|------|------|------|------|------|-------|-------|------|------|

| 10Ah | POV7 | POV6 | POV5 | POV4 | POV3  | POV2  | POV1 | POV0 |

| 10Bh | Х    | Х    | Х    | Х    | POV11 | POV10 | POV9 | POV8 |

There is general read and write access to these addresses. Factory default: 10Ah: FFh; 10Bh: 0Fh. The contents of this register are automatically transferred to address 120h/121h when the device powers up.

| BIT DESCRIPTION                     | BIT(S) | DEFINITION                                                                        |

|-------------------------------------|--------|-----------------------------------------------------------------------------------|

| POVn: PIO Power-On<br>Default State | _      | Power-on default output <b>state</b> of PIO0 to PIO11. POV0 applies to PIO0, etc. |

| X: (Not Assigned)                   | _      | Reserved for future use.                                                          |

## **Power-On Default for PIO Direction**

| ADDR | b7   | b6   | b5   | b4   | b3    | b2    | b1   | b0   |

|------|------|------|------|------|-------|-------|------|------|

| 10Ch | POD7 | POD6 | POD5 | POD4 | POD3  | POD2  | POD1 | POD0 |

| 10Dh | Х    | Х    | Х    | Х    | POD11 | POD10 | POD9 | POD8 |

There is general read and write access to these addresses. Factory default: 10Ch: FFh; 10Dh: 0Fh. The contents of this register are automatically transferred to address 122h/123h when the device powers up.

| BIT DESCRIPTION                      | BIT(S) | DEFINITION                                                                                                 |  |  |  |

|--------------------------------------|--------|------------------------------------------------------------------------------------------------------------|--|--|--|

| PODn: PIO Power-On Default Direction | l      | Power-on default direction of PIO0 to PIO11. POD0 applies to PIO0, e <b>Legend</b> : 0 → output; 1 → input |  |  |  |

| X: (Not Assigned)                    | _      | Reserved for future use.                                                                                   |  |  |  |

## Power-On Default for PIO Read Inversion (PIO0 to PIO7)

| ADDR | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

|------|------|------|------|------|------|------|------|------|

| 10Eh | PIM7 | PIM6 | PIM5 | PIM4 | PIM3 | PIM2 | PIM1 | PIM0 |

There is general read and write access to this address. Factory default: 00h. The contents of this register are automatically transferred to address 124h when the device powers up.

| BIT DESCRIPTION                              | BIT(S) | DEFINITION                                                                                                                            |  |  |

|----------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIMn: PIO Power-On<br>Default Read-Inversion | _      | Power-on default state of the read-inversion bit of PIO0 to PIO7. PIM0 applies to PIO0, etc.  Legend: 0 → no inversion; 1 → inversion |  |  |

## Power-On Default for PIO Read Inversion (PIO8 to PIO11), PIO Output Type and Output Mode

| ADDR | b7   | b6   | b5   | b4   | b3    | b2    | b1   | b0   |  |

|------|------|------|------|------|-------|-------|------|------|--|

| 10Fh | POTM | РОТ3 | POT2 | POT1 | PIM11 | PIM10 | PIM9 | PIM8 |  |

There is general read and write access to this address. Factory default: 80h. The contents of this register are automatically transferred to address 125h when the device powers up.

| BIT DESCRIPTION                              | BIT(S)   | DEFINITION                                                                                                                              |

|----------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| PIMn: PIO Power-On<br>Default Read-Inversion | b0 to b3 | Power-on default state of the read-inversion bit of PIO8 to PIO11. PIM8 applies to PIO8, etc.  Legend: 0 → no inversion; 1 → inversion  |

| POT1: Power-On<br>Default Output Type        | b4       | Power-on default output type of PIO0 to PIO3;  Legend: 0 → push-pull; 1 → open drain                                                    |

| POT2: Power-On<br>Default Output Type        | b5       | Power-on default output type of PIO4 to PIO7; <b>Legend</b> : 0 → push-pull; 1 → open drain                                             |

| POT3: Power-On<br>Default Output Type        | b6       | Power-on default output type of PIO8 to PIO11;  Legend: 0 → push-pull; 1 → open drain                                                   |

| POTM: Power-On<br>Default Output Mode        | b7       | Power-on default output mode of PIO0 to PIO11;  Legend: 0 → low-current, simultaneous switching; 1 → high-current, sequential switching |

## **Unique Registration Number (118h to 11Fh)**

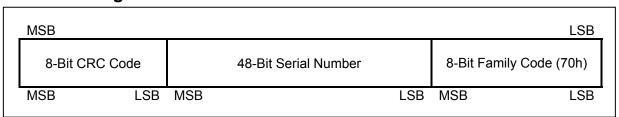

Each DS28DG02 has a unique registration number that is 64 bits long, as shown in Figure 3. The registration number begins with the family code at address 118h followed by the 48-bit serial number (LS-byte at the lower address) and ends at address 11Fh with the Cyclic Redundancy Check (CRC) of the first 56 bits. This CRC is generated using the a polynomial  $X^8 + X^5 + X^4 + 1$ . Additional information about CRCs is available in *Application Note 27*.

Figure 3. 64-Bit Registration Number

#### **PIO Output State**

| ADDR | b7  | b6  | b5  | b4  | b3   | b2   | b1  | b0  |

|------|-----|-----|-----|-----|------|------|-----|-----|

| 120h | OV7 | OV6 | OV5 | OV4 | OV3  | OV2  | OV1 | OV0 |

| 121h | Х   | Х   | Х   | Х   | OV11 | OV10 | OV9 | OV8 |

There is general read and write access to these addresses. These registers are automatically loaded with data from address 10Ah/10Bh when the device powers up.

| BIT DESCRIPTION       | BIT(S) | DEFINITION                                                                                                     |

|-----------------------|--------|----------------------------------------------------------------------------------------------------------------|

| OVn: PIO Output State |        | Output state of PIO0 to PIO11. OV0 applies to PIO0, etc.  Legend: 0 → LOW; 1 → HIGH if PIO direction is output |

| X: (Not Assigned)     | _      | Reserved for future use.                                                                                       |

#### **PIO Direction**

| ADDR | b7   | b6   | b5   | b4   | b3    | b2    | b1   | b0   |

|------|------|------|------|------|-------|-------|------|------|

| 122h | DIR7 | DIR6 | DIR5 | DIR4 | DIR3  | DIR2  | DIR1 | DIR0 |

| 123h | Х    | Х    | Х    | Х    | DIR11 | DIR10 | DIR9 | DIR8 |

There is general read and write access to these addresses. These registers are automatically loaded with data from address 10Ch/10Dh when the device powers up.

| BIT DESCRIPTION     | BIT(S) | DEFINITION                                                                            |

|---------------------|--------|---------------------------------------------------------------------------------------|

| DIRn: PIO Direction |        | Direction of PIO0 to PIO11. DIR0 applies to PIO0, etc.  Legend: 0 → output; 1 → input |

| X: (Not Assigned)   | _      | Reserved for future use.                                                              |

## PIO Read Inversion (PIO0 to PIO7)

| ADDR | b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 124h | IMSK7 | IMSK6 | IMSK5 | IMSK4 | IMSK3 | IMSK2 | IMSK1 | IMSK0 |

There is general read and write access to this address. This register is automatically loaded with data from address 10Eh when the device powers up.

| BIT DESCRIPTION               | BIT(S) | DEFINITION                                                                                                         |  |  |

|-------------------------------|--------|--------------------------------------------------------------------------------------------------------------------|--|--|

| IMSKn: PIO Read-<br>Inversion |        | Read-inversion bit of PIO0 to PIO7. IMSK0 applies to PIO0, etc.<br><b>Legend</b> : 0 → no inversion; 1 → inversion |  |  |

## PIO Read Inversion (PIO8 to PIO11), PIO Output Type and Output Mode

| ADDR | b7  | b6  | b5  | b4  | b3     | b2     | b1    | b0    |

|------|-----|-----|-----|-----|--------|--------|-------|-------|

| 125h | OTM | OT3 | OT2 | OT1 | IMSK11 | IMSK10 | IMSK9 | IMSK8 |

There is general read and write access to this address. This register is automatically loaded with data from address 10Fh when the device powers up.

| BIT DESCRIPTION               | BIT(S)   | DEFINITION                                                                                                             |

|-------------------------------|----------|------------------------------------------------------------------------------------------------------------------------|

| IMSKn: PIO Read-<br>Inversion | b0 to b3 | Read-inversion bit of PIO8 to PIO11. PIM8 applies to PIO8, etc.<br><b>Legend</b> : 0 → no inversion; 1 → inversion     |

| OT1: Output Type              | b4       | Output type of PIO0 to PIO3;<br><b>Legend</b> : 0 → push-pull; 1 → open drain                                          |

| OT2: Output Type              | b5       | Output type of PIO4 to PIO7; <b>Legend</b> : 0 → push-pull; 1 → open drain                                             |

| OT3: Output Type              | b6       | Output type of PIO8 to PIO11;  Legend: 0 → push-pull; 1 → open drain                                                   |

| OTM: Output Mode              | b7       | Output mode of PIO0 to PIO11;  Legend: 0 → low-current, simultaneous switching; 1 → high-current, sequential switching |

#### **PIO Read Access**

| ADDR | b7  | b6  | b5  | b4  | b3   | b2   | b1  | b0  |

|------|-----|-----|-----|-----|------|------|-----|-----|

| 126h | IV7 | IV6 | IV5 | IV4 | IV3  | IV2  | IV1 | IV0 |

| 127h | 0   | 0   | 0   | 0   | IV11 | IV10 | IV9 | IV8 |

There is only read access to these addresses. Bits 4 to 7 of address 127h always read 0. Read access is functional for all PIOs, regardless of their direction setting. Reported is the logic state of the pin, which may be different from what the PIO output value register implies.

| BIT DESCRIPTION          | BIT(S) | DEFINITION                                                                                                |

|--------------------------|--------|-----------------------------------------------------------------------------------------------------------|

| IVn: Input Value of PIOn | _      | Logic state read from PIO0 to PIO11 pins. IV0 applies to PIO0, etc.  Legend: IVn = PIOn XOR'ed with IMSKn |

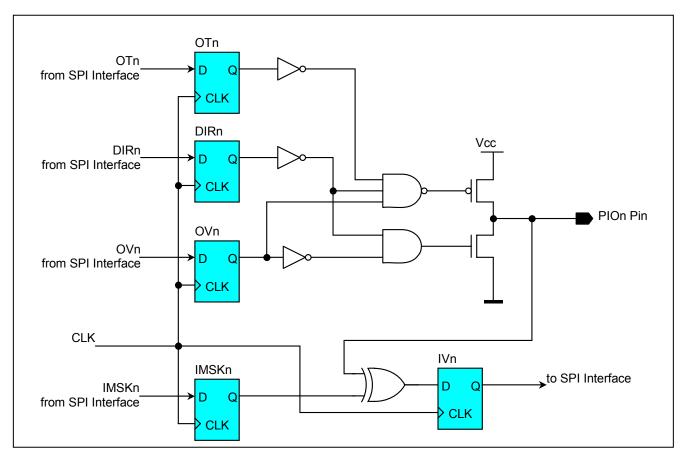

Figure 4 shows a simplified schematic of a PIO. The flip flops are accessed through the PIO Output State (OVn) and Read Access (IVn) registers and memory addresses 122h to 125 (DIRn, IMSKn, OTn). They are initialized at power-up or during Refresh (see the *SPI Interface Description*) according to the data stored at memory addresses 10Ah to 10Fh. When a PIO is configured as input, the PIO output is tri-stated (high impedance). When a PIO is configured as output, the PIO input is the same as the output state XORed with the corresponding read inversion bit. The differences of the PIO behavior in low current and high current mode are explained in the *PIO Read/Write Access* section near the end of this document.

Figure 4. PIO Simplified Schematic

## **RTC and Calendar Registers**

| ADDR | b7 | b6    | b5           | b4    | b3            | b2             | b1        | b0 |

|------|----|-------|--------------|-------|---------------|----------------|-----------|----|

| 129h | 0  | 1     | 0 Second     | S     |               | Single Seconds |           |    |

| 12Ah | 0  |       | 10 Minutes   |       |               | Single I       | Minutes   |    |

| 12Bh | 0  | 12/24 | 10hrs<br>A/P | 10hrs |               | Single         | Hours     |    |

| 12Ch | 0  | 0     | 0            | 0     | 0             | С              | ay of Wee | k  |

| 12Dh | 0  | 0     | 10 [         | Date  |               | Single         | e Date    |    |

| 12Eh | 0  | 0     | 0            |       | Single Months |                |           |    |

| 12Fh |    | 10 Y  | ears         |       |               | Single         | Years     |    |

There is general read and write access to these addresses. Bits shown as 0 cannot be written to 1. The RTC and calendar registers are reset to 00h when the battery voltage ramps up. Writes take effect immediately. To prevent unexpected increments during write access, first update the seconds; this creates a 1s window to finish updating the RTC/Calendar registers without any carryover from the Seconds register. Whenever the DS28DG02 receives a SPI Read command, the RTC and Calendar registers are copied to a buffer. When during a read access the address counter points to the RTC/Calendar registers, data from the buffer is transmitted. To obtain most accurate RTC data, start reading at the Seconds register.

The number representation of the RTC/Calendar registers is BCD (binary-coded decimal). The RTC can run in the 12-hour AM/PM and the 24-hour mode. The "12/24" bit (bit 6 of address 12Bh) defines the mode. For 12-hour AM/PM mode, set this bit to 1; bit 5 of address 12Bh then indicates AM (0b) or PM (1b). In the 24-hour mode, bit 5 and bit 4 together indicate the multiple of 10 hours. The Day of Week register counts from 1 to 7. The calendar logic is designed to automatically compensate for leap years. For every year value that is either 00 or a multiple of 4 the device will add a 29th of February. This will work correctly up to (but not including) the year 2100.

## **RTC Alarm Registers**

| ADDR  | b7       | b6    | b5         | b4      | b3    | b2       | b1           | b0 |  |

|-------|----------|-------|------------|---------|-------|----------|--------------|----|--|

| 130h  | AM1      | 1     | 10 Seconds |         |       | Single S | Seconds      |    |  |

| 131h  | AM2      |       | 10 Minutes |         |       | Single I | Minutes      |    |  |

| 132h  | ANA2 42/ |       | AM3 12/24  |         | 10hrs | 10hrs    | Single Hours |    |  |

| 13211 | AM3      | 12/24 | A/P        | 101115  |       | Sirigle  | Hours        |    |  |

| 133h  | AM4      | DY/DT | 0          | 0       | 0     | С        | ay of Wee    | k  |  |

| 13311 | AIVI4    | וטוזט | 10 [       | 10 Date |       | Single   | Date         |    |  |

There is general read and write access to these addresses. Bits shown as 0 cannot be written to 1. The RTC Alarm registers are reset to 00h when the battery voltage ramps up. To generate an alarm, there must be a match between Alarm registers and RTC registers. Alarm register addresses 130h to 132h correspond to RTC register addresses 129h to 12Bh; bits 6:0 participate in the comparison. The lower 6 bits of register address 133h correspond to 12Ch if DY/DT is 1 and to 12Dh if DY/DT is 0; the upper 2 bits of this register do not participate in the comparison. The control bits AM1, AM2, AM3, and AM4 determine the frequency of the alarm, as shown in Table 1. When the alarm occurs, the CLKA bit of the Alarm and Status register at address 135h changes to 1. The RTC must be running for the device to generate RTC alarms (OSCE at address 134h = 1).

**Table 1. Alarm Frequency Control**

| DY/DT | AM4 | AM3 | AM2 | AM1 | ALARM OCCURRENCE                                          |  |  |

|-------|-----|-----|-----|-----|-----------------------------------------------------------|--|--|

| Х     | Х   | Х   | Х   | 1   | Every second                                              |  |  |

| Х     | Х   | Х   | 1   | 0   | Every minute, when the seconds match                      |  |  |

| Х     | Х   | 1   | 0   | 0   | Every hour, when minutes and seconds match                |  |  |

| Х     | 1   | 0   | 0   | 0   | Every day, when hours, minutes, and seconds match         |  |  |

| 1     | 0   | 0   | 0   | 0   | Every week, when day, hours, minutes, and seconds match   |  |  |

| 0     | 0   | 0   | 0   | 0   | Every month, when date, hours, minutes, and seconds match |  |  |

## **Multifunction Control/Setup Register**

| ADDR | b7 | b6  | b5 | b4 | b3   | b2  | b1   | b0  |

|------|----|-----|----|----|------|-----|------|-----|

| 134h | 0  | BME | ВТ | RP | WDOS | WDE | OSCE | CAE |

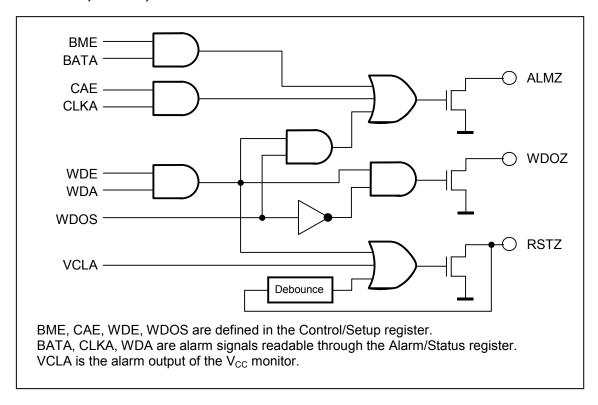

There is general read and write access to this address. Bit 7 always reads 0; it cannot be written to 1. This register is reset to 00h when the battery voltage ramps up. See Figure 5 for the use of the CAE, WDE, WDOS, and BME bits in the generation of the ALMZ, RSTZ, and WDOZ signals.

| BIT DESCRIPTION                                                                                                                                                                                                            | BIT(S)                                                             | DEFINITION                                                                                                                                                                                                                                                  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CAE: Clock Alarm<br>Enable                                                                                                                                                                                                 | b0                                                                 | Enable/disable control of the RTC/Calendar alarm.  Legend: 0 → disabled (power-on default); 1 → enabled                                                                                                                                                     |  |  |

| OSCE: RTC Oscillator<br>Enable                                                                                                                                                                                             | b1                                                                 | Run/halt control of the RTC's 32KHz oscillator  Legend: 0 → halted (power-on default); 1 → running                                                                                                                                                          |  |  |

| WDE: Watchdog Enable                                                                                                                                                                                                       | b2                                                                 | Enable/disable control of the watchdog and its alarm.  Legend: 0 → disabled (power-on default); 1 → enabled  The watchdog timer is reset by changing WDE from 0 to 1, V <sub>CC</sub> ramp up (Power-on reset) or applying a positive pulse at the WDI pin. |  |  |

| WDOS: Watchdog<br>Output Selection                                                                                                                                                                                         | b3                                                                 | Pin selection for watchdog alarm signaling.  Legend: 0 → WDOZ pin (power-on default); 1 → ALMZ pin                                                                                                                                                          |  |  |

| BTRP: Battery Monitor<br>Trip Point                                                                                                                                                                                        | Selection of the <b>nominal</b> Battery Monitor Trip Point voltage |                                                                                                                                                                                                                                                             |  |  |

| BME: Battery Monitor  BME: Battery Monitor |                                                                    | The battery test takes place a) after BME changes to 1, b) after V <sub>CC</sub> ramps up, c) every hour on the hour. The RTC must be running (OSCE                                                                                                         |  |  |

## **Alarm and Status Register**

| ADDR | b7 | b6   | b5   | b4  | b3  | b2   | b1  | b0  |

|------|----|------|------|-----|-----|------|-----|-----|

| 135h | 0  | BATA | WPZV | POR | BOR | CLKA | WDA | RST |

There is general read access to this address; writing clears all bits to 0. Bit 7 always reads 0. See Figure 5 for the use of the CLKA, WDA, and BATA bits in the generation of the ALMZ, RSTZ, and WDOZ signals.

| BIT DESCRIPTION                    | BIT(S) | DEFINITION                                                                                                                                                                                                                                                                |

|------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST: Reset Flag                    | b0     | RSTZ pin activity indicator; set whenever there is a pulse at RSTZ; cleared by writing to the Alarm and Status register. $V_{\text{CC}}$ ramp up: 1; $V_{\text{BAT}}$ attach: 0                                                                                           |

| WDA: Watchdog Alarm                | b1     | Watchdog Alarm indicator; set whenever the watchdog is enabled AND the watchdog timer expires; cleared by writing to the Alarm and Status register. $V_{\text{CC}}$ ramp up: 0; $V_{\text{BAT}}$ attach: 0                                                                |

| CLKA: Clock Alarm                  | b2     | RTC/Calendar Alarm indicator; set whenever the clock alarm is enabled AND RTC and RTC Alarm register match; cleared by writing to the Alarm and Status register.<br>$V_{\text{CC}}$ ramp up: 0; $V_{\text{BAT}}$ attach: 0                                                |

| BOR: Battery-On Reset Flag         | b3     | Battery attach indicator; set whenever the voltage at $V_{BAT}$ ramps up above $V_{BATmin}$ ; cleared by writing to the Alarm and Status register. $V_{CC}$ ramp up: not affected; $V_{BAT}$ attach: 1                                                                    |

| POR: Power-On Reset Flag           | b4     | Power-On Reset indicator; set whenever the voltage at $V_{CC}$ ramps up above $V_{CCmin}$ ; cleared by writing to the Alarm and Status register. $V_{CC}$ ramp up: 1; $V_{BAT}$ attach: 0                                                                                 |

| WPZV: Hardware Write Protect Value | b5     | WPZ pin state readout; reports the logic state at the WPZ pin; $V_{\text{CC}}$ ramp up: WPZ pin state; $V_{\text{BAT}}$ attach: not affected.                                                                                                                             |

| BATA: Battery Alarm                | b6     | Low Battery indicator; set whenever the battery alarm is enabled AND if, during a battery test, $V_{BAT}$ is below the selected $V_{BAT}$ trip point; cleared by writing to the Alarm and Status register. $V_{CC}$ ramp up: battery test if BME = 1; $V_{BAT}$ attach: 0 |

Figure 5. ALMZ, WDOZ, and RSTZ Generation

#### MONITORING FUNCTIONS

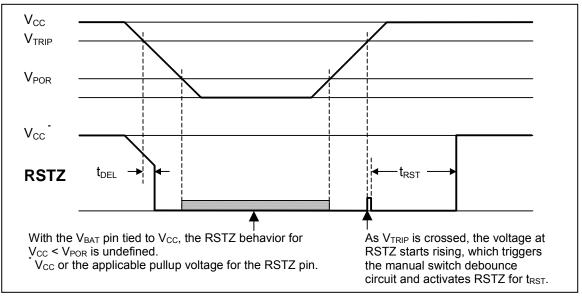

The DS28DG02 has two voltage monitors: one for the  $V_{CC}$  supply voltage and another one for the battery that supplies the RTC and associated registers if  $V_{CC}$  is switched off. If  $V_{CC}$  falls below the  $V_{TRIP}$  threshold the  $V_{CC}$  monitor activates the open-drain RSTZ output, as shown in Figure 6. There is a delay of  $t_{DEL}$  between crossing the trip point and RSTZ going LOW. As long as  $V_{CC}$  is above  $V_{POR}$  or the device has a functioning battery backup, the logic level at RSTZ does not exceed  $V_{OLmax}$ . Without battery support, the state of the RSTZ output is undefined for  $V_{CC}$  values below  $V_{POR}$ . When  $V_{CC}$  ramps up, RSTZ remains at LOW until the  $V_{TRIP}$  threshold is reached. As  $V_{TRIP}$  is crossed, the voltage at RSTZ rises until it reaches  $V_{TRMS}$ , the manual reset release threshold. This activates the debounce circuit, which holds RSTZ low for  $t_{RST}$ . After  $t_{RST}$  is expired, the voltage at RSTZ ramps up to the value of the applied pullup voltage.

Figure 6. RSTZ Power-Fail Reset

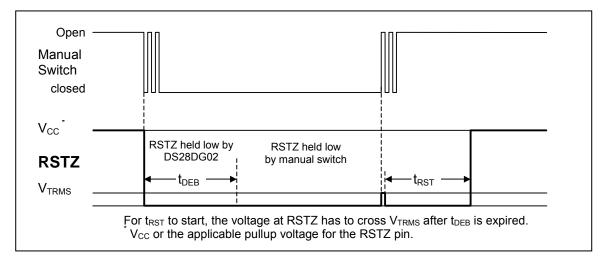

The RSTZ pin is internally connected to a debounce circuit, which allows using a manually operated switch to generate a reset signal. Figure 7 illustrates the timing of the manual reset. As the switch closes, it forces the voltage at RSTZ to fall below  $V_{\text{ILmax}}$ , which triggers the debounce circuit. Now the voltage at RSTZ is held at logic LOW by both, the manual switch and the debounce circuit. When the manual switch is opened or  $t_{\text{DEB}}$  is over, (whichever occurs later) the voltage at RSTZ rises until it reaches  $V_{\text{TRMS}}$ . This again triggers the debounce circuit, which holds RSTZ low for  $t_{\text{RST}}$ , after which the voltage at RSTZ ramps up to the pullup voltage. The minimum LOW time of a manually generated reset is  $t_{\text{DEB}} + t_{\text{RST}}$ .

Figure 7. RSTZ Manual Switch Debounce

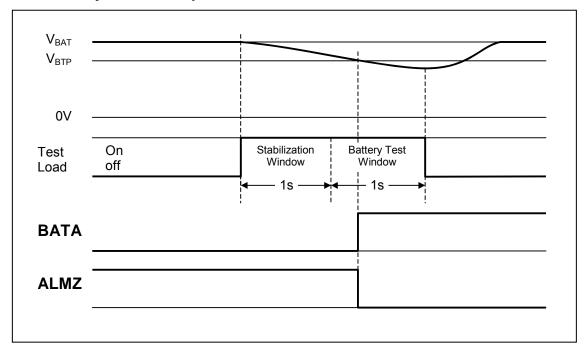

In contrast to the  $V_{CC}$  monitor, the battery monitor is active only for two seconds per hour, and only if it is enabled through the BME bit in the Multifunction Control/Setup register. In addition to this, the DS28DG02 must have sufficient  $V_{CC}$  power and the RTC must be running (OSCE = 1). The battery test takes place a) immediately after enabling the battery monitor, and, if the battery monitor is enabled, b) every hour on the full hour, and c) immediately after  $V_{CC}$  ramps up above  $V_{POR}$ . Figure 8 shows the details.

The battery test procedure begins with the DS28DG02 internally connecting the test load to the  $V_{BAT}$  pin. If the battery is near the end of its lifetime, this extra load causes the battery voltage to fall below  $V_{BTP}$ , the Battery Trip Point. After the stabilization window is over, the actual comparison of the battery voltage to the battery trip point takes place. If at the beginning of or during the battery test window the battery voltage falls below  $V_{BTP}$ , the battery alarm flag BATA in the Alarm and Status register is set, which in turn activates the ALMZ output. The BATA flag is cleared by a) replacing the battery, or b) by writing to the Alarm and Status register. The BATA flag is not cleared if a subsequent battery test, e.g., one hour later or after power-cycling the DS28DG02, determines that the battery voltage is above  $V_{BTP}$ . Note that replacing the battery resets the RTC and clears the Multifunction Control/Setup register.

Battery monitoring is only useful when performed regularly. Equipment that is powered-down for excessively long periods can completely drain its battery without receiving any advanced warning. To prevent such an occurrence, equipment using the battery-monitoring feature should be switched on periodically, e.g., once a month, to perform a battery test.

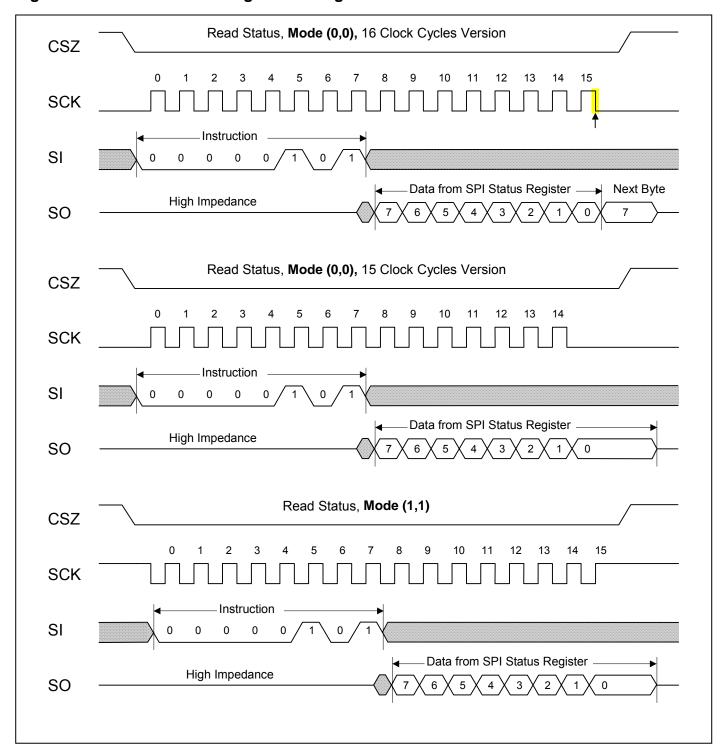

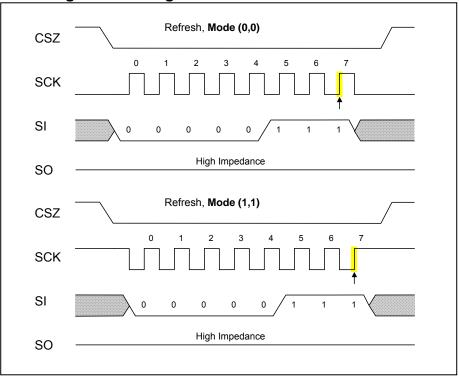

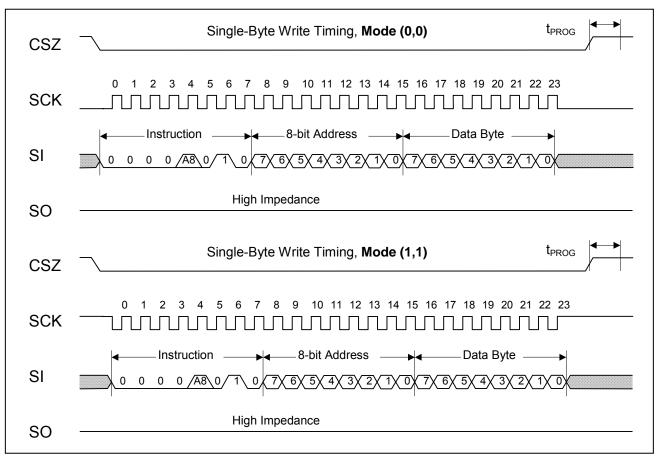

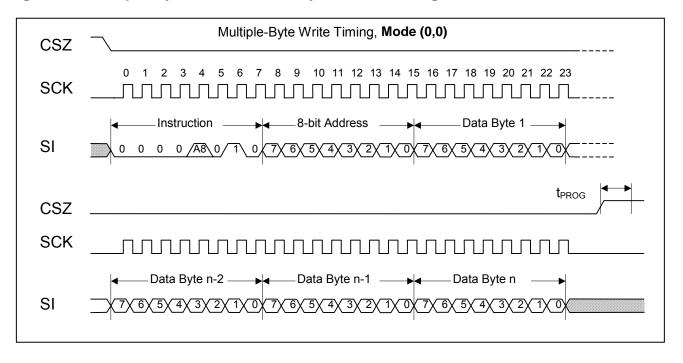

#### SPI INTERFACE

The DS28DG02 is a slave device that communicates with its master, a microcontroller, through the serial SPI interface. This interface uses the signals CSZ (chip select), SCK (bit transfer clock), SI (serial input), and SO (serial output). Common to SPI devices is a WPZ input (write protect), which can protect the nonvolatile bits in the SPI Status register from inadvertent changes.

## **Pin Description**

#### **Chip Select (CSZ)**

A low level on the CSZ pin selects the device; a high level deselects the device. A low-to-high transition on CSZ after a valid EEPROM write sequence initiates an internal programming cycle. A programming cycle already initiated or in progress will be completed, regardless of the CSZ input signal. When the device is deselected, SO goes to the high-impedance state, allowing multiple parts to share the same SPI bus. After powerup, a low level on CSZ is required prior to any sequence being initiated. The CSZ pin must remain low while the DS28DG02 is receiving or transmitting data.

#### Serial Clock (SCK)

The SCK is used to synchronize the communication between a master and the DS28DG02. Instructions, addresses, or data present on the SI pin are latched on the rising edge of the clock input, while data on the SO pin is updated after the falling edge of the clock input.

#### Serial Input (SI)

The SI pin is used to transfer data into the device. It receives instructions, addresses, and data. Data is latched on the rising edge of the serial clock.

## Serial Output (SO)

The SO pin is used to transfer data out of the DS28DG02. During a read cycle, data is shifted out on this pin after the falling edge of the serial clock.

#### Write Protect (WPZ)

The WPZ pin, if enabled, prevents writes to the nonvolatile bits in the SPI Status register. As factory default, the WPZ pin function is disabled. This allows the user to install the DS28DG02 in a system with WPZ pin grounded and still being able to write to the Status register. For more details see *Principles of Operation*.

## **SPI Modes and Bit Timing**

The SPI protocol defines communication in full bytes with the MS bit being transmitted first. Every SPI communication sequence begins with at least one byte written to the slave device. The first byte that the slave receives from the master is understood as an instruction. Depending on the instruction the slave may need more bytes, e.g., address and data; for a read function, after having received the instruction and address, the slave starts sending data to the master.