19-1288; Rev 1; 9/08

EVALUATION KIT AVAILABLE

# Low-Power Audio CODEC with **DirectDrive Headphone Amplifiers**

## **General Description**

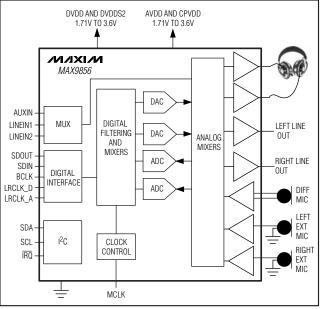

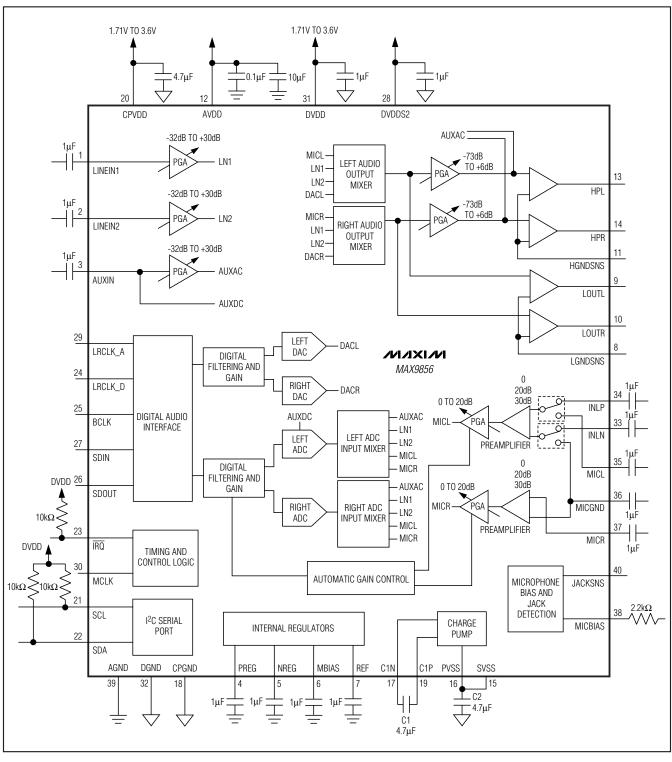

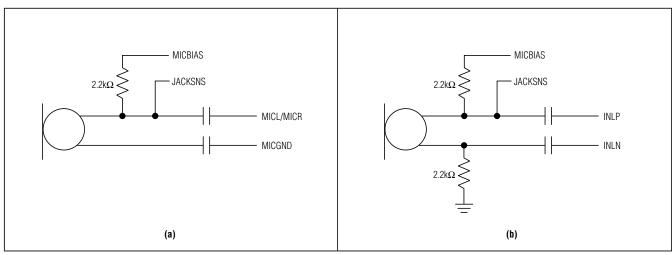

The MAX9856 is a high-performance, low-power stereo audio CODEC designed for MP3, personal media players (PMPs), or other portable multimedia devices. Using on-board stereo DirectDrive® headphone amplifiers, the CODEC can output 30mW into stereo  $32\Omega$ headphones while operating from a single 1.8V power supply. Very low 9mW playback power consumption makes it an ideal choice for battery-powered applications. The MAX9856 provides microphone input amplifiers, plus flexible input selection, signal mixing, and automatic gain control (AGC). Comprehensive loadimpedance sensing allows the MAX9856 to autodetect most common audio and audio/video headset and jack plug types.

Outputs include stereo DirectDrive line outputs and DirectDrive headphone amplifiers. The stereo ADC can convert audio signals from either internal or external microphones that can be configured for single-ended or differential signal inputs. Line inputs can be configured as stereo, differential, or mono and fed through one channel of the microphone path. The analog inputs selected can be gain ranged or mixed with other input sources prior to conversion to digital. The ADC path also features programmable digital highpass filters to remove DC offset voltages and wind noise.

The MAX9856 supports all common sample rates from 8kHz to 48kHz in both master and slave mode. The serial digital audio interfaces support a variety of formats including I<sup>2</sup>S, left-justified, and PCM modes.

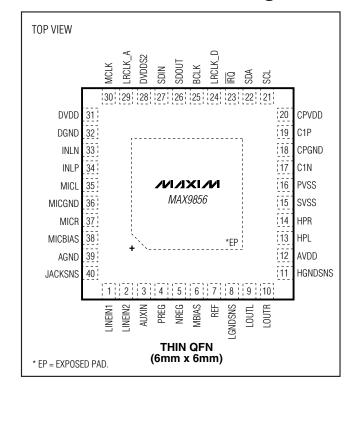

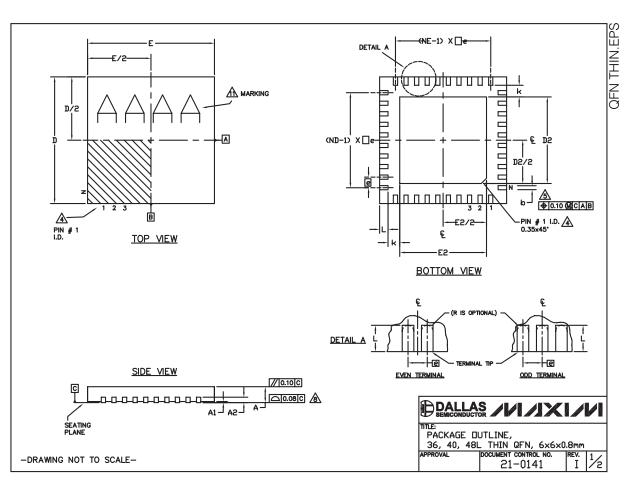

The MAX9856 uses a thermally efficient, space-saving 40-pin, 6mm x 6mm x 0.8mm TQFN package.

#### **Features**

- 1.71V to 3.6V Single-Supply Operation

- Stereo 30mW DirectDrive Headphone Amplifier

- Stereo 1V<sub>RMS</sub> DirectDrive Line Outputs (V<sub>DD</sub> = 1.8V) and Stereo Line Inputs

- Low-Noise Stereo and Mono Differential **Microphone Inputs with Automatic Gain Control** and Noise Quieting

- ♦ 9mW Playback Power Consumption (V<sub>DD</sub> = 1.8V)

- 91dB 96kHz 18-Bit Stereo DAC

- 85dB 48kHz 18-Bit Stereo ADC

- Supports Any Master Clock Frequency from 10MHz to 60MHz

- ♦ ADCs and DACs Can Run at Independent Sample **Rates**

- Flexible Audio Mixing and Volume Control

- Clickless/Popless Operation

- Headset Detection Logic

- ♦ I<sup>2</sup>C Control Interface

#### **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX9856ETL+ | -40°C to + 85°C | 40 TQFN-EP* |

+Denotes a lead-free/RoHS-compliant package.

\*EP = Exposed pad.

## Simplified Block Diagram

##

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642. or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

(Voltages with respect to AGND.)

| (vollages with respect to AGNL | /.)                                  |

|--------------------------------|--------------------------------------|

| AVDD, DVDD, DVDDS2, CPVDI      | D0.3V to +4V                         |

| PVSS, SVSS                     | Capacitor connection only            |

|                                | 0.3V to +0.3V                        |

| HPL, HPR                       | .(SVSS - 0.3V) to (AVDD + 0.3V)      |

|                                | D0.3V to +0.3V                       |

|                                | .(SVSS - 0.3V) to (AVDD + 0.3V)      |

| LOUTL, LOUTR                   | .(SVSS - 0.3V) to (AVDD + 0.3V)      |

|                                | -2V to +2V                           |

| MICL, MICR, INLP, INLM, INRM   | l2V to +2V                           |

| C1N(F                          | PVSS - $0.3V$ ) to (CPGND + $0.3V$ ) |

| C1P(CF                         | PGND - 0.3V) to (CPVDD + 0.3V)       |

| PREG, REF, MBIAS, MICBIAS      | 0.3V to (AVDD + 0.3V)                |

| NREG                           | (SVSS - 0.3V) to +0.3V               |

| MCLK                           | -0.3V to +4V                         |

| SDA, SCL, IRQ                  | -0.3V to +4V                         |

|                                |                                      |

| LRCLK_A, LRCLK_D, BCLK,<br>SDIN, SDOUT0.3V to (DVDDS2 + 0.3V)<br>Continuous Current Into/Out of HPR/HPL/ |

|----------------------------------------------------------------------------------------------------------|

| LOUTL/LOUTR                                                                                              |

| CPVDD/CPGND/C1P/C1N/PVSS                                                                                 |

| Any Other Pin20mA                                                                                        |

| Duration of HPR/HPL/LOUTL/LOUTR Short Circuit                                                            |

| to AVDD/AGND/CPVDD/CPGNDContinuous                                                                       |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                    |

| 40-Pin TQFN (derate 26.3mW/°C above +70°C,                                                               |

| single-layer board)2105mW                                                                                |

| 40-Pin TQFN (derate 37mW/°C above +70°C,                                                                 |

| multilayer board)                                                                                        |

| Operating Temperature Range40°C to +85°C                                                                 |

| Storage Temperature Range65°C to +150°C                                                                  |

| Lead Temperature (soldering, 10s)+300°C                                                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, C<sub>REF</sub> = C<sub>MBIAS</sub> = C<sub>PREG</sub> = C<sub>NREG</sub> = 1 $\mu$ F, A<sub>VPRE</sub> = +20dB, C<sub>MICBIAS</sub> = 1 $\mu$ F, A<sub>VMIGPGA</sub> = 0dB, MCLK = 11.2896MHz, DRATE = 00, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                     | SYMBOL | CONDITIO                                                        | NS              | MIN  | ТҮР  | МАХ  | UNITS |

|-------------------------------|--------|-----------------------------------------------------------------|-----------------|------|------|------|-------|

| Supply Voltage Range          |        | AVDD = CPVDD (inferred<br>PSRR)                                 | from HP output  | 1.71 | 1.80 | 3.60 | V     |

|                               |        | DVDD, DVDDS2 (inferred to performance tests)                    | from CODEC      | 1.71 | 1.80 | 3.60 | V     |

|                               |        | DAC playback mode                                               | IAVDD + ICPVDD  |      | 2.9  | 5.1  |       |

|                               |        | $(f_S = 44.1 \text{kHz})$ analog                                | IDVDD + IDVDDS2 |      | 2.3  |      |       |

|                               |        | Line-only playback mode                                         | IAVDD + ICPVDD  |      | 2.9  | 4.3  |       |

|                               |        | (DAC/ADC disabled)                                              | IDVDD + IDVDDS2 |      | 0.14 | 0.20 |       |

|                               |        | DAC + line input<br>playback mode<br>(f <sub>S</sub> = 44.1kHz) | IAVDD + ICPVDD  |      | 3.9  | 5.4  |       |

|                               |        |                                                                 | IDVDD + IDVDDS2 |      | 2.3  | 3.5  | 1     |

| Total Supply Current (Note 2) | IVDD   | Full operation, fs =<br>44.1kHz (DAC + ADC +                    | IAVDD + ICPVDD  |      | 11.0 | 15.5 | mA    |

|                               |        | LINEIN + MIC + AUXIN)                                           | IDVDD + IDVDDS2 |      | 3.7  | 4.5  | -     |

|                               |        | DAC playback, fs =<br>44.1kHz mono ADC                          | IAVDD + ICPVDD  |      | 6.6  | 9.1  |       |

|                               |        | record $f_S = 8kHz$                                             | IDVDD + IDVDDS2 |      | 2.8  | 3.5  |       |

|                               |        | ADC record,                                                     | IAVDD + ICPVDD  |      | 7.8  | 10.5 |       |

|                               |        | $f_S = 44.1 \text{kHz}$                                         | IDVDD + IDVDDS2 |      | 2.3  | 3.5  |       |

|                               |        | IAVDD + ICPVDD                                                  |                 |      | 2.2  | 10   |       |

| Shutdown Supply Current       |        | IDVDD + IDVDDS2                                                 |                 |      | 0.6  | 10   | μA    |

| Shutdown to Full Operation    |        |                                                                 |                 |      | 50   |      | ms    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu F, C2 = 4.7\mu F, C_{REF} = C_{MBIAS} = C_{PREG} = C_{NREG} = 1\mu F, A_{VPRE} = +20dB, C_{MICBIAS} = 1\mu F, A_{VMICPGA} = 0dB, MCLK = 11.2896MHz, DRATE = 00, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER                        | SYMBOL             | CONDITIONS                                         |                                                      | MIN | ТҮР      | MAX | UNITS |  |

|----------------------------------|--------------------|----------------------------------------------------|------------------------------------------------------|-----|----------|-----|-------|--|

| STEREO DAC (Note 3)              |                    | •                                                  |                                                      |     |          |     | •     |  |

| Gain Error                       |                    |                                                    |                                                      |     | ±1       | ±5  | %     |  |

| Channel Gain Mismatch            |                    |                                                    |                                                      |     | ±1       |     | %     |  |

| DAC DYNAMIC SPECIFICATIO         | NS                 |                                                    |                                                      |     |          |     |       |  |

|                                  |                    | f <sub>S</sub> = 44.1kHz, A-weighte                | ed, DRATE = 10                                       | 80  | 91       |     |       |  |

| Dynamic Range (Note 4)           |                    | fs = 8kHz to 96kHz,                                | DRATE = 00                                           |     | 87       |     | dB    |  |

|                                  |                    | A-weighted                                         | DRATE =10                                            |     | 91       |     |       |  |

| Total Harmonic Distortion        | THD                | $f_{IN} = 1$ kHz, $f_{S} = 8$ kHz to               | 96kHz, 0dBFS                                         |     | 82       |     | dB    |  |

| Signal to Naisa Datia            | SNR                | f <sub>S</sub> = 8kHz to 96kHz,                    | DRATE = 00                                           |     | 87       |     | dB    |  |

| Signal-to-Noise Ratio            | SINK               | A-weighted (Note 5)                                | DRATE = 10                                           |     | 91       |     | uв    |  |

| Crosstalk                        |                    | Driven channel at -1dBF<br>f <sub>S</sub> = 8kHz   | FS, f <sub>IN</sub> = 1kHz,                          |     | 78       |     | dB    |  |

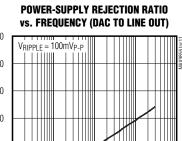

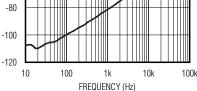

|                                  | 5055               | f = 217Hz, VRIPPLE = 10                            | 0mV, A <sub>VPGA</sub> = 0dB                         |     | 93       |     |       |  |

| Power-Supply Rejection Ratio     | PSRR               | $f = 10 \text{kHz}, \text{V}_{\text{RIPPLE}} = 10$ | $V_{RIPPLE} = 100 \text{mV}, A_{VPGA} = 0 \text{dB}$ |     | 60       |     | dB    |  |

| DAC DIGITAL FILTER (8x inter     | polation, FIR      | (f <sub>S</sub> = 7.8kHz to 50kHz))                |                                                      |     |          |     | •     |  |

| Passband Cutoff                  | fP                 | -0.2dB from peak                                   |                                                      |     | 0.44     |     | fs    |  |

| Passband Ripple                  |                    | f < 0.44 x fs                                      |                                                      |     | ±0.1     |     | dB    |  |

| Stopband Cutoff                  | fs                 |                                                    |                                                      |     | 0.58     |     | fs    |  |

| Stopband Attenuation             |                    | f > fs                                             |                                                      |     | 58       |     | dB    |  |

| Attenuation at fs/2              |                    |                                                    |                                                      |     | -6.02    |     | dB    |  |

| DAC DIGITAL FILTER (4x inter     | polation, FIR      | (f <sub>S</sub> = 50kHz to 100kHz))                |                                                      |     |          |     |       |  |

| Passband Cutoff                  | fP                 | -0.2dB from peak                                   |                                                      |     | 0.24     |     | fs    |  |

| Passband Ripple                  |                    | f < 0.23 x fs                                      |                                                      |     | ±0.1     |     | dB    |  |

| Stopband Cutoff                  | fs                 |                                                    |                                                      |     | 0.5      |     | fS    |  |

| Stopband Attenuation             |                    | f > fs                                             |                                                      |     | 54       |     | dB    |  |

| Attenuation at f <sub>S</sub> /2 |                    |                                                    |                                                      |     | -60      |     | dB    |  |

| DAC HIGHPASS FILTER              |                    |                                                    |                                                      |     |          |     |       |  |

|                                  |                    | DACHP = 000                                        |                                                      |     | Disabled |     |       |  |

|                                  |                    | DACHP = 001; LRCLK/1                               | 1598                                                 |     | 28       |     |       |  |

|                                  |                    | DACHP = 010; LRCLK/7                               | 798                                                  |     | 55       |     |       |  |

| -3dB Corner Frequency            |                    | DACHP = 011; LRCLK/3                               | 398                                                  |     | 111      |     |       |  |

| $(f_{S} = 44.1 \text{kHz})$      | HP <sub>FILT</sub> | DACHP = 100; LRCLK/1                               | 197                                                  |     | 224      |     | Hz    |  |

|                                  |                    | DACHP = 101; LRCLK/9                               | 97                                                   |     | 455      |     |       |  |

|                                  |                    | DACHP = 110; LRCLK/4                               | 17                                                   |     | 938      |     |       |  |

|                                  |                    | DACHP = 111; LRCLK/2                               | 22                                                   |     | 2004     |     | 1     |  |

| DC Attenuation                   | DCATTEN            | DACHP ≠ 000                                        |                                                      |     | 60       |     | dB    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, CREF = C<sub>MBIAS</sub> = CPREG = CNREG = 1 $\mu$ F, AVPRE = +20dB, C<sub>MICBIAS</sub> = 1 $\mu$ F, AVMICPGA = 0dB, MCLK = 11.2896MHz, DRATE = 00, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                    | SYMBOL             | CONDITIONS                                                             | MIN | TYP      | MAX | UNITS |  |

|------------------------------|--------------------|------------------------------------------------------------------------|-----|----------|-----|-------|--|

| STEREO ADC (Note 6)          |                    |                                                                        | •   |          |     |       |  |

| Gain Error                   |                    |                                                                        |     | ±1       | ±5  | %     |  |

| Full-Scale Conversion        | 0dBFS              | f <sub>IN</sub> = 1kHz, line input PGA = 0dB                           |     | 2        |     | VP-P  |  |

| Channel Gain Mismatch        |                    |                                                                        |     | ±1       |     | %     |  |

| ADC DYNAMIC SPECIFICATIO     | NS                 | ·                                                                      |     |          |     |       |  |

|                              |                    | $f_S = 8$ kHz to 32kHz, BW = 22Hz to $f_S/2$                           |     | 80       |     |       |  |

| Dynamic Range (Note 4)       |                    | $f_S = 44.1$ kHz, BW = 22Hz to 20kHz,<br>A-weighted                    | 78  | 84       |     | dB    |  |

|                              |                    | $f_S = 48$ kHz, BW = 22Hz to 20kHz,<br>A-weighted                      |     | 85       |     |       |  |

| <b>T</b>                     | 7110               | 1kHz, 0dBFS, f <sub>S</sub> = 8kHz                                     |     | -63      |     | 10    |  |

| Total Harmonic Distortion    | THD                | 1kHz, 0dBFS, f <sub>S</sub> = 48kHz                                    |     | -68      |     | dB    |  |

|                              |                    | 1kHz, 0dBFS, $f_S = 8kHz$ , BW = 22Hz to 20kHz, A-weighted             |     | 77       |     |       |  |

| Signal-to-Noise Ratio        | SNR                | 1kHz, 0dBFS, f <sub>S</sub> = 48kHz, BW = 22Hz to<br>20kHz, A-weighted |     | 77       |     | dB    |  |

| Channel Crosstalk            |                    | Driven channel at -1dBFS, $f_{IN} = 1kHz$ , $f_{S} = 8kHz$             |     | 65       |     | dB    |  |

|                              |                    | V <sub>AVDD</sub> = 1.71V to 3.6V                                      | 60  | 100      |     |       |  |

| Power-Supply Rejection Ratio | PSRR               | f = 1kHz, V <sub>RIPPLE</sub> = 100mV                                  | 80  |          |     | dB    |  |

| (Note 7)                     |                    | $f = 10 kHz, V_{RIPPLE} = 100 mV$                                      |     | 50       |     |       |  |

| ADC DIGITAL FILTER PATH      |                    |                                                                        |     |          |     | -     |  |

| Passband Cutoff              | fP                 | -0.2dB from peak                                                       |     | 0.44     |     | fs    |  |

| Passband Ripple              |                    | f < fp                                                                 |     | ±0.1     |     | dB    |  |

| Stopband Cutoff              | fS                 |                                                                        |     | 0.56     |     | fs    |  |

| Stopband Attenuation         |                    | f > fs                                                                 |     | 60       |     | dB    |  |

| Attenuation at fs/2          |                    |                                                                        |     | -6.02    |     | dB    |  |

| ADC HIGHPASS FILTER          |                    |                                                                        |     |          |     |       |  |

|                              |                    | ADCHP = 000                                                            |     | Disabled |     |       |  |

|                              |                    | ADCHP = 001; LRCLK/1598                                                |     | 28       |     |       |  |

|                              |                    | ADCHP = 010; LRCLK/798                                                 |     | 55       |     |       |  |

| -3dB Corner Frequency        |                    | ADCHP = 011; LRCLK/398                                                 |     | 111      |     | Hz    |  |

| $(f_{S} = 44.1 \text{kHz})$  | HP <sub>FILT</sub> | ADCHP = 100; LRCLK/197                                                 |     | 224      |     |       |  |

|                              |                    | ADCHP = 101; LRCLK/97                                                  |     | 455      |     | ]     |  |

|                              |                    | ADCHP = 110; LRCLK/47                                                  |     | 938      |     | ]     |  |

|                              |                    | ADCHP = 111; LRCLK/22                                                  | İ   | 2004     |     | 1     |  |

| DC Attenuation               | DCATTEN            | ADCHP anything other than 000                                          |     | 90       |     | dB    |  |

| DC Output Offset             |                    | ADCHP = 000                                                            |     | -40      |     | dBFS  |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu F, C2 = 4.7\mu F, C_{REF} = C_{MBIAS} = C_{PREG} = C_{NREG} = 1\mu F, A_{VPRE} = +20dB, C_{MICBIAS} = 1\mu F, A_{VMICPGA} = 0dB, MCLK = 11.2896MHz, DRATE = 00, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER                                                                              | SYMBOL          | CONDITIO                                                       | NS                                                                                                        | MIN    | ТҮР  | MAX    | UNITS |

|----------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------|------|--------|-------|

| ADC/DAC DATA RATE ACCURA                                                               | Сү              |                                                                |                                                                                                           |        |      |        |       |

| LRCLK_D and LRCLK_A Output<br>Average Sample Rate Deviation<br>(Master Mode, Any MCLK) |                 | (Note 8)                                                       |                                                                                                           | -0.025 |      | +0.025 | %     |

| LRCLK_D Output Sample Rate<br>Deviation (Master Mode)                                  |                 | PCLK/LRCLK = 1536, 102<br>256, 192, or 128                     | 4, 768, 512, 384,                                                                                         |        | 0    |        | %     |

| LRCLK Input Sample Rate Range                                                          |                 | LRCLK_A, LRCLK_D (DHF                                          | = = 0)                                                                                                    | 7.8    |      | 50     |       |

| (Slave Mode)                                                                           |                 | LRCLK_D (DHF = 1)                                              |                                                                                                           | 15.6   |      | 100    | kHz   |

| LRCLK_D and LRCLK_A PLL<br>Lock Time                                                   | tlock           | Any allowable LRCLK and                                        | PCLK rates                                                                                                |        | 12   | 25     | ms    |

| LRCLK_D and LRCLK_A<br>Acceptable Jitter for Maintaining<br>PLL Lock (All Slave Modes) |                 | nominal for slave PLL mod                                      | Allowable LRCLK period change from<br>nominal for slave PLL mode at any<br>allowable LRCLK and PCLK rates |        |      | ±20    | ns    |

| HEADPHONE AMPLIFIERS                                                                   |                 | ·                                                              |                                                                                                           |        |      |        |       |

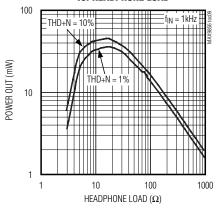

|                                                                                        | Davia           | f = 1kHz, THD < 1%,                                            | $R_L = 16\Omega$                                                                                          |        | 35   |        |       |

| Output Power                                                                           | Pout            | $T_A = +25^{\circ}C$                                           | $R_L = 32\Omega$                                                                                          | 15     | 28   |        | mW    |

| 0dBFS DAC Output Voltage                                                               |                 | +0dB volume setting                                            |                                                                                                           | 3.40   | 3.51 | 3.80   | Vp-p  |

| Line In to HP Out Voltage Gain                                                         |                 | +4.5dB volume setting, 0c                                      | IB PGA setting                                                                                            |        | 1.77 |        | V/V   |

| Output Offset Voltage                                                                  | VOS             | $T_A = +25^{\circ}C$ , -40dB volume                            | e setting                                                                                                 |        | ±0.6 | ±4     | mV    |

| Total Harmonic Distortion Plus                                                         | THD+N           | $R_L=32\Omega,P_OUT=25mW,$                                     | f = 1kHz                                                                                                  |        | 0.03 |        | %     |

| Noise                                                                                  |                 | $R_L=16\Omega,P_{OUT}=25mW,$                                   | f = 1kHz                                                                                                  |        | 0.05 |        | 70    |

| Dynamic Range                                                                          | DR              | +5.5dB volume setting, DA<br>f <sub>S</sub> = 44.1kHz (Note 4) | AC input at                                                                                               | 80     | 91   |        | dB    |

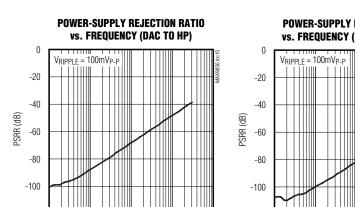

|                                                                                        |                 | V <sub>AVDD</sub> = 1.71V to 3.6V                              |                                                                                                           | 70     | 94   |        |       |

| Power-Supply Rejection Ratio                                                           | PSRR            | $V_{RIPPLE} = 100 mV_{P-P}, f = 2$                             | 17Hz                                                                                                      |        | 80   |        | dB    |

|                                                                                        |                 | $V_{RIPPLE} = 100 mV_{P-P}, f = 1$                             | 0kHz                                                                                                      |        | 50   |        |       |

| Capacitive Drive                                                                       | CL              | No sustained oscillations                                      |                                                                                                           |        | 150  |        | pF    |

| Crosstalk                                                                              |                 | $P_{OUT} = 1.6mW, f = 1kHz,$<br>(HPR to HPL)                   | (HPL to HPR) or                                                                                           |        | 69   |        | dB    |

| Channel Gain Matching                                                                  | AVMATCH         |                                                                |                                                                                                           |        | ±2   |        | %     |

| Click-and-Pop Level                                                                    |                 | Peak voltage,<br>A-weighted, 32 samples                        |                                                                                                           |        | -70  |        | dBV   |

|                                                                                        |                 | per second                                                     | Out of shutdown                                                                                           |        | -70  |        |       |

| LINE AMPLIFIERS                                                                        |                 |                                                                |                                                                                                           |        |      |        |       |

| 0dBFS DAC Output Voltage                                                               |                 |                                                                |                                                                                                           |        | 1.0  |        | VRMS  |

| Line-In to Line-Out Voltage Gain                                                       |                 | 0dB input PGA setting                                          |                                                                                                           | 1.3    | 1.34 | 1.4    | V/V   |

| Output Offset Voltage                                                                  | V <sub>OS</sub> | $T_A = +25^{\circ}C$                                           |                                                                                                           |        | ±0.7 | ±10    | mV    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, CREF = C<sub>MBIAS</sub> = CPREG = C<sub>NREG</sub> = 1 $\mu$ F, A<sub>VPRE</sub> = +20dB, C<sub>MICBIAS</sub> = 1 $\mu$ F, A<sub>VMICPGA</sub> = 0dB, MCLK = 11.2896MHz, DRATE = 00, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                               | SYMBOL                                           | CON                                                                           | CONDITIONS                  |       | ТҮР   | MAX   | UNITS  |

|-----------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------|-------|-------|-------|--------|

| Total Harmonic Distortion Plus<br>Noise | THD+N                                            | $V_{OUT} = 1V_{RMS}, f = 7$                                                   | 1kHz                        |       | 0.024 |       | %      |

| Signal-to-Noise Ratio                   | SNR                                              |                                                                               |                             |       | 98    |       | dB     |

|                                         |                                                  | V <sub>AVDD</sub> = 1.71V to 3.                                               | 6V                          | 70    | 108   |       |        |

| Power-Supply Rejection Ratio            | PSRR                                             | $V_{RIPPLE} = 100 m V_{P-F}$                                                  | p, f = 217Hz                |       | 93    |       | dB     |

|                                         |                                                  | $V_{RIPPLE} = 100 m V_{P-F}$                                                  | p, f = 10kHz                |       | 60    |       | ]      |

| Capacitive Drive                        | CL                                               | No sustained oscilla                                                          | tions                       |       | 150   |       | рF     |

| Crosstalk                               |                                                  | $V_{OUT} = 2V_{P-P}, f = 1k$<br>or (LOUTR to LOUT)                            | kHz, (LOUTL to LOUTR)<br>L) |       | 98    |       | dB     |

| Channel Gain Matching                   | AVMATCH                                          |                                                                               |                             |       | ±2    |       | %      |

| VOLUME CONTROL                          |                                                  |                                                                               |                             | 1     |       |       | 1      |

| Headphone Volume Control<br>Range       |                                                  |                                                                               |                             | -74.0 |       | +5.5  | dB     |

|                                         |                                                  | 5.5dB to 2dB                                                                  |                             |       | 0.5   |       |        |

| Headphone Volume Control Step           |                                                  | +2.5dB to -2dB                                                                |                             |       | 1     |       |        |

| Size                                    |                                                  | -2dB to -46dB                                                                 |                             | 2     |       |       | dB     |

|                                         |                                                  | -46dB to -74dB                                                                | -46dB to -74dB              |       | 4     |       |        |

| Headphone Mute Attenuation              |                                                  | f = 1kHz                                                                      |                             |       | 92    |       | dB     |

| CHARGE PUMP                             |                                                  | •                                                                             |                             |       |       |       |        |

| Charge-Pump Oscillator<br>Frequency     | fosc                                             | $T_A = +25^{\circ}C$                                                          |                             | 600   | 665   | 720   | kHz    |

| MICROPHONE AMPLIFIERS                   |                                                  |                                                                               |                             |       |       |       | •      |

|                                         |                                                  |                                                                               | PALEN/PAREN = 01            | -0.5  | 0     | +0.5  |        |

| Preamplifier Gain                       | AVPRE                                            | MICL or MICR                                                                  | PALEN/PAREN = 10            | 19    | 20    | 21    | dB     |

|                                         |                                                  |                                                                               | PALEN/PAREN = 11            | 28.5  | 30.0  | 31.5  |        |

| MIC PGA Gain                            | Avmicpga                                         | PGAML/R = 0x20                                                                |                             | -0.5  | 0     | +0.5  | dB     |

|                                         | AVIVIICEGA                                       | PGAML/R = 0x00                                                                |                             | 19.5  | 20.0  | 19.5  | uD     |

| MIC PGA Gain Step Size                  |                                                  |                                                                               |                             |       | 1     |       | dB     |

| MIC Mute Attenuation                    |                                                  | f = 1kHz                                                                      |                             |       | 92    |       | dB     |

| Common-Mode Rejection Ratio             | CMRR                                             | INL $\pm$ , V <sub>IN</sub> = 100mV <sub>P-P</sub> at 217Hz,<br>AVPRE = +20dB |                             |       | 73    |       | dB     |

|                                         |                                                  | INL±, MICL or MICF                                                            | $R, A_{VPRE} = +30 dB$      | 4     | 8     | 10    |        |

| MIC Input Resistance                    | INL±, MICL or MICR, A <sub>VPRE</sub> = +20dB 12 |                                                                               | 18                          | 28    | kΩ    |       |        |

|                                         |                                                  | INL±, MICL or MICR, AVPRE = 0dB                                               |                             | 60    | 100   | 160   |        |

| MIC Input Resistance Matching           | RMATCH                                           | INL+ to INL- or MICI                                                          | L/MICR to AGND              |       | 1     |       | %      |

| MIC Input Bias Voltage                  | VCML                                             |                                                                               | VICR, MICL, and AGND        | -0.05 | 0     | +0.05 | V      |

| Input Voltage Noise                     |                                                  | $f = 1 kHz, A_{VPRE} = +$                                                     | -30dB                       |       | 15    |       | nV/√Hz |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu F, C2 = 4.7\mu F, C_{REF} = C_{MBIAS} = C_{PREG} = C_{NREG} = 1\mu F, A_{VPRE} = +20dB, C_{MICBIAS} = 1\mu F, A_{VMICPGA} = 0dB, MCLK = 11.2896MHz, DRATE = 00, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.) (Note 1)$

| PARAMETER                               | SYMBOL    | CONDITIONS                                                                                                                                                               | MIN   | ТҮР      | MAX    | UNITS  |

|-----------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|--------|--------|

|                                         |           | $A_{VPRE} = 0$ dB, $A_{VMICPGA} = 0$ dB,<br>$V_{IN} = 500$ m $V_{P-P}$ , f = 1kHz, A-weighted                                                                            |       | 0.04     |        |        |

| Total Harmonic Distortion Plus<br>Noise | THD+N     | $A_{VPRE} = +20$ dB, $A_{VMICPGA} = 0$ dB,<br>$V_{IN} = 50$ mV <sub>P-P</sub> , f = 1kHz, A-weighted                                                                     |       | 0.08     |        | %      |

|                                         |           | $A_{VPRE} = +30$ dB, $A_{VMICPGA} = 0$ dB,<br>$V_{IN} = 18$ mV <sub>P-P</sub> , f = 1kHz, A-weighted                                                                     |       | 0.08     |        |        |

|                                         |           | $V_{AVDD} = 1.71V$ to 3.6V, $T_A = +25^{\circ}C$                                                                                                                         | 79    | 80       |        |        |

| MIC Power-Supply Rejection              | PSRR      | VRIPPLE = 100mV at 1kHz, input referred                                                                                                                                  |       | 80       |        | dB     |

| Ratio                                   |           | VRIPPLE = 100mV at 10kHz, input referred                                                                                                                                 |       | 50       |        |        |

| MICROPHONE BIAS                         | •         | •                                                                                                                                                                        |       |          |        |        |

|                                         |           | V <sub>AVDD</sub> = 1.8V (MBSEL = 0 register setting)                                                                                                                    | 1.4   | 1.5      | 1.6    |        |

| MICBIAS Output Voltage                  | VMICBIAS  | V <sub>AVDD</sub> = 3.0V (MBSEL = 1 register setting)                                                                                                                    | 2.3   | 2.4      | 2.5    | V      |

| MICBIAS Load Regulation                 |           | I <sub>MICBIAS</sub> = 0 to 2mA                                                                                                                                          |       | 0.8      | 10     | Ω      |

| MICBIAS Capacitive Load                 |           | Minimum capacitive load                                                                                                                                                  |       | 1        |        | μF     |

| MICBIAS Short-Circuit Current           |           | To GND                                                                                                                                                                   |       | 14       |        | mA     |

| MICBIAS Power-Supply Rejection          | 0000      | $V_{AVDD} = 1.71V$ to 3.6V, MBSEL = 0,<br>T <sub>A</sub> = +25°C                                                                                                         | 75    | 86       |        | Ē      |

| Ratio                                   | PSRR      | VRIPPLE = 100mV at 1kHz                                                                                                                                                  |       | 86       |        | dB     |

|                                         |           | VRIPPLE = 100mV at 10kHz                                                                                                                                                 |       | 76       |        |        |

|                                         | VNOISEMIC | f = 10Hz to 20kHz                                                                                                                                                        |       | 3        |        | μVrms  |

| MICBIAS Noise Voltage                   | BIAS      | MBSET = 0  or  1 $f = 1  kHz$                                                                                                                                            |       | 20       |        | nV/√Hz |

| AUTOMATIC GAIN CONTROL                  |           | · · · ·                                                                                                                                                                  |       |          |        |        |

| Threshold Level                         |           | Set by AGCSTH[3:0]                                                                                                                                                       | -3    |          | -18    | dB     |

| Attack Time                             |           | Set by AGCATK[1:0]                                                                                                                                                       | 3     |          | 200    | ms     |

| Release Time                            |           | Set by AGCRLS[2:0]                                                                                                                                                       | 0.078 |          | 10.000 | S      |

| Hold Time                               |           | Set by AGCHLD[1:0]                                                                                                                                                       | 50    |          | 400    | ms     |

|                                         |           | A <sub>VPRE</sub> = +30dB                                                                                                                                                |       | 30 to 50 |        |        |

| Gain Adjustment Range                   |           | A <sub>VPRE</sub> = +20dB                                                                                                                                                |       | 20 to 40 |        | dB     |

|                                         |           | A <sub>VPRE</sub> = 0dB                                                                                                                                                  |       | 0 to 20  |        |        |

| ADC LOW-LEVEL QUIETING                  | •         | •                                                                                                                                                                        |       |          |        |        |

| NG Attack and Release Time              |           | Full 12dB quieting at 1dB of<br>attenuation/(gain) for every 2dB<br>decrease/(increase) of signal level<br>(immediate release if PGA < 20dB gain<br>when AGC is enabled) |       | 0.5      |        | S      |

| NG Threshold Level                      |           | ANTH[3:0] setting range (AGC off) (AGC on<br>adjusts these values by 20dB since low-<br>level signals cause maximum AGC gain in<br>the PGA)                              | -64   |          | -28    | dB     |

| NG Attenuation                          |           | 1dB of attenuation for every 2dB signal amplitude decrease from NG threshold                                                                                             | 0     |          | 12     | dB     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, CREF = C<sub>MBIAS</sub> = CPREG = C<sub>NREG</sub> = 1 $\mu$ F, A<sub>VPRE</sub> = +20dB, C<sub>MICBIAS</sub> = 1 $\mu$ F, A<sub>VMICPGA</sub> = 0dB, MCLK = 11.2896MHz, DRATE = 00, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                   | SYMBOL              | CONDITIONS                                            | MIN               | ТҮР               | MAX               | UNITS |

|-------------------------------------------------------------|---------------------|-------------------------------------------------------|-------------------|-------------------|-------------------|-------|

| LINEIN1/LINEIN2 INPUTS                                      | 1                   |                                                       | 1                 |                   |                   |       |

| Line Input Full-Scale Input<br>Voltage                      | 0dBFS               |                                                       |                   | 2                 |                   | VP-P  |

| Input DC Bias Voltage                                       |                     |                                                       |                   | 0                 |                   | V     |

| Line Input Resistance                                       | RIN                 | PGA = 0dB (Note 9)                                    | 12                | 21                |                   | kΩ    |

| Crosstalk                                                   |                     | LINEIN1 to LINEIN2 or LINEIN2 to<br>LINEIN1, f = 1kHz |                   | 97                |                   | dB    |

| Line Channel-to-Channel Gain<br>Matching                    | AV <sub>MATCH</sub> |                                                       |                   | ±2                |                   | %     |

| PGA Gain Range                                              |                     |                                                       | -32               |                   | +30               | dB    |

| PGA Gain Step Size                                          |                     | -32dB to +30dB                                        |                   | 2                 |                   | dB    |

| AUXIN INPUT                                                 |                     |                                                       |                   |                   |                   |       |

| AUXIN Full-Scale Input Voltage                              | 0dBFS               | AUXDC = 0                                             |                   | 2                 |                   | VP-P  |

| Input DC Voltage Range                                      |                     | AUXDC = 1                                             | 0                 |                   | 1                 | V     |

| Input DC Bias Voltage                                       |                     | AUXDC = 0                                             |                   | 0                 |                   | V     |

|                                                             | Dut                 | AUXDC = 0                                             | 12                | 21                |                   | kΩ    |

| AUXIN Input Resistance                                      | RIN                 | AUXDC = 1                                             |                   | 100               |                   | MΩ    |

| Line Channel-to-Channel Gain<br>Matching                    | AVMATCH             |                                                       |                   | ±2                |                   | %     |

| PGA Gain Range                                              |                     |                                                       | -32               |                   | +30               | dB    |

| PGA Gain Step Size                                          |                     | -32dB to +30dB                                        |                   | 2                 |                   | dB    |

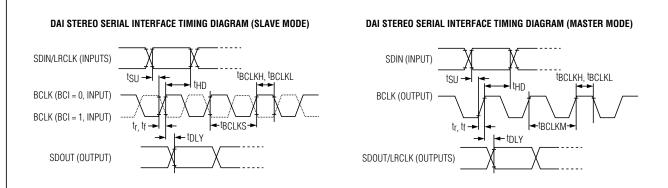

| JACK SENSE OPERATION (EN                                    | [2:0] = 000)        |                                                       |                   |                   |                   |       |

| JACKSNS High Threshold<br>(JKMIC)                           | VTH1                | $T_A = +25^{\circ}C$                                  | 0.92 x<br>MICBIAS | 0.95 x<br>MICBIAS | 0.98 x<br>MICBIAS | V     |

| JACKSNS Deglitch Period<br>(JKMIC)                          | <sup>t</sup> GLITCH | Pulses shorter than $t_{GLITCH}$ are eliminated       |                   | 12                |                   | ms    |

| JACKSNS Voltage (JKMIC)                                     |                     | JDETEN = 1                                            |                   | AVDD              |                   | V     |

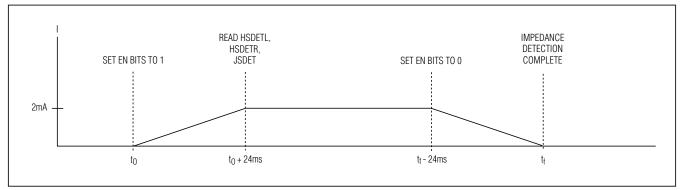

| HEADSET IMPEDANCE DETEC                                     | T MODE (EN          | v[2:0] = 111)                                         |                   |                   |                   |       |

| JACKSNS/HPL/HPR High<br>Threshold<br>(JSDET/ HSDETL/HSDETR) | V <sub>TH2</sub>    | HPL/HPR disabled                                      | 0.32              | 0.40              | 0.48              | V     |

| JACKSNS/HPL/HPR Low<br>Threshold<br>(JSDET/HSDETL/HSDETR)   | V <sub>TH3</sub>    | HPL/HPR disabled                                      | 0.075             | 0.100             | 0.125             | V     |

| JACKSNS/HPL/HPR Sense<br>Current<br>(JSDET/HSDETL/HSDETR)   | I <sub>SNS</sub>    | HPL/HPR disabled                                      | 1.7               | 2.0               | 2.3               | mA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, CREF = CMBIAS = CPREG = CNREG = 1 $\mu$ F, AVPRE = +20dB, CMICBIAS = 1 $\mu$ F, AVMICPGA = 0dB, MCLK = 11.2896MHz, DRATE = 00, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                   | SYMBOL           | CONDITIONS    | MIN            | ТҮР            | MAX             | UNITS |  |  |  |

|---------------------------------------------|------------------|---------------|----------------|----------------|-----------------|-------|--|--|--|

| SLEEP MODE (JDETEN = 1, SHDNB = 0)          |                  |               |                |                |                 |       |  |  |  |

| JACKSNS/HPL Resistance                      | R <sub>PU</sub>  | MICBIAS = GND | 400            | 1000           |                 | kΩ    |  |  |  |

| JACKSNS/HPL Sense Voltage                   | V <sub>PU</sub>  |               |                | AVDD           |                 | V     |  |  |  |

| JACKSNS/HPL Sleep Threshold<br>(JKSNS/LSNS) | V <sub>TH4</sub> |               | AVDD -<br>0.8V | AVDD -<br>0.4V | AVDD -<br>0.15V | V     |  |  |  |

## DIGITAL INTERFACE ELECTRICAL CHARACTERISTICS

(VDVDD = VDVDDS2 = 1.8V, TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

| PARAMETER                            | SYMBOL                            | CONDITIONS                        | MIN      | ТҮР      | MAX      | UNITS |

|--------------------------------------|-----------------------------------|-----------------------------------|----------|----------|----------|-------|

| MCLK INPUT CHARACTERISTIC            | S                                 | ·                                 | •        |          |          |       |

| Input Voltage High                   | VIH                               |                                   | C        | .7 x DVD | D        | V     |

| Input Voltage Low                    | VIL                               |                                   |          |          | 0.4      | V     |

| Input Leakage Current                | I <sub>IH</sub> , I <sub>IL</sub> |                                   | -10      |          | +10      | μΑ    |

| Input Capacitance                    |                                   |                                   |          | 3        |          | рF    |

| MCLK Input Frequency                 |                                   |                                   | 10       |          | 60       | MHz   |

| MCLK Duty Cycle                      |                                   |                                   | 40       | 50       | 60       | %     |

| Maximum MCLK Input Jitter            |                                   | For guaranteed performance limits |          | 100      |          | psrms |

| DIGITAL INPUTS (BCLK, LRCLK          | _A, LRCLK_                        | D, SDIN, SDA, SCL)                |          |          |          |       |

| Input Voltage High                   | VIH                               |                                   | 0.7 x DV | DD       |          | V     |

| Input Voltage Low                    | VIL                               |                                   |          | 0.3      | 3 x DVDD | V     |

| Input Hysteresis                     |                                   |                                   |          | 200      |          | mV    |

| Input Leakage Current                | I <sub>IH</sub> , I <sub>IL</sub> |                                   | -10      |          | +10      | μA    |

| Input Capacitance                    |                                   |                                   |          | 10       |          | рF    |

| CMOS DIGITAL OUTPUTS (BCL            | K, LRCLK_A,                       | LRCLK_D, SDOUT)                   |          |          |          |       |

| Output Low Voltage                   | V <sub>OL</sub>                   | I <sub>OL</sub> = 3mA             |          |          | 0.4      | V     |

| Output High Voltage                  | VOH                               | I <sub>OH</sub> = 3mA             | DVDD -   | 0.4      |          | V     |

| OPEN-DRAIN DIGITAL OUTPUT            | S (IRQ, SDA)                      |                                   |          |          |          |       |

| Output High Current                  | IOH                               | V <sub>OUT</sub> = DVDD           |          |          | 1        | μΑ    |

| Output Low Voltage                   | V <sub>OL</sub>                   | I <sub>OL</sub> = 3mA             |          |          | 0.4      | V     |

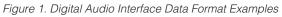

| DIGITAL AUDIO INTERFACE TIN          | IING CHARA                        | CTERISTICS                        |          |          |          |       |

|                                      | <b>t</b> BCLKS                    | Slave operation                   | 75       |          |          | ns    |

| BCLK Cycle Time                      | <b>t</b> BCLKM                    | Master operation                  | 100      | 325      |          | ns    |

| BCLK High Time                       | <b>t</b> BCLKH                    | Slave operation                   | 30       |          |          | ns    |

| BCLK Low Time                        | <b>t</b> BCLKL                    | Master operation                  | 30       |          |          | ns    |

| BCLK or LRCLK_A/D Rise and Fall Time | tr , t <sub>f</sub>               | Master operation, $C_L = 15pF$    | 7        |          |          | ns    |

## DIGITAL INTERFACE ELECTRICAL CHARACTERISTICS (continued)

$(V_{DVDD} = V_{DVDDS2} = 1.8V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                          | SYMBOL              | CONDITIONS                                                                                      | MIN T                   | ΥP | MAX | UNITS |

|----------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|-------------------------|----|-----|-------|

| SDIN or LRCLK_A/D to BCLK<br>Rising Setup Time     | ts∪                 | BCI = 0 (see the <i>I</i> <sup>2</sup> <i>C Register Address Map and Definitions</i> section)   | 30                      |    |     | ns    |

| SDIN or LRCLK_A/D to BCLK<br>Rising Hold Time      | thd                 | BCI = 0 (see the <i>I</i> <sup>2</sup> <i>C Register Address Map and Definitions</i> section)   | 5                       |    |     | ns    |

| SDOUT Delay Time                                   | tDLY                | BCI = 0 (see the $l^2C$ Register Address Map<br>and Definitions section), C <sub>L</sub> = 30pF | 0                       |    | 50  | ns    |

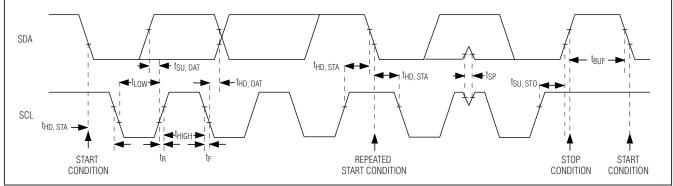

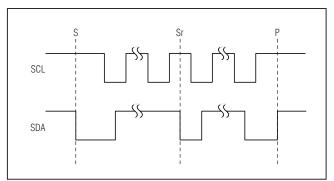

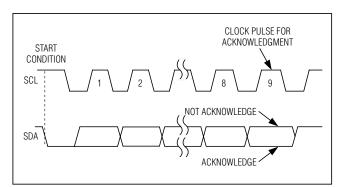

| I <sup>2</sup> C INTERFACE TIMING CHARAC           | TERISTICS           | •                                                                                               |                         |    |     |       |

| Serial-Clock Frequency                             | fSCL                |                                                                                                 | 0                       |    | 400 | kHz   |

| Bus Free Time Between STOP<br>and START Conditions | t <sub>BUF</sub>    |                                                                                                 | 1.3                     |    |     | μs    |

| Hold Time (Repeated) START<br>Condition            | <sup>t</sup> HD,STA |                                                                                                 | 0.6                     |    |     | μs    |

| SCL Pulse Width Low                                | tLOW                |                                                                                                 | 1.3                     |    |     | μs    |

| SCL Pulse Width High                               | thigh               |                                                                                                 | 0.6                     |    |     | μs    |

| Setup Time for a Repeated<br>START Condition       | tsu,sta             |                                                                                                 | 0.6                     |    |     | μs    |

| Data Hold Time                                     | thd,dat             |                                                                                                 | 0                       |    | 900 | ns    |

| Data Setup Time                                    | tsu,dat             |                                                                                                 | 100                     |    |     | ns    |

| SDA and SCL Receiving Rise<br>Time                 | tr                  | (Note 10)                                                                                       | 20 + 0.1C <sub>B</sub>  |    | 300 | ns    |

| SDA and SCL Receiving Fall<br>Time                 | tf                  | (Note 10)                                                                                       | 20 + 0.1C <sub>B</sub>  |    | 300 | ns    |

|                                                    |                     | V <sub>DVDD</sub> = 1.8V (Note 10)                                                              | 20 + 0.1C <sub>B</sub>  |    | 250 |       |

| SDA Transmitting Fall Time                         | tf                  | V <sub>DVDD</sub> = 3.6V (Note 10)                                                              | 20 + 0.05C <sub>B</sub> | 3  | 250 | ns    |

| Setup Time for STOP Condition                      | tsu,sto             |                                                                                                 | 0.6                     |    |     | μs    |

| Bus Capacitance                                    | Cb                  |                                                                                                 |                         |    | 400 | pF    |

| Pulse Width of Suppressed Spike                    | tsp                 | $T_A = +25^{\circ}C$                                                                            | 0                       |    | 50  | ns    |

|                                                    |                     |                                                                                                 |                         |    |     |       |

Note 1: All devices are 100% production tested at room temperature. All temperature limits are guaranteed by design.

**Note 2:** Supply current measurements taken with no applied input signal to line and microphone inputs. A digital zero audio signal used for all digital serial audio inputs. Speaker and headphone outputs are loaded as stated in the global conditions.

**Note 3:** DAC performance measured at headphone outputs.

**Note 4:** Dynamic range measured using the EIAJ method. The input is applied at -60dBFS, f<sub>IN</sub> = 1kHz. The is THD+N referred to 0dBFS.

Note 5: Signal-to-noise ratio measured using an all-zeros input signal, and is relative to 0dB full scale. The DAC is not muted for the SNR measurement.

Note 6: Performance measured from line inputs (unless otherwise noted).

**Note 7:** Microphone amplifiers connected to ADC, microphone inputs AC-grounded.

Note 8: In master-mode operation, the accuracy of the MCLK input proportionally determines the accuracy of the sample clock rate. (V<sub>DVDD</sub> = 1.8V, unless otherwise noted).

**Note 9:** To enable the line input, make sure the desired input is selected by either the audio output mixer or the ADC input mixer. **Note 10:** CB is in pF.

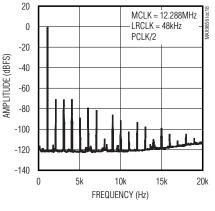

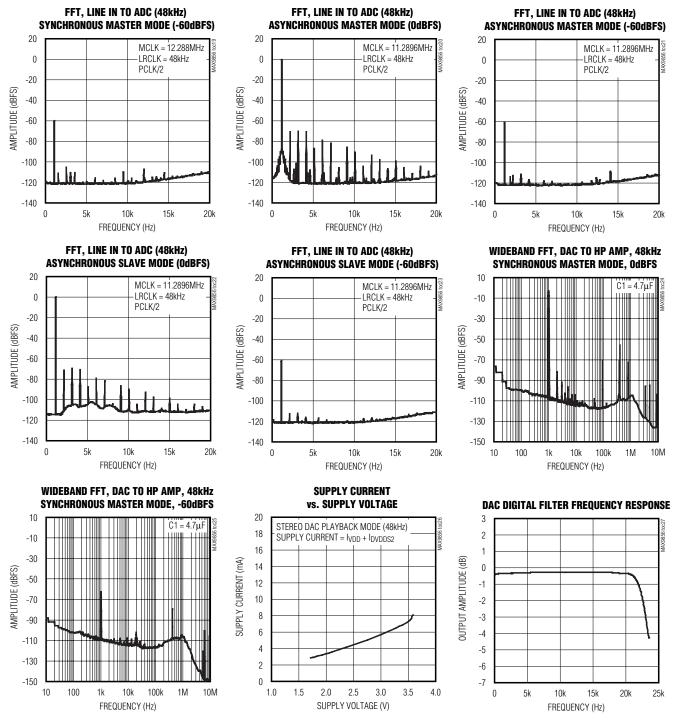

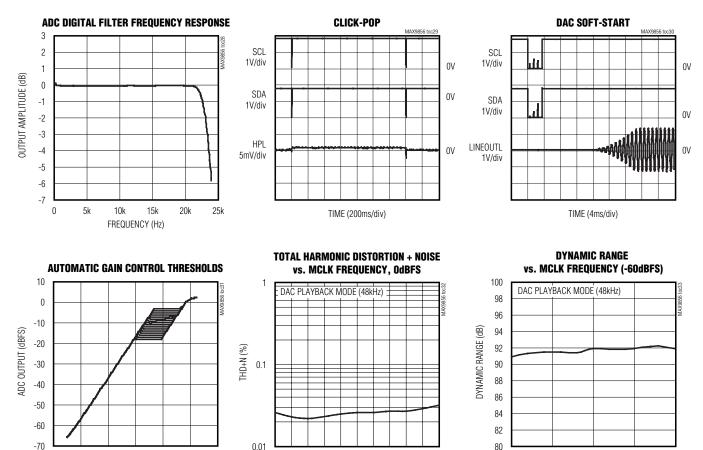

## **Typical Operating Characteristics**

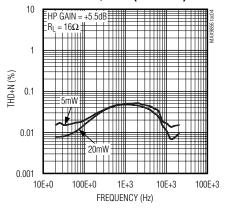

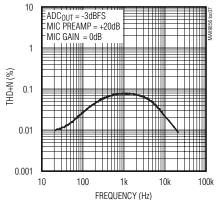

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, C<sub>REF</sub> = C<sub>MBIAS</sub> = C<sub>PREG</sub> = C<sub>NREG</sub> = 1 $\mu$ F, V<sub>AVPRE</sub> = +20dB, C<sub>MICBIAS</sub> = 1 $\mu$ F, V<sub>AVMICPGA</sub> = 0dB, MCLK = 12.288MHz, DRATE = 10, T<sub>A</sub> = +25°C, unless otherwise noted.)

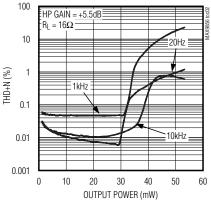

#### TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (DAC TO HP) 100 HP GAIN = +5.5dB $R_L = 32\Omega$ 10 20kHz THD+N (%) 1 1kHz 0.1 0.01 10kHz 0.001 5 10 15 20 25 30 35 40 0 OUTPUT POWER (mW)

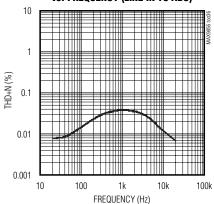

TOTAL HARMONIC DISTORTION + NOISE vs. Frequency (dac to hp)

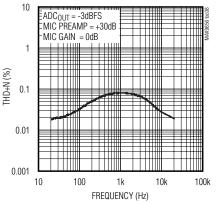

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Intmic to Adc)

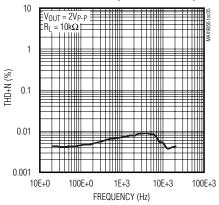

TOTAL HARMONIC DISTORTION + NOISE vs. Frequency (dac to line out)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Intmic to ADC)

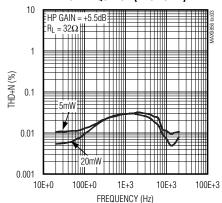

TOTAL HARMONIC DISTORTION + NOISE vs. Frequency (dac to HP)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (line in to ADC)

POWER OUT vs. Headphone Load

-120

10

100

10k

100k

1k

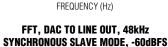

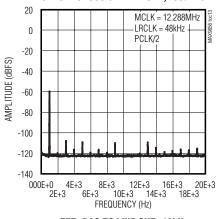

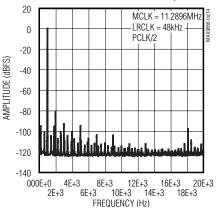

FFT. DAC TO LINE OUT. 48kHz **ASYNCHRONOUS SLAVE MODE, OdBFS**

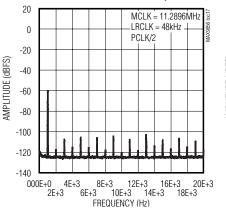

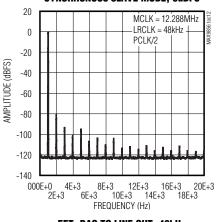

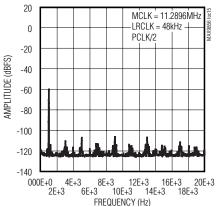

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, CREF = CMBIAS = CPREG = CNRFG =1µF, VAVPRE = +20dB, CMICBIAS = 1µF, VAVMICPGA = 0dB, MCLK = 12.288MHz, DRATE = 10, TA = +25°C, unless otherwise noted.)

**Typical Operating Characteristics (continued)**

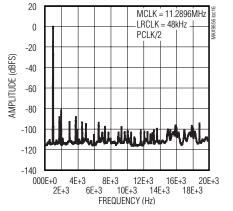

FFT, DAC TO LINE OUT, 48kHz **ASYNCHRONOUS MASTER MODE. OdBFS**

FFT. DAC TO LINE OUT. 48kHz **ASYNCHRONOUS SLAVE MODE, -60dBFS**

FFT, DAC TO LINE OUT, 48kHz SYNCHRONOUS SLAVE MODE, OdBFS

FFT, DAC TO LINE OUT, 48kHz **ASYNCHRONOUS MASTER MODE. -60dBFS**

FFT, LINE IN TO ADC (48kHz) SYNCHRONOUS MASTER MODE (OdBFS)

12

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, CREF = C<sub>MBIAS</sub> = C<sub>PREG</sub> = C<sub>NREG</sub> = 1 $\mu$ F, V<sub>AVPRE</sub> = +20dB, C<sub>MICBIAS</sub> = 1 $\mu$ F, V<sub>AVMICPGA</sub> = 0dB, MCLK = 12.288MHz, DRATE = 10, T<sub>A</sub> = +25°C, unless otherwise noted.)

$(V_{AVDD} = V_{CPVDD} = V_{DVDDS2} = V_{DVDD} = 1.8V, R_{HP} = 32\Omega, R_{LINE} = 10k\Omega, C1 = 4.7\mu$ F, C2 = 4.7 $\mu$ F, CREF = C<sub>MBIAS</sub> = CPREG = C<sub>NREG</sub> = 1 $\mu$ F, V<sub>AVPRE</sub> = +20dB, C<sub>MICBIAS</sub> = 1 $\mu$ F, V<sub>AVMICPGA</sub> = 0dB, MCLK = 12.288MHz, DRATE = 10, T<sub>A</sub> = +25°C, unless otherwise noted.)

14 15 16

FREQUENCY (MHz)

17 18 19 20

10

12

14

FREQUENCY (MHz)

10 11 12 13

16

20

-100 -80

-60

-40

MICROPHONE INPUT (dBV)

-20

0

## **Pin Description**

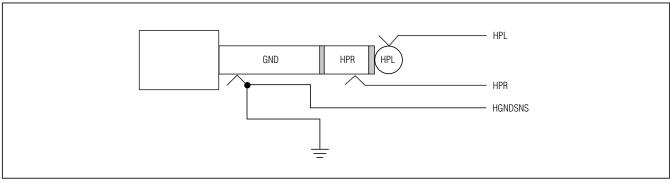

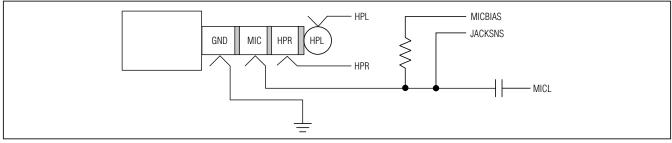

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LINEIN1 | Line 1 Input. AC-couple signal to LINEIN1 with a 1µF capacitor.                                                                                                                                                                                                                                                                                                                              |

| 2   | LINEIN2 | Line 2 Input. AC-couple signal to LINEIN2 with a 1µF capacitor.                                                                                                                                                                                                                                                                                                                              |

| 3   | AUXIN   | Auxiliary Input. Input for beep and sound effect signals or can be used for DC measurements.                                                                                                                                                                                                                                                                                                 |

| 4   | PREG    | Positive Internally Regulated Supply (+1.6V $\pm$ 5%). Bypass to AGND with 1µF capacitor.                                                                                                                                                                                                                                                                                                    |

| 5   | NREG    | Negative Internally Regulated Supply (-1.15V $\pm$ 5%). Bypass to AGND with 1µF capacitor.                                                                                                                                                                                                                                                                                                   |

| 6   | MBIAS   | Internal Microphone Bias Regulator Output (1.23V $\pm$ 5%). Bypass to AGND with a 1µF capacitor.                                                                                                                                                                                                                                                                                             |

| 7   | REF     | Converter Reference (1.23V $\pm$ 5%). Bypass to AGND with a 1µF capacitor.                                                                                                                                                                                                                                                                                                                   |

| 8   | LGNDSNS | Line Output Ground Sense. Feedback path to line-out amplifiers for noise reduction. Connect to the ground pin of the line output jack. Connect directly to AGND, if ground sense is not required.                                                                                                                                                                                            |

| 9   | LOUTL   | Left-Channel Line Output. Ground-referenced DirectDrive output.                                                                                                                                                                                                                                                                                                                              |

| 10  | LOUTR   | Right-Channel Line Output. Ground-referenced DirectDrive output.                                                                                                                                                                                                                                                                                                                             |

| 11  | HGNDSNS | Headphone Ground Sense. Feedback path to headphone amplifiers for noise reduction. Connect to the ground pin of the headphone jack. Connect directly to AGND if ground sense is not required.                                                                                                                                                                                                |

| 12  | AVDD    | Analog Power Supply. Bypass to AGND with 10µF and 0.1µF capacitors.                                                                                                                                                                                                                                                                                                                          |

| 13  | HPL     | Left Headphone DirectDrive Output                                                                                                                                                                                                                                                                                                                                                            |