SBAS513C – JANUARY 2011 – REVISED MARCH 2012

# 12-Bit ANALOG MONITORING AND CONTROL SOLUTION with Multichannel ADC, DACs, and Temperature Sensors

Check for Samples: AMC7812

# FEATURES

.

www.ti.com

- 12, 12-Bit DACs with Programmable Outputs:  $\diamond$  0V to 5V

- ♦ 0V to 12.5V

- DAC Shutdown to User-Defined Level

- 12-Bit, 500kSPS ADC with 16 Inputs: ◇ 16 Single-Ended or Two Differential + 12 Single-Ended

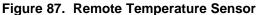

- Two Remote Temperature Sensors:

~ -40°C to +150°C, ±2°C Accuracy

- One Internal Temperature Sensor:

–40°C to +125°C, ±2.5°C Accuracy

- Input Out-of-Range Alarms

- 2.5V Internal Reference

- Eight General-Purpose Input/Outputs

- Configurable I<sup>2</sup>C<sup>™</sup>-Compatible/ SPI<sup>™</sup> Interface with 5V/3V Logic

- Power-Down Mode

- Wide Temperature Range:

–40°C to +105°C

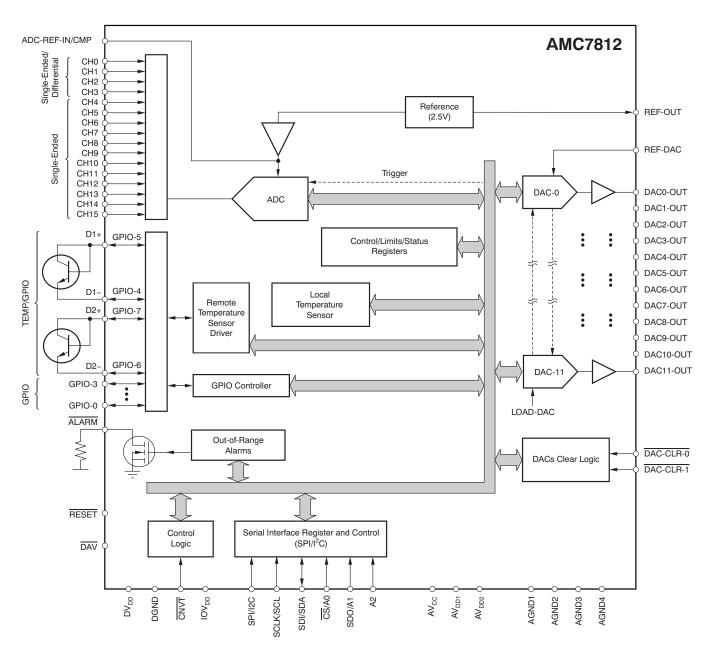

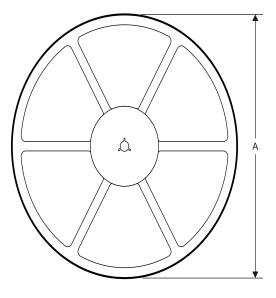

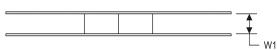

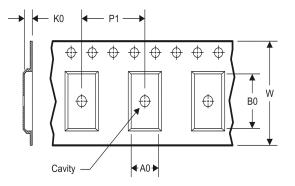

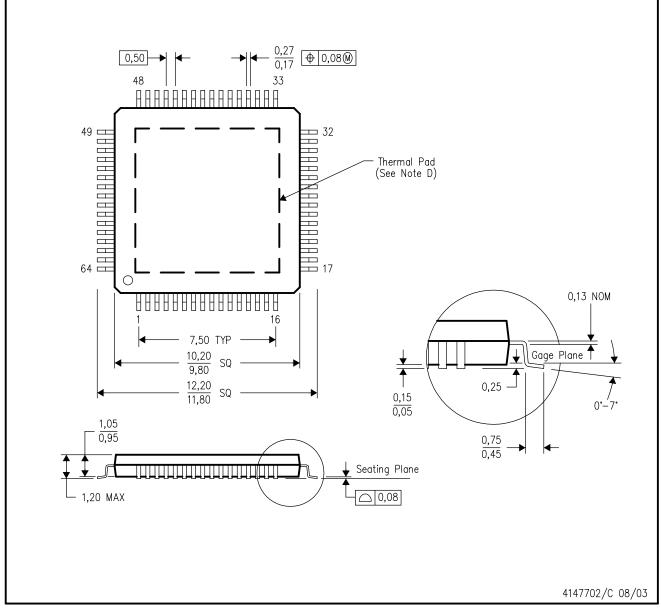

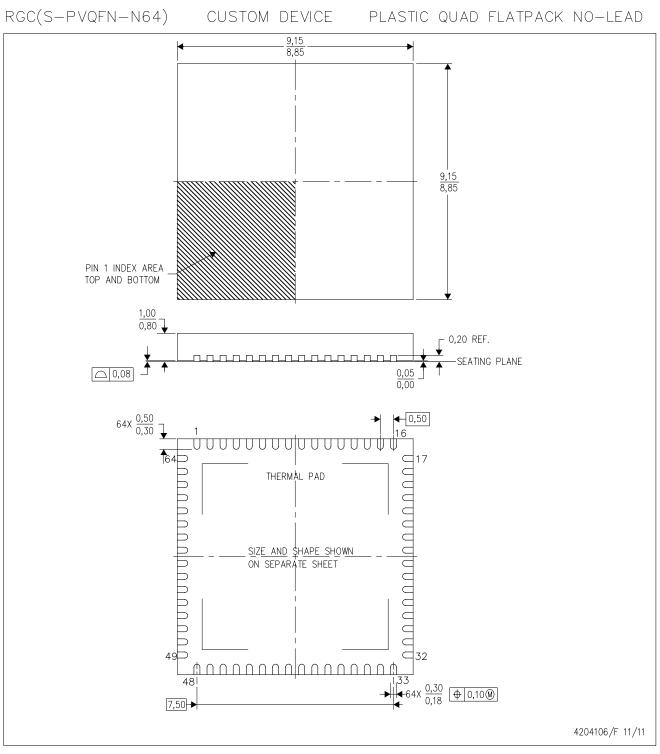

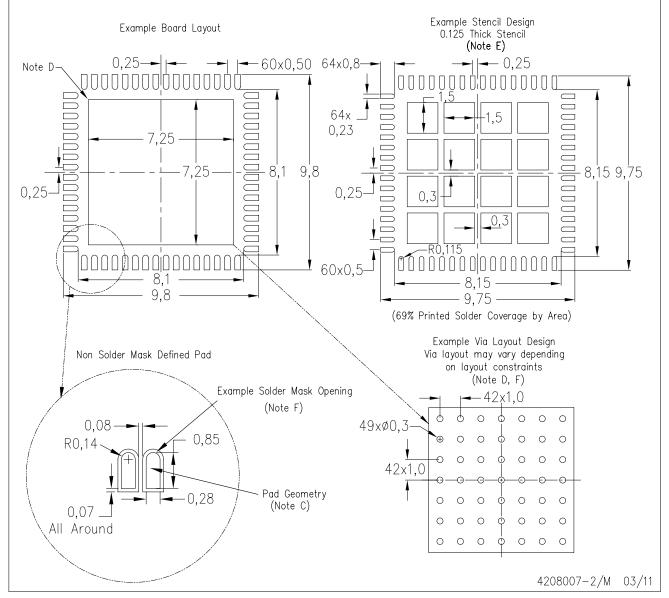

- Small Packages: 9mm x 9mm QFN-64, and 10mm x 10mm HTQFP-64

# **APPLICATIONS**

- RF Power Amplifier Control in Base Stations

- Test and Measurement

- Industrial Control

- General Analog Monitoring and Control

# DESCRIPTION

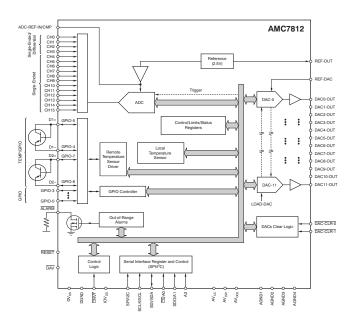

The AMC7812 is a complete analog monitoring and control solution that includes a 16-channel, 12-bit analog-to-digital converter (ADC), twelve 12-bit digital-to-analog converters (DACs), eight GPIOs, and two remote/one local temperature sensor channels.

The AMC7812 has an internal reference of +2.5V that can configure the DAC output voltage to a range of either 0V to +5V or 0V to +12.5V. An external reference can be used as well. Typical power dissipation is 95mW. The AMC7812 is ideal for multichannel applications where board space, size, and low power are critical.

The AMC7812 is available in either a 64-lead QFN or HTQFP-64 PowerPAD<sup>TM</sup> package and is fully specified over the -40°C to +105°C temperature range.

For applications that require a different channel count, additional features, or converter resolutions, Texas Instruments offers a complete family of analog monitor and control (AMC) products. Visit http://www.ti.com/amc for more information.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI, QSPI are trademarks of Motorola, Inc.  $l^2$

I<sup>2</sup>C is a trademark of NXP Semiconductors.

MICROWIRE is a trademark of National Semiconductor. All other trademarks are the property of their respective owners.

## SBAS513C – JANUARY 2011 – REVISED MARCH 2012

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT   | MAXIMUM<br>RELATIVE<br>ACCURACY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>NONLINEARITY<br>(LSB) | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING |  |  |  |

|-----------|------------------------------------------|--------------------------------------------------|------------------|-----------------------|-----------------------------------|--------------------|--|--|--|

| AMC7040   | AMC7812 ±1                               | .1                                               | QFN-64           | RGC                   | -40°C to +105°C                   | AMC7812            |  |  |  |

| AIVIC/812 |                                          | ±1                                               | HTQFP-64         | PAP                   | -40°C to +105°C                   | AMC7812            |  |  |  |

## PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

Over operating free-air temperature range, unless otherwise noted.

|                               |                                             | AMC7812                         | UNIT |

|-------------------------------|---------------------------------------------|---------------------------------|------|

| AV <sub>DD</sub> to GND       |                                             | -0.3 to +6                      | V    |

| DV <sub>DD</sub> to GND       |                                             | -0.3 to +6                      | V    |

| IOV <sub>DD</sub> to GND      |                                             | -0.3 to +6                      | V    |

| AV <sub>CC</sub> to GND       |                                             | -0.3 to +18                     | V    |

| DV <sub>DD</sub> to DGND      |                                             | -0.3 to +6                      | V    |

| Analog input voltage to GND   |                                             | -0.3 to AV <sub>DD</sub> + 0.3  | V    |

| ALARM, GPIO-0, GPIO-1, GP     | PIO-2, GPIO-3, SCLK/SCL, and SDI/SDA to GND | -0.3 to +6                      | V    |

| D1+/GPIO-4, D1-/GPIO-5, D2    | 2+/GPIO-6, D2-/GPIO-7 to GND                | -0.3 to AV <sub>DD</sub> + 0.3  | V    |

| Digital input voltage to DGND |                                             | -0.3 to IOV <sub>DD</sub> + 0.3 | V    |

| SDO and DAV to GND            |                                             | -0.3 to IOV <sub>DD</sub> + 0.3 | V    |

| Operating temperature range   |                                             | -40 to +105                     | °C   |

| Storage temperature range     |                                             | -40 to +150                     | °C   |

| Junction temperature range (  | T <sub>J</sub> max)                         | +150                            | °C   |

| FCD rotings                   | Human body model (HBM)                      | 2.5                             | kV   |

| ESD ratings                   | Charged device model (CDM)                  | 1.0                             | kV   |

(1) Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

## THERMAL INFORMATION

|                               |                                              | AMO       |             |       |

|-------------------------------|----------------------------------------------|-----------|-------------|-------|

| THERMAL METRIC <sup>(1)</sup> |                                              | RGC (QFN) | PAP (HTQFP) | UNITS |

|                               |                                              | 64 PINS   | 64 PINS     |       |

| $\theta_{JA}$                 | Junction-to-ambient thermal resistance       | 24.1      | 33.7        |       |

| θ <sub>JCtop</sub>            | Junction-to-case (top) thermal resistance    | 8.1       | 9.5         |       |

| $\theta_{JB}$                 | Junction-to-board thermal resistance         | 3.2       | 9.0         | °C/W  |

| ΨJT                           | Junction-to-top characterization parameter   | 0.1       | 0.3         | C/W   |

| ΨJB                           | Junction-to-board characterization parameter | 3.3       | 8.9         |       |

| $\theta_{JCbot}$              | Junction-to-case (bottom) thermal resistance | 0.6       | 0.2         |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = DV_{DD} = 4.5$ V to 5.5V,  $AV_{CC} = +15$ V, AGND = DGND = 0V,  $IOV_{DD} = 2.7$ V to 5.5V, internal 2.5V reference, and the DAC output span = 0V to 5V, unless otherwise noted.

|                                             |                              |                                                                                                                                     | AMC7812   |                                                                                                                                                                                                                                                                                                         |                  |

|---------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                                             | PARAMETER                    | TEST CONDITIONS                                                                                                                     | MIN TYP   | MAX                                                                                                                                                                                                                                                                                                     | UNIT             |

| DAC PERFO                                   | DRMANCE                      |                                                                                                                                     |           |                                                                                                                                                                                                                                                                                                         |                  |

| DAC DC AC                                   | CURACY                       |                                                                                                                                     |           |                                                                                                                                                                                                                                                                                                         |                  |

| Resolution                                  |                              |                                                                                                                                     | 12        |                                                                                                                                                                                                                                                                                                         | Bits             |

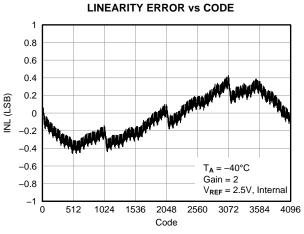

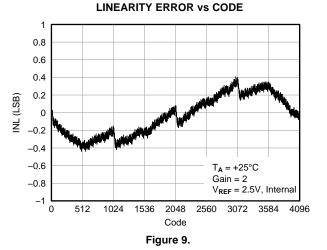

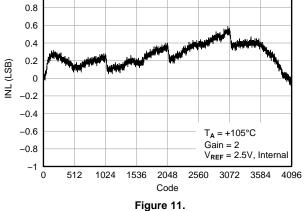

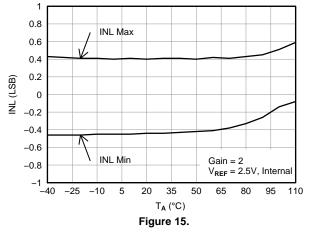

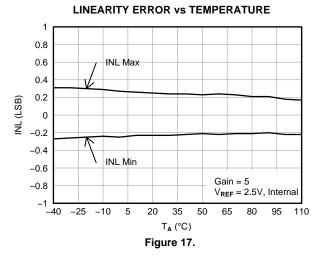

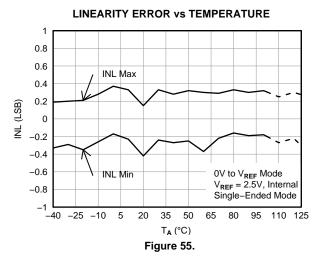

| INL                                         | Relative accuracy            | Measured by line passing through codes 020h and FFFh                                                                                |           | ±1                                                                                                                                                                                                                                                                                                      | LSB              |

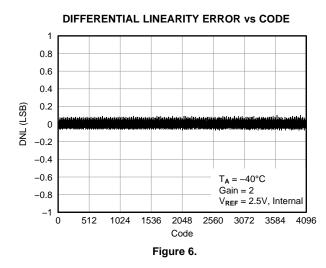

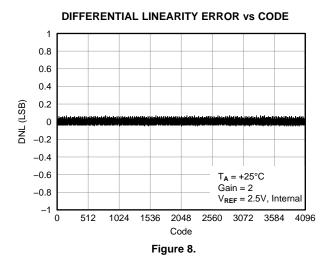

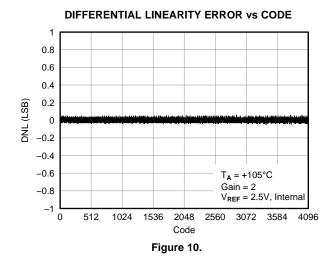

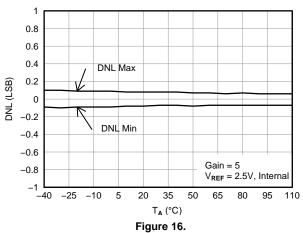

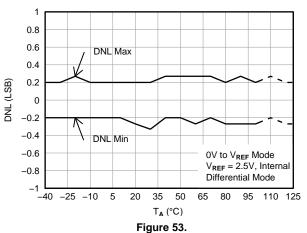

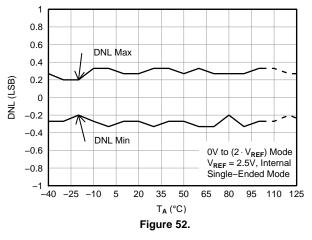

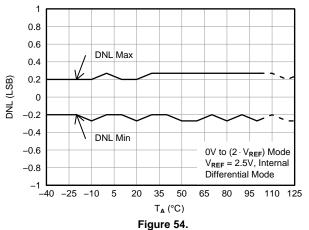

| DNL                                         | Differential nonlinearity    | 12-bit monotonic, Measured by line passing through codes 020h and FFFh                                                              | ±0.3      | ±1                                                                                                                                                                                                                                                                                                      | LSB              |

| TUE                                         | Total unadjusted error       | $T_A = +25^{\circ}C$ , DAC output = 5.0V                                                                                            |           | ±10                                                                                                                                                                                                                                                                                                     | mV               |

| TUE                                         | rotal unadjusted error       | $T_A = +25^{\circ}C$ , DAC output = 12.5V                                                                                           |           | ±30                                                                                                                                                                                                                                                                                                     | mV               |

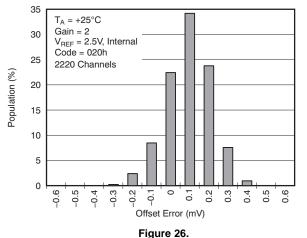

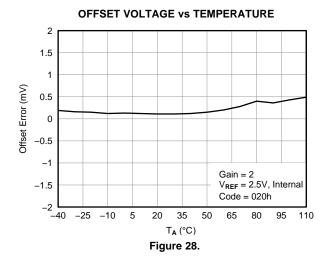

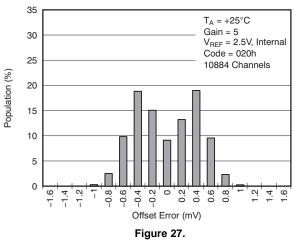

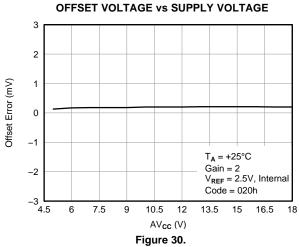

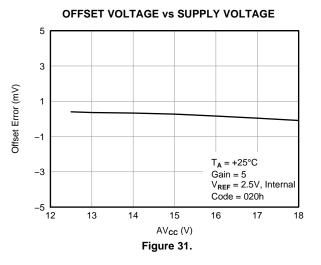

| Offect error                                |                              | $T_A = +25^{\circ}C$ , DAC output = 0V to +5V, code 020h                                                                            |           | ±2                                                                                                                                                                                                                                                                                                      | mV               |

| Offset error                                |                              | $T_A = +25^{\circ}C$ , DAC output = 0V to +12.5V, code 020h                                                                         |           | ±5                                                                                                                                                                                                                                                                                                      | mV               |

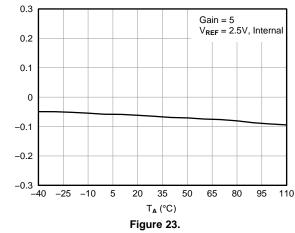

| Offset error                                | temperature coefficient      |                                                                                                                                     | ±1        |                                                                                                                                                                                                                                                                                                         | ppm/°C           |

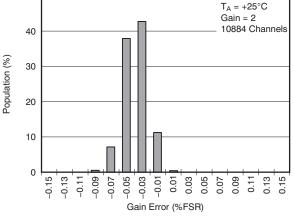

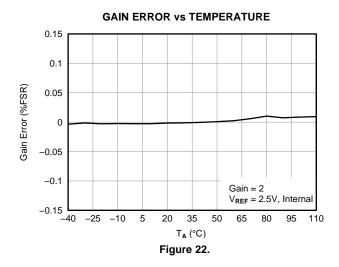

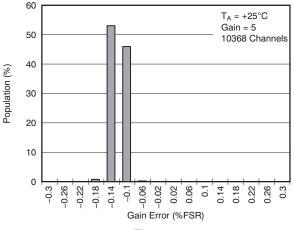

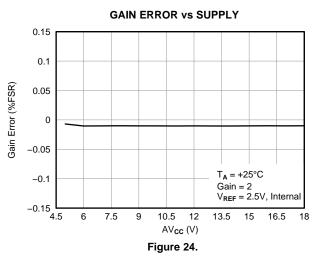

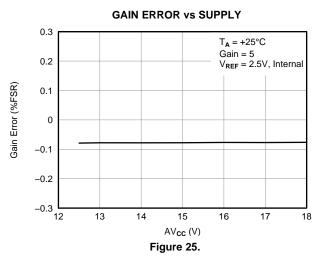

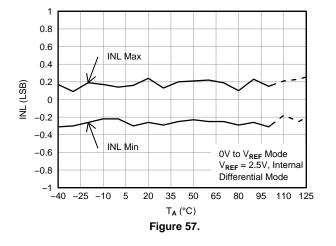

| Coin orres                                  |                              | External reference, output = 0V to +5V                                                                                              | ±0.025    | ±0.15                                                                                                                                                                                                                                                                                                   | %FSR             |

| Gain error                                  |                              | External reference, output = 0V to +12.5V                                                                                           | -0.15     | ±0.3                                                                                                                                                                                                                                                                                                    | %FSR             |

| Gain temper                                 | ature coefficient            |                                                                                                                                     | ±2        |                                                                                                                                                                                                                                                                                                         | ppm/°C           |

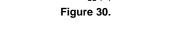

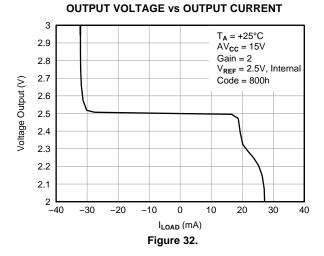

| DAC OUTPU                                   | UT CHARACTERISTICS           |                                                                                                                                     |           |                                                                                                                                                                                                                                                                                                         |                  |

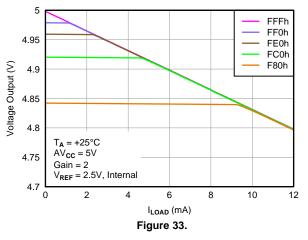

| Output voltage range <sup>(1)</sup>         |                              | $V_{REF} = 2.5V, gain = 2$                                                                                                          | 0         | 5                                                                                                                                                                                                                                                                                                       | V                |

| Output volta                                | ge range (                   | V <sub>REF</sub> = 2.5V, gain = 5                                                                                                   | 0         | 12.5                                                                                                                                                                                                                                                                                                    | V                |

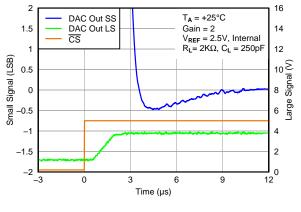

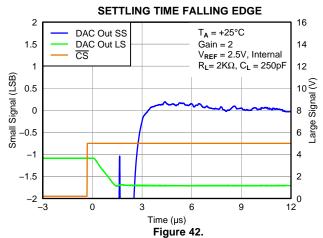

| Output voltage settling time <sup>(2)</sup> |                              | DAC output = 0V to +5V, code 400h to C00h, to $\frac{1}{2}$ LSB, from $\overline{CS}$ rising edge, $R_L = 2k\Omega$ , $C_L = 200pF$ | 3         |                                                                                                                                                                                                                                                                                                         | μs               |

| Slew rate <sup>(2)</sup>                    |                              |                                                                                                                                     | 1.5       |                                                                                                                                                                                                                                                                                                         | V/µs             |

| Short-circuit                               | current <sup>(2)</sup>       | Full-scale current shorted to ground                                                                                                | 30        |                                                                                                                                                                                                                                                                                                         | mA               |

|                                             |                              | Source within 200mV of supply                                                                                                       | +10       |                                                                                                                                                                                                                                                                                                         | mA               |

| Load current                                | t                            | Sink within 300mV of supply                                                                                                         | -10       |                                                                                                                                                                                                                                                                                                         | mA               |

| Capacitive lo                               | bad stability <sup>(2)</sup> | R <sub>L</sub> = ∞                                                                                                                  | 10        |                                                                                                                                                                                                                                                                                                         | nF               |

| DC output in                                | npedance <sup>(2)</sup>      | Code 800h                                                                                                                           | 0.3       |                                                                                                                                                                                                                                                                                                         | Ω                |

| Power-on ov                                 | vershoot                     | AV <sub>CC</sub> 0 to 5V, 2ms ramp                                                                                                  | 5         |                                                                                                                                                                                                                                                                                                         | mV               |

| Digital-to-and                              | alog glitch energy           | Code changes from 7FFh to 800h, 800h to 7FFh                                                                                        | 0.15      |                                                                                                                                                                                                                                                                                                         | nV-s             |

| Digital feedth                              | hrough                       | Device is not accessed                                                                                                              | 0.15      |                                                                                                                                                                                                                                                                                                         | nV-s             |

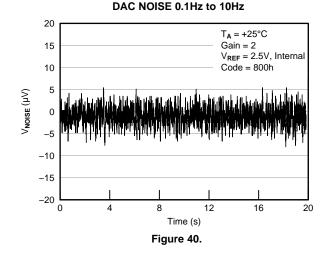

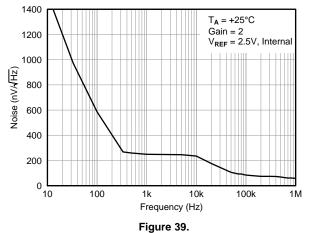

| Output noise                                | )                            | $T_A = +25^{\circ}C$ , at 1kHz, code 800h, gain = 2,<br>excludes reference                                                          | 81        |                                                                                                                                                                                                                                                                                                         | nV/√Hz           |

| ·                                           |                              | f = 0.1Hz to 10Hz, excludes reference                                                                                               | 8         | .3 $\pm 1$ $\pm 10$ $\pm 10$ $\pm 30$ $\pm 2$ $\pm 5$ $\pm 1$ $\pm 5$ $\pm 1$ $25$ $\pm 1$ $25$ $\pm 5$ $\pm 1$ $25$ $\pm 1$ $25$ $\pm 1$ $25$ $\pm 1$ $25$ $\pm 2$ $5$ $3$ $5$ $3$ $5$ $3$ $5$ $3$ $5$ $3$ $5$ $10$ $3$ $5$ $15$ $15$ $26$ $70$ $.5$ $.4$ $10$ $.5$ $.5$ $.5$ $.5$ $.5$ $.5$ $.5$ $.5$ | μV <sub>PP</sub> |

| DAC REFER                                   | RENCE INPUT                  |                                                                                                                                     |           |                                                                                                                                                                                                                                                                                                         |                  |

| Reference v                                 | oltage input range           | REF-DAC pin                                                                                                                         | 1         | 2.6                                                                                                                                                                                                                                                                                                     | V                |

| Input current                               | t <sup>(2)</sup>             | V <sub>REF</sub> = 2.5V                                                                                                             | 170       |                                                                                                                                                                                                                                                                                                         | μA               |

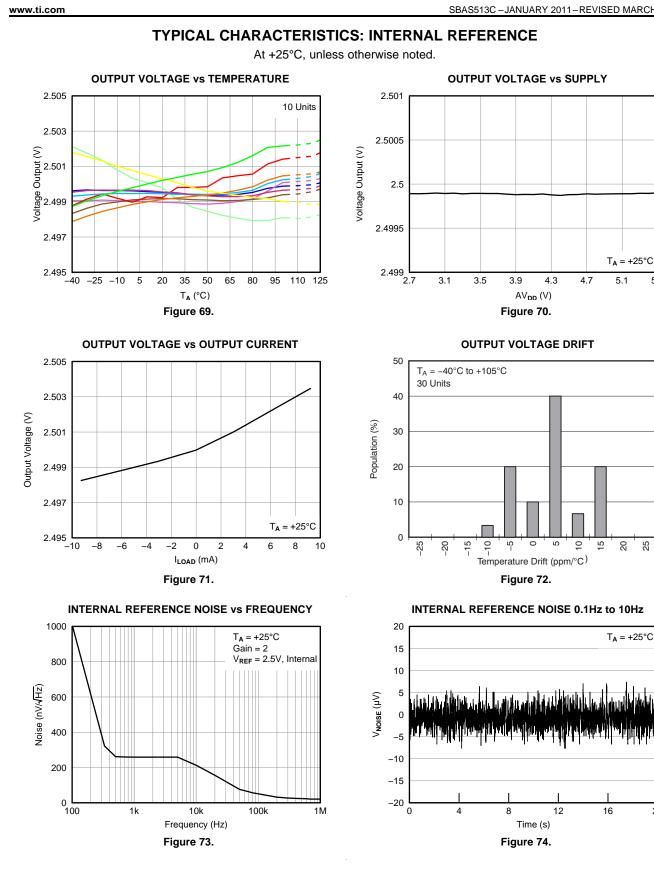

| INTERNAL                                    | REFERENCE                    |                                                                                                                                     |           |                                                                                                                                                                                                                                                                                                         |                  |

| Output volta                                | ge                           | T <sub>A</sub> = +25°C, REF-OUT pin                                                                                                 | 2.495 2.5 | 2.505                                                                                                                                                                                                                                                                                                   | V                |

| Output impe                                 | dance                        |                                                                                                                                     | 0.4       |                                                                                                                                                                                                                                                                                                         | Ω                |

| Reference te                                | emperature coefficient       |                                                                                                                                     | 10        | 25                                                                                                                                                                                                                                                                                                      | ppm/°C           |

| Output curre                                | ent (sourcing/sinking)       |                                                                                                                                     | ±5        |                                                                                                                                                                                                                                                                                                         | mA               |

|                                             |                              | $T_A = +25^{\circ}C$ , f = 1kHz                                                                                                     | 260       |                                                                                                                                                                                                                                                                                                         | nV/√Hz           |

| Output volta                                | ye nuise                     | f = 0.1Hz to 10Hz                                                                                                                   | 13        |                                                                                                                                                                                                                                                                                                         | μV <sub>PP</sub> |

(1) The output voltage must not be greater than AV<sub>CC</sub>. See the *DAC Output* section for more details.

(2) Sampled during initial release to ensure compliance; not subject to production testing.

SBAS513C – JANUARY 2011 – REVISED MARCH 2012

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = DV_{DD} = 4.5$ V to 5.5V,  $AV_{CC} = +15$ V, AGND = DGND = 0V,  $IOV_{DD} = 2.7$ V to 5.5V, internal 2.5V reference, and the DAC output span = 0V to 5V, unless otherwise noted.

|            |                                     |                                                                                      | AMC7812            |      |                   |      |

|------------|-------------------------------------|--------------------------------------------------------------------------------------|--------------------|------|-------------------|------|

|            | PARAMETER                           | TEST CONDITIONS                                                                      | MIN                | TYP  | MAX               | UNIT |

| ADC PEF    | RFORMANCE                           |                                                                                      |                    |      |                   |      |

| ADC DC     | ACCURACY (for AV <sub>DD</sub> = 5) | /)                                                                                   |                    |      |                   |      |

| Resolutio  | n                                   |                                                                                      |                    | 12   |                   | Bits |

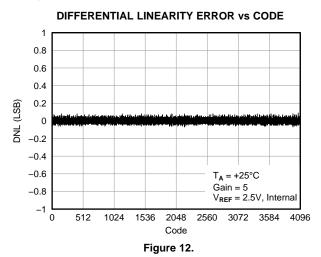

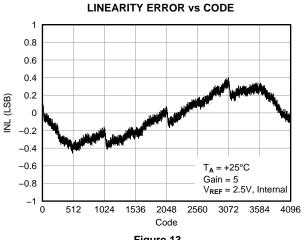

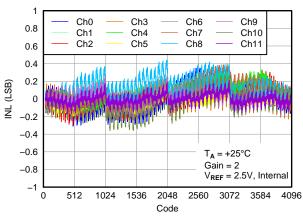

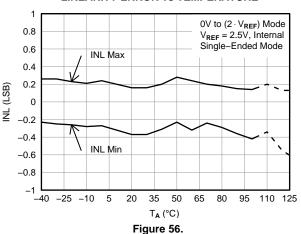

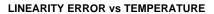

| INL        | Integral nonlinearity               |                                                                                      |                    | ±0.5 | ±1                | LSB  |

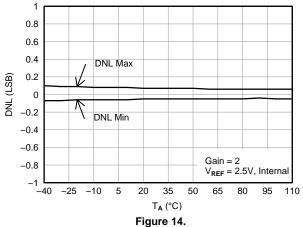

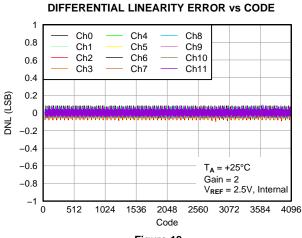

| DNL        | Differential nonlinearity           |                                                                                      |                    | ±0.5 | ±1                | LSB  |

| Single-E   | nded Mode                           |                                                                                      |                    |      |                   |      |

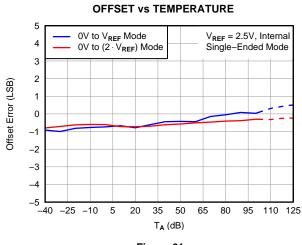

| Offset     | error                               |                                                                                      |                    | ±1   | ±3                | LSB  |

| Offset     | error match                         |                                                                                      |                    | ±0.4 |                   | LSB  |

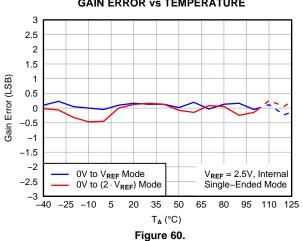

| Gain e     | rror                                | External reference                                                                   |                    | ±1   | ±5                | LSB  |

| Gain e     | rror match                          |                                                                                      |                    | ±0.4 |                   | LSB  |

| Different  | ial Mode                            |                                                                                      |                    |      |                   |      |

| Coin o     |                                     | External reference, 0V to $(2 \cdot V_{REF})$ mode, $V_{CM}$ = 2.5V                  |                    | ±2   | ±5                | LSB  |

| Gain e     | 1101                                | External reference, 0V to V <sub>REF</sub> mode, V <sub>CM</sub> = 1.25V             |                    | ±1   | ±5                | LSB  |

| Gain e     | rror match                          |                                                                                      |                    | ±0.5 |                   | LSB  |

|            |                                     | 0V to $(2 \cdot V_{REF})$ mode, $V_{CM} = 2.5V$                                      |                    | ±1   | ±3                | LSB  |

| Zero c     | ode error                           | External reference, 0V to $V_{REF}$ mode, $V_{CM}$ = 1.25V                           |                    | ±1   | ±3                | LSB  |

| Zero c     | ode error match                     |                                                                                      |                    | ±0.5 |                   | LSB  |

| Comm       | on mode rejection                   | DC, 0V to (2 · V <sub>REF</sub> ) mode                                               |                    | 67   |                   | dB   |

| SAMPLIN    | IG DYNAMICS                         | •                                                                                    |                    |      |                   |      |

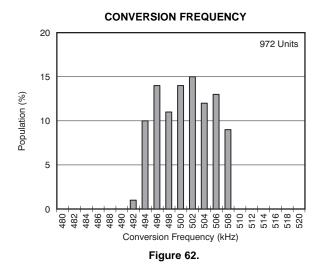

| Comment    |                                     | External single analog channel, auto mode                                            |                    | 500  |                   | kSPS |

| Conversio  | on rate                             | External single analog channel, direct mode                                          |                    | 167  |                   | kSPS |

| Conversio  | on time <sup>(3)</sup>              | External single analog channel                                                       |                    | 2    |                   | μs   |

| Autocycle  | e update rate <sup>(3)</sup>        | All 16 single-ended inputs enabled                                                   |                    | 32   |                   | μs   |

| Throughp   | out rate                            | SPI clock 12MHz or greater, single analog channel                                    |                    |      | 500               | kSPS |

| ANALOG     | input <sup>(4)</sup>                |                                                                                      |                    |      |                   |      |

|            |                                     | Single-ended, 0V to V <sub>REF</sub> mode                                            | 0                  |      | $V_{REF}$         | V    |

|            |                                     | Single-ended, 0V to $(2 \cdot V_{REF})$ mode                                         | 0                  |      | $2 \cdot V_{REF}$ | V    |

| Full-scale | e input voltage                     | $V_{IN+} - V_{IN-}$ , fully-differential, 0V to $V_{REF}$ mode                       | -V <sub>REF</sub>  |      | $+V_{REF}$        | V    |

|            |                                     | $V_{\text{IN+}} - V_{\text{IN-}}$ fully-differential, 0V to (2 $\cdot$ V_{REF}) mode | $-2 \cdot V_{REF}$ |      | $2 \cdot V_{REF}$ | V    |

| Absolute   | input voltage                       |                                                                                      | GND - 0.2          |      | $AV_{DD} + 0.2$   | V    |

| Input cap  | acitance <sup>(3)</sup>             |                                                                                      |                    | 40   |                   | pF   |

| DC input   | leakage current                     | Unselected ADC input                                                                 |                    |      | ±10               | μA   |

| ADC REP    | FERENCE INPUT                       |                                                                                      |                    |      |                   |      |

| Reference  | e input voltage range               |                                                                                      | 1.2                |      | $AV_{DD}$         | V    |

| Input curr | rent                                | V <sub>REF</sub> = 2.5V                                                              |                    | 145  |                   | μA   |

| INTERNA    | AL ADC REFERENCE BUFF               | ER                                                                                   |                    |      |                   |      |

| Offset     |                                     | T <sub>A</sub> = +25°C                                                               |                    |      | ±5                | mV   |

(3)

Sampled during initial release to ensure compliance; not subject to production testing.  $V_{IN+}$  or  $V_{IN-}$  must remain within GND - 0.2V and  $AV_{DD}$  + 0.2V. See *Analog Inputs* section. (4)

# **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = DV_{DD} = 4.5$ V to 5.5V,  $AV_{CC} = +15$ V, AGND = DGND = 0V,  $IOV_{DD} = 2.7$ V to 5.5V, internal 2.5V reference, and the DAC output span = 0V to 5V, unless otherwise noted.

|                            |                                                                                                                             |                                                                                                            | AMC7812 |                                                                                                                                                                                             |                         |      |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|

| PA                         | RAMETER                                                                                                                     | TEST CONDITIONS                                                                                            | MIN     | TYP                                                                                                                                                                                         | MAX                     | UNIT |

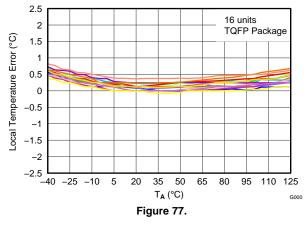

| INTERNAL TE                | MPERATURE SENSO                                                                                                             | R                                                                                                          |         |                                                                                                                                                                                             |                         |      |

| Operating rang             | je                                                                                                                          |                                                                                                            | -40     |                                                                                                                                                                                             | +125                    | °C   |

| A                          |                                                                                                                             | $AV_{DD} = 5V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                               | ±1      |                                                                                                                                                                                             | ±2.5                    | °C   |

| Accuracy                   |                                                                                                                             | $AV_{DD} = 5V$ , $T_A = 0^{\circ}C$ to $+100^{\circ}C$                                                     |         | ±1.5<br>0.125<br>15<br>40 +150<br>±1.5<br>±2<br>0.125                                                                                                                                       |                         | °C   |

| Resolution                 |                                                                                                                             | Per LSB                                                                                                    |         | 0.125                                                                                                                                                                                       |                         | °C   |

| Conversion rat             | on rate     External temperature sensors are disabled     15       AL TEMPERATURE SENSOR (Using 2N3906 external transistor) |                                                                                                            | ms      |                                                                                                                                                                                             |                         |      |

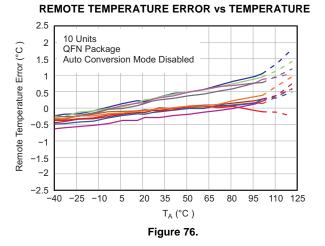

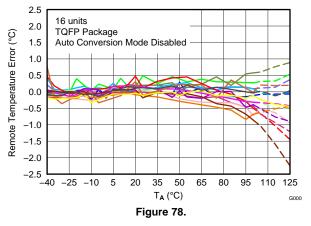

| EXTERNAL T                 | EMPERATURE SENSO                                                                                                            | DR (Using 2N3906 external transistor)                                                                      |         |                                                                                                                                                                                             |                         |      |

| Operating rang             | je                                                                                                                          | Limited by external diode                                                                                  | -40     |                                                                                                                                                                                             | +150                    | °C   |

| Accuracy <sup>(5)(6)</sup> |                                                                                                                             | $AV_{DD} = 5V, T_A = 0^{\circ}C \text{ to } +100^{\circ}C, T_D = -40^{\circ}C \text{ to } +150^{\circ}C$   |         |                                                                                                                                                                                             | ±1.5                    | °C   |

| Accuracy                   |                                                                                                                             | $AV_{DD} = 5V, T_A = -40^{\circ}C \text{ to } +100^{\circ}C, T_D = -40^{\circ}C \text{ to } +150^{\circ}C$ |         |                                                                                                                                                                                             | ±2                      | °C   |

| Resolution                 |                                                                                                                             | Per LSB                                                                                                    |         | 0.125                                                                                                                                                                                       |                         | °C   |

| Comunication and           |                                                                                                                             | With resistance cancellation<br>(RC bit = '1')                                                             | 72      | 93                                                                                                                                                                                          | 100                     | ms   |

| Conversion rat             | te per sensor                                                                                                               | Without resistance cancellation<br>(RC bit = '0')                                                          | 33      | 44                                                                                                                                                                                          | 47                      | ms   |

| DIGITAL LOG                | IC: GPIO <sup>(7)(8)</sup> and ALA                                                                                          | ARM                                                                                                        |         |                                                                                                                                                                                             |                         |      |

|                            |                                                                                                                             | $IOV_{DD} = +5V$                                                                                           | 2.1     |                                                                                                                                                                                             | 0.3 + IOV <sub>DD</sub> | V    |

| V <sub>IH</sub> In         | put high voltage                                                                                                            | $IOV_{DD} = +3.3V$                                                                                         | 2.1     | .1 0.3 + IOV <sub>DD</sub>                                                                                                                                                                  | 0.3 + IOV <sub>DD</sub> | V    |

|                            |                                                                                                                             | IOV <sub>DD</sub> = +5V                                                                                    | -0.3    | 0.3 + IOV <sub>DD</sub><br>0.3 + IOV <sub>DD</sub><br>3 0.8<br>3 0.8<br>0.8<br>0.4                                                                                                          | V                       |      |

| V <sub>IL</sub> In         | put low voltage                                                                                                             | IOV <sub>DD</sub> = +3.3V                                                                                  | -0.3    |                                                                                                                                                                                             | 0.8                     | V    |

|                            |                                                                                                                             | $IOV_{DD} = +5V$ , sinking 5mA                                                                             |         | 2 93 100<br>3 44 47<br>1 0.3 + IOV <sub>DD</sub><br>1 0.3 + IOV <sub>DD</sub><br>3 0.8<br>3 0.8<br>3 0.8<br>0.4<br>0.4<br>5<br>10<br>1 0.3 + IOV <sub>DD</sub><br>1 0.3 + IOV <sub>DD</sub> | V                       |      |

| V <sub>OL</sub> O          | utput low voltage                                                                                                           | $IOV_{DD} = +3.3V$ , sinking 2mA                                                                           |         |                                                                                                                                                                                             | V                       |      |

| High-impedanc              | ce leakage                                                                                                                  |                                                                                                            |         |                                                                                                                                                                                             | 5                       | μA   |

| High-impedanc              | ce output capacitance                                                                                                       |                                                                                                            |         |                                                                                                                                                                                             | 10                      | pF   |

| DIGITAL LOG                | IC: All Except SCL, SI                                                                                                      | DA, ALARM, and GPIO                                                                                        |         |                                                                                                                                                                                             | 1                       |      |

|                            |                                                                                                                             | $IOV_{DD} = +5V$                                                                                           | 2.1     |                                                                                                                                                                                             | 0.3 + IOV <sub>DD</sub> | V    |

| V <sub>IH</sub> In         | put high voltage                                                                                                            | $IOV_{DD} = +3.3V$                                                                                         | 2.1     |                                                                                                                                                                                             |                         | V    |

|                            |                                                                                                                             | $IOV_{DD} = +5V$                                                                                           | -0.3    |                                                                                                                                                                                             |                         | V    |

| V <sub>IL</sub> In         | put low voltage                                                                                                             | $IOV_{DD} = +3.3V$                                                                                         | -0.3    |                                                                                                                                                                                             | 0.8                     | V    |

| Input current              |                                                                                                                             |                                                                                                            |         |                                                                                                                                                                                             | ±1                      | μA   |

| Input capacitar            | nce                                                                                                                         |                                                                                                            |         |                                                                                                                                                                                             | 5                       | pF   |

|                            |                                                                                                                             | $IOV_{DD} = +5V$ , sourcing 3mA                                                                            | 4.8     |                                                                                                                                                                                             |                         | V    |

| V <sub>OH</sub> O          | utput high voltage                                                                                                          | $IOV_{DD} = +3.3V$ , sourcing 3mA                                                                          | 2.9     |                                                                                                                                                                                             |                         | V    |

|                            |                                                                                                                             | $IOV_{DD} = +5V$ , sinking 3mA                                                                             |         |                                                                                                                                                                                             | 0.4                     | V    |

| V <sub>OL</sub> O          | utput low voltage                                                                                                           | $IOV_{DD} = +3.3V$ , sinking 3mA                                                                           |         |                                                                                                                                                                                             | 0.4                     | V    |

| High-impedanc              | ce leakage                                                                                                                  |                                                                                                            |         |                                                                                                                                                                                             | ±5                      | μA   |

| <b>°</b> ,                 | ce output capacitance                                                                                                       |                                                                                                            |         |                                                                                                                                                                                             | 10                      | pF   |

(5)  $T_D$  is the external diode temperature.

(6) Auto conversion mode disabled

(7) For pins GPIO0-3, the external pull up resistor must be connected to a voltage less than or equal to 5.5V.

(8) For pins GPIO4-7, the external pull up resistor must be connected to a voltage less than or equal to AV<sub>DD</sub>.

SBAS513C – JANUARY 2011 – REVISED MARCH 2012

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = DV_{DD} = 4.5$ V to 5.5V,  $AV_{CC} = +15$ V, AGND = DGND = 0V,  $IOV_{DD} = 2.7$ V to 5.5V, internal 2.5V reference, and the DAC output span = 0V to 5V, unless otherwise noted.

|                   |                                     |                                                                                | AMC7812                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |      |

|-------------------|-------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|

|                   | PARAMETER                           | TEST CONDITIONS                                                                | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MAX                     | UNIT |

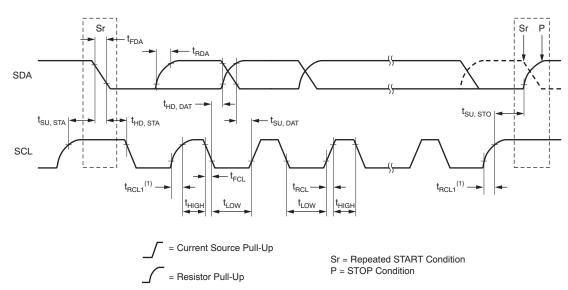

| DIGITAL           | LOGIC: SDA, SCL (I <sup>2</sup> C-C | compatible Interface)                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |      |

| \ <i>\</i>        |                                     | $IOV_{DD} = +5V$                                                               | 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $0.3 + IOV_{DD}$        | V    |

| V <sub>IH</sub>   | Input high voltage                  | $IOV_{DD} = +3.3V$                                                             | 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.3 + IOV <sub>DD</sub> | V    |

| V                 | Input low voltogo                   | $IOV_{DD} = +5V$                                                               | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TYP         MAX           2.1 $0.3 + IOV_{DD}$ 2.1 $0.3 + IOV_{DD}$ 2.1 $0.3 + IOV_{DD}$ 2.1 $0.3 + IOV_{DD}$ 0.3 $0.8$ $\pm 5$ $5$ 0 $0.4$ 0 $0.4$ 0 $0.4$ 0 $0.4$ 100 $250$ 100 $250$ 20 $70$ 20 $70$ 1.00 $250$ 2.7 $+5.5$ 7.9 $12.5$ 1.6 $4.5$ $4.5$ $+18$ $6.5$ $95$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V                       |      |

| V <sub>IL</sub>   | Input low voltage                   | $IOV_{DD} = +3.3V$                                                             | MIN         TYP         MAX           2.1 $0.3 + IOV_{DI}$ 2.1 $0.3 + IOV_{DI}$ -0.3 $0.6$ -0.3 $0.6$ -0.3 $0.6$ -0.6         0.6           0 $0.6$ -0.6         0.6           0 $0.6$ -0.6         0.6           0 $0.6$ -0.6         0.6           0 $0.6$ -0.6         -0.6           0 $0.6$ -0.6         -0.6           0 $0.6$ -0.6         -0.6           0         0.6         -0.6         -0.6           5V to         100         250         -0.6           5V to         100         250         -0.6           20         -0.6         -0.6         -0.6           20         -0.6         -0.6         -0.6           +2.7         +5.5         -1.6         -0.6           +2.7         +5.5         -0.6         -0.6           +2.7         +5.5         -0.5         -0.5           +2.7         +5.5         -0.5         -0.5           +2.7 | 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V                       |      |

| Input curr        | rent                                |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ±5                      | μA   |

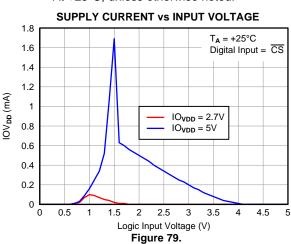

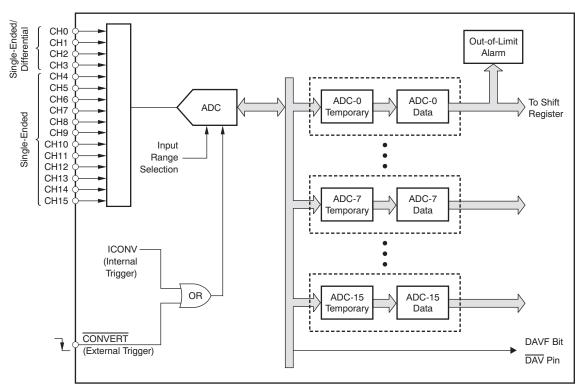

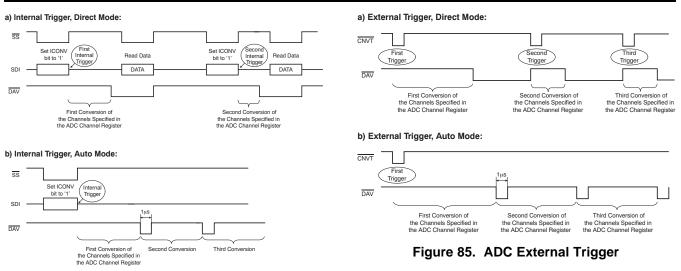

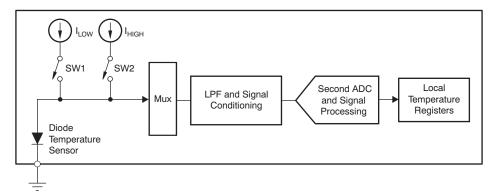

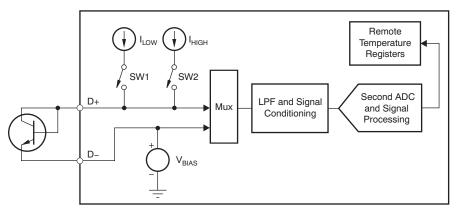

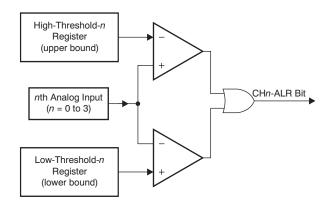

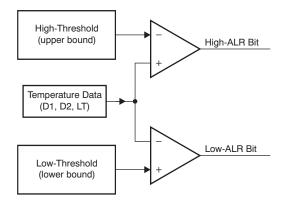

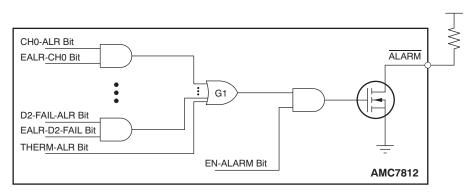

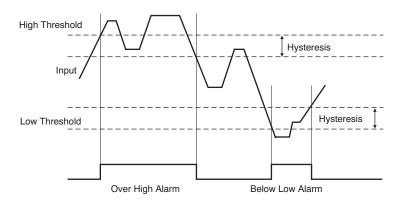

| Input cap         | acitance                            |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                       | pF   |