Large Current External FET Controller Type Switching Regulator

# Dual-output, high voltage, high-efficiency step-down **Switching Regulator** (Controller type) **BD9011EKN, BD9011KV, BD9775FV**

#### Overview

The BD9011EKN/KV is a 2-ch synchronous controller with rectification switching for enhanced power management efficiency. It supports a wide input range, enabling low power consumption ecodesign for an array of electronics.

#### Features

- 1) Wide input voltage range: 3.9V to 30V

- 2) Precision voltage references: 0.8V±1%

- 3) FET direct drive

- 4) Rectification switching for increased efficiency

- 5) Variable frequency: 250k to 550kHz (external synchronization to 550kHz)

- 6) Built-in selected OFF latch and auto remove over current protection

- 7) Built-in independent power up/power down sequencing control

- 8) Make various application, step-down, step-up and step-up-down

- 9) Small footprint packages: HQFN36V, VQFP48C

## Applications

Car audio and navigation systems, CRTTV, LCDTV, PDPTV, STB, DVD, and PC systems, portable CD and DVD players,

## ● Absolute Maximum Ratings (Ta=25°C)

| Parameter                | Symbol        | Rating | Unit | Parameter             | Symbol    | Rating      | Unit |

|--------------------------|---------------|--------|------|-----------------------|-----------|-------------|------|

| EXTVCC Voltage           | EXTVCC        | 34 *1  | ٧    | COMP1,2 Voltage       | COMP1,2   |             |      |

| VCCCL1,2 Voltage         | VCCCL1,2      | 34 *1  | ٧    | DET1,2 Voltage        | DET1,2    | VREG5       | V    |

| CL1,2 Voltage            | CL1,2         | 34     | V    | RT, SYNC Voltage      | RT, SYNC  |             |      |

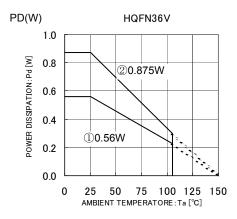

| SW1,2 Voltage            | SW1,2         | 34 *1  | ٧    |                       |           | 0.875*2     | W    |

| BOOT1,2 Voltage          | BOOT1,2       | 40 *1  | V    |                       |           | (HQFN36V)   | VV   |

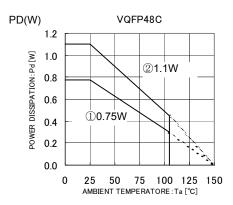

| BOOT1,2-SW1,2<br>Voltage | BOOT1,2-SW1,2 | 7 *1   | V    | Power Dissipation     | Pd 1.1 *2 |             | W    |

| STB, EN1,2 Voltage       | STB, EN1,2    | VCC    | V    |                       |           | (VQFP48C)   |      |

| VREG5,5A                 | VREG5,5A      | 7      | V    | Operating temperature | Topr      | -40 to +105 | Ωຶ   |

| VREG33                   | VREG33        | VREG5  | V    | Storage temperature   | Tstg      | -55 to +150 | °C   |

| SS1,2, FB1,2             | SS1,2,FB1,2   | VREG5  | ٧    | Junction temperature  | Tj        | +150        | °C   |

<sup>\*1</sup> Regardless of the listed rating, do not exceed Pd in any circumstances.

<sup>\*2</sup> Mounted on a 70mm x 70mm x 0.8mm glass-epoxy board. De-rated at 7.44mW/°C (HQFN36V) or 8.8mW/°C (VQFP48C) above 25°C.

# ●Operating conditions (Ta=25°C)

| Parameter              | Symbol  | Min.      | Тур. | Max.  | Unit     |

|------------------------|---------|-----------|------|-------|----------|

| Input voltage 1        | EXTVCC  | 3.9 *1 *2 | 12   | 30    | <b>V</b> |

| Input voltage 2        | VCC     | 3.9 *1 *2 | 12   | 30    | V        |

| BOOT-SW voltage        | BOOT-SW | 4.5       | 5    | VREG5 | V        |

| Carrier frequency      | OSC     | 250       | 300  | 550   | kHz      |

| Synchronous frequency  | SYNC    | OSC       | -    | 550   | kHz      |

| Synchronous pulse duty | Duty    | 40        | 50   | 60    | %        |

| Min OFF pulse          | TMIN    | -         | 100  | -     | nsec     |

<sup>★</sup>This product is not designed to provide resistance against radiation.

# ● Electrical characteristics (Unless otherwise specified, Ta=25°C VCC=12V STB=5V EN1,2=5V)

| Demonstra                                       | Limit      |       |       | 1.1:4 | Conditions |                          |

|-------------------------------------------------|------------|-------|-------|-------|------------|--------------------------|

| Parameter                                       | Symbol     | Min.  | Тур.  | Max.  | Unit       | Conditions               |

| VIN bias current                                | IIN        | -     | 5     | 10    | mA         |                          |

| Shutdown mode current                           | IST        | -     | 0     | 10    | μΑ         | VSTB=0V                  |

| [Error Amp Block]                               |            |       |       | 1     |            |                          |

| Feedback reference voltage                      | VOB        | 0.792 | 0.800 | 0.808 | V          |                          |

| Feedback reference voltage<br>(Ta=-40 to 105°C) | VOB+       | 0.784 | 0.800 | 0.816 | ٧          | Ta=-40 to 105°C ※        |

| Open circuit voltage gain                       | Averr      | -     | 46    | -     | dB         |                          |

| VO input bias current                           | IVo+       | -     | -     | 1     | μΑ         |                          |

| [FET Driver Block]                              |            |       |       |       |            |                          |

| HG high side ON resistance                      | HGhon      | -     | 1.5   | -     | Ω          |                          |

| HG low side ON resistance                       | HGlon      | -     | 1.0   | -     | Ω          |                          |

| LG high side ON resistance                      | LGhon      | -     | 1.5   | -     | Ω          |                          |

| LG low side ON resistance                       | LGlon      | -     | 0.5   | -     | Ω          |                          |

| [Oscillator]                                    |            |       |       |       |            |                          |

| Carrier frequency                               | FOSC       | 270   | 300   | 330   | kHz        | RT=100 kΩ                |

| Synchronous frequency                           | Fsync      | -     | 500   | -     | kHz        | RT=100 kΩ,SYNC=500kHz    |

| [Over Current Protection Block]                 |            |       |       |       |            |                          |

| CL threshold voltage                            | Vswth      | 70    | 90    | 110   | mV         |                          |

| CL threshold voltage<br>(Ta=-40 to 105°C)       | Vswth+     | 67    | 90    | 113   | mV         | Ta=-40 to 105°C ※        |

| [VREG Block]                                    |            |       |       |       |            |                          |

| VREG5 output voltage                            | VREG5      | 4.8   | 5     | 5.2   | V          | IREF=6mA                 |

| VREG33 reference voltage                        | VREG33     | 3.0   | 3.3   | 3.6   | V          | IREG=6mA                 |

| VREG5 threshold voltage                         | VREG_UVLO  | 2.6   | 2.8   | 3.0   | V          | VREG:Sweep down          |

| VREG5 hysteresis voltage                        | DVREG_UVLO | 50    | 100   | 200   | mV         | VREG:Sweep up            |

| [Soft start block]                              |            |       | 1     | I     | 1          | 1                        |

| Charge current                                  | ISS        | 6.5   | 10    | 13.5  | μΑ         | VSS=1V                   |

| Charge current<br>(Ta=-40 to 105°C)             | ISS+       | 6     | 10    | 14    | μΑ         | VSS=1V,Ta=-40 to 105°C % |

Note: Not all shipped products are subject to outgoing inspection.

<sup>\*1</sup> After more than 4.5V, voltage range.

<sup>\*2</sup> In case of using less than 6V, Short to VCC, EXTVCC and VREG5.

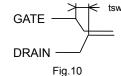

Fig.10 EN threshold voltage

Fig.11 Load transient response 1

**11** 50.20 %

Fig.12 Load transient response 2

**ij**50.20 %

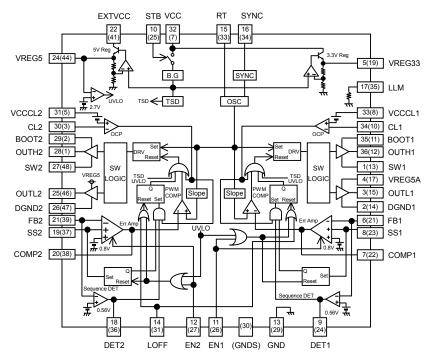

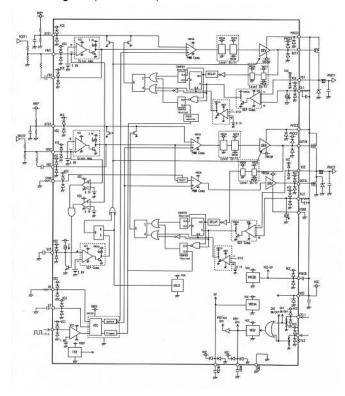

## ●Block diagram (Parentheses indicate VQFP48C pin numbers)

Fig-13

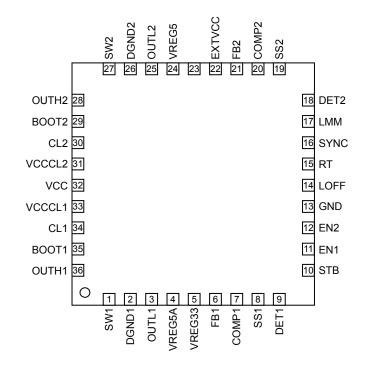

## ●Pin configuration

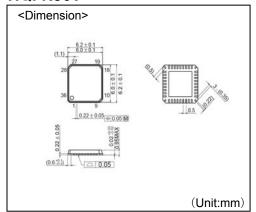

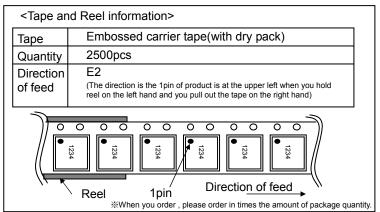

## BD9011EKN (HQFN36V)

Fig-14

## ●PIN function table

| Pin<br>No. | Pin name | Function                                              |  |

|------------|----------|-------------------------------------------------------|--|

| 1          | SW1      | High side FET source pin 1                            |  |

| 2          | DGND1    | Low side FET source pin 1                             |  |

| 3          | OUTL1    | Low side FET gate drive pin 1                         |  |

| 4          | VREG5A   | FET drive REG input                                   |  |

| 5          | VREG33   | Reference input REG output                            |  |

| 6          | FB1      | Error amp input 1                                     |  |

| 7          | COMP1    | Error amp output 1                                    |  |

| 8          | SS1      | Soft start setting pin 1                              |  |

| 9          | DET1     | FB detector output 1                                  |  |

| 10         | STB      | Standby ON/OFF pin                                    |  |

| 11         | EN1      | Output 1ON/OFF pin                                    |  |

| 12         | EN2      | Output 2ON/OFFpin                                     |  |

| 13         | GND      | Ground                                                |  |

| 14         | LOFF     | Over current protection OFF latch function ON/OFF pin |  |

| 15         | RT       | Switching frequency setting pin                       |  |

| 16         | SYNC     | External synchronous pulse input pin                  |  |

| 17         | LLM      | Built-in pull-down resistor pin                       |  |

| 18         | DET2     | FB detector output 2                                  |  |

| 19         | SS2      | Soft start setting pin 2                              |  |

| 20         | COMP2    | Error amp output 2                                    |  |

| 21         | FB2      | Error amp input 2                                     |  |

| 22         | EXTVCC   | External power input pin                              |  |

| 23         | _        | N.C.                                                  |  |

| 24         | VREG5    | FET drive REG output                                  |  |

| 25         | OUTL2    | Low side FET gate drive pin 2                         |  |

| 26         | DGND2    | Low side FET source pin 2                             |  |

| 27         | SW2      | High side FET source pin 2                            |  |

| 28         | OUTH2    | Hi side FET gate drive pin 2                          |  |

| 29         | BOOT2    | OUTH2 driver power pin                                |  |

| 30         | CL2      | Over current detector setting pin 2                   |  |

| 31         | VCCCL2   | Over current detection VCC2                           |  |

| 32         | VCC      | Input power pin                                       |  |

| 33         | VCCCL1   | Over current detection VCC1                           |  |

| 34         | CL1      | Over current detector setting pin 1                   |  |

| 35         | BOOT1    | OUTH1 driver power pin                                |  |

| 36         | OUTH1    | High side FET gate drive pin 1                        |  |

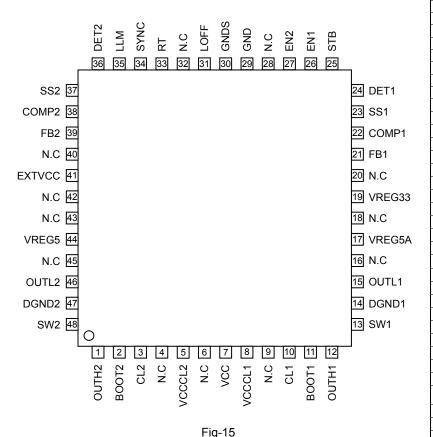

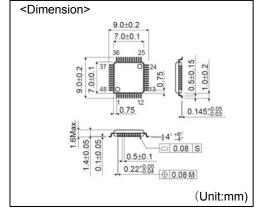

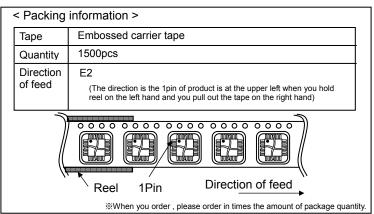

#### Pin configuration

BD9011KV (VQFP48C)

■Pin function table

| ●Pin f     | unction table |                                                |

|------------|---------------|------------------------------------------------|

| Pin<br>No. | Pin name      | Function                                       |

| 1          | OUTH2         | High side FET gate drive pin 2                 |

| 2          | BOOT2         | OUTH2 driver power pin                         |

| 3          | CL2           | Over current detection pin 2                   |

| 4          | N.C           | Non-connect (unused) pin                       |

| 5          | VCCCL2        | Over current detection VCC2                    |

| 6          | N.C           | Non-connect (unused) pin                       |

| 7          | VCC           | Input power pin                                |

| 8          | VCCCL1        | Over current detection CC1                     |

| 9          | N.C           | Non-connect (unused) pin                       |

| 10         | CL1           | Over current detection setting pin 1           |

| 11         | BOOT1         | OUTH1 driver power pin                         |

| 12         | OUTH1         | High side FET gate drive pin 1                 |

| 13         | SW1           | High side FET source pin 1                     |

| 14         | DGND1         | Low side FET source pin 1                      |

| 15         | OUTL1         | Low side FET gate drive pin 1                  |

| 16         | N.C           | Non-connect (unused) pin                       |

| 17         | VREG5A        | FET drive REG input                            |

| 18         | N.C           | Non-connect (unused) pin                       |

| 19         | VREG33        | Reference input REG output                     |

| 20         | N.C           | Non-connect (unused) pin                       |

| 21         | FB1           | Error amp input 1                              |

| 22         | COMP1         | Error amp output 1                             |

| 23         | SS1           | Soft start setting pin 1                       |

| 24         | DET1          | FB detector output 1                           |

| 25         | STB           | Standby ON/OFF pin                             |

| 26         | EN1           | Output 1 ON/OFF pin                            |

| 27         | EN2           | Output 2 ON/OFF pin                            |

| 28         | N.C           | Non-connect (unused) pin                       |

| 29         | GND           | Ground                                         |

| 30         | GNDS          |                                                |

|            |               | Sense ground Over current protection OFF latch |

| 31         | LOFF          | function ON/OFF pin                            |

| 32         | N.C           | Non-connect (unused) pin                       |

| 33         | RT            | Switching frequency setting pin                |

| 34         | SYNC          | External synchronous pulse input pin           |

| 35         | LLM           | Built-in pull-down resistor pin                |

| 36         | DET2          | FB detector output 2                           |

| 37         | SS2           | Soft start setting pin 2                       |

| 38         | COMP2         | Error amp output 2                             |

| 39         | FB2           | Error amp input 2                              |

| 40         | N.C           | Non-connect (unused) pin                       |

| 41         | EXTVCC        | External power input pin                       |

| 42         | N.C           | Non-connect (unused) pin                       |

| 43         | N.C           | Non-connect (unused) pin                       |

| 44         | VREG5         | FET drive REG output                           |

| 45         | N.C           | Non-connect (unused) pin                       |

| 46         | OUTL2         | Low side FET gate drive pin 2                  |

| 47         | DGND2         | Low side FET source pin 2                      |

| 48         | SW2           | High side FET source pin 2                     |

|            | 02            | g.r oldo i E i oodioo piii 2                   |

## Block functional descriptions

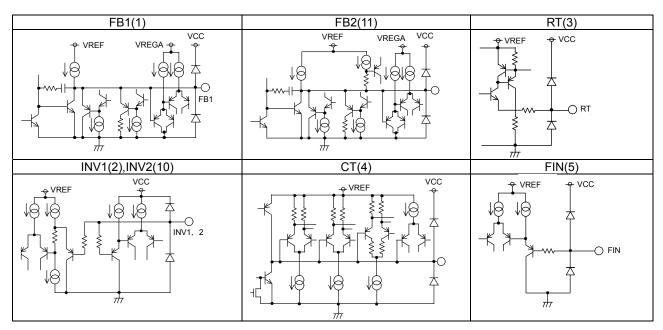

· Error amp

The error amp compares output feedback voltage to the 0.8V reference voltage and provides the comparison result as COMP voltage, which is used to determine the switching Duty. COMP voltage is limited to the SS voltage, since soft start at power up is based on SS pin voltage.

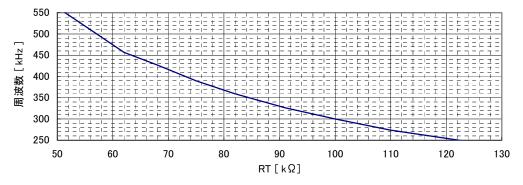

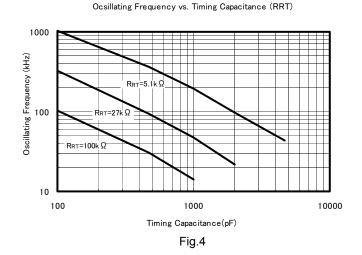

Oscillator (OSC)

Oscillation frequency is determined by the switching frequency pin (RT) in this block. The frequency can be set between 250kHz and 550kHz.

SLOPE

The SLOPE block uses the clock produced by the oscillator to generate a triangular wave, and sends the wave to the PWM comparator.

• PWM COMP

The PWM comparator determines switching Duty by comparing the COMP voltage, output from the error amp, with the triangular wave from the SLOPE block. Switching duty is limited to a percentage of the internal maximum duty, and thus cannot be 100% of the maximum.

Reference voltage (5Vreg, 33Vreg)

This block generates the internal reference voltages: 5V and 3.3V.

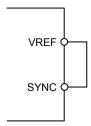

External synchronization (SYNC)

Determines the switching frequency, based on the external pulse applied.

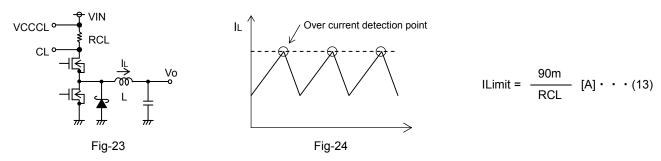

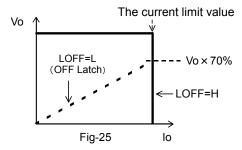

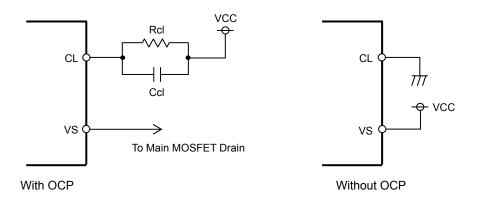

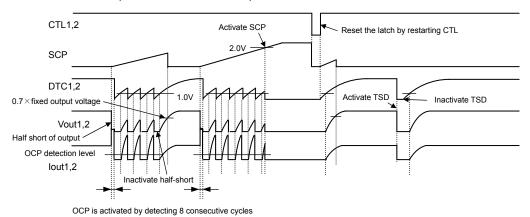

Over current protection (OCP)

Over current protection is activated when the VCCCL-CL voltage reaches or exceeds 90mV. When over current protection is active, Duty is low, and output voltage also decreases. When LOFF=L, the output voltage has fallen to 70% or below and output is latched OFF. The OFF latch mode ends when the latch is set to STB, EN.

Sequence control (Sequence DET)

Compares FB voltage with reference voltage (0.56V) and outputs the result as DET.

Protection circuits (UVLO/TSD)

The UVLO lock out function is activated when VREG falls to about 2.8V, while TSD turns outputs OFF when the chip temperature reaches or exceeds 150°C. Output is restored when temperature falls back below the threshold value.

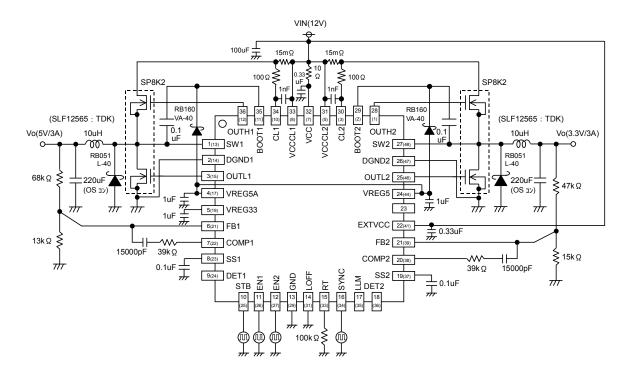

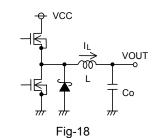

●Application circuit example (Parentheses indicate VQFP48C pin numbers)

Fig-16A (Step-Down : Cout=OS Capacitor)

There are many factors(The PCB board layout, Output Current, etc.)that can affect the DCDC characteristics. Please verify and confirm using practical applications.

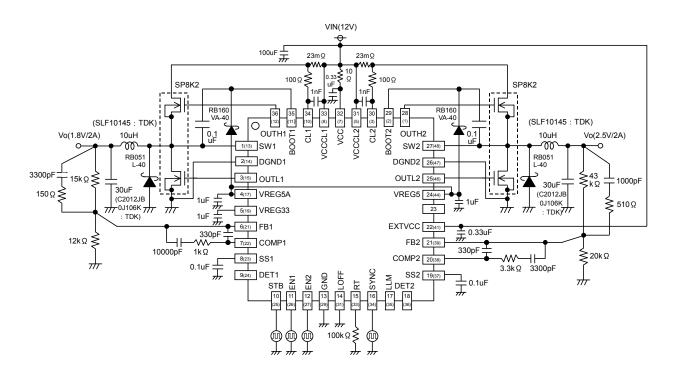

Fig-16B (Step-Down : Cout=Ceramic Capacitor)

There are many factors(The PCB board layout, Output Current, etc.)that can affect the DCDC characteristics. Please verify and confirm using practical applications.

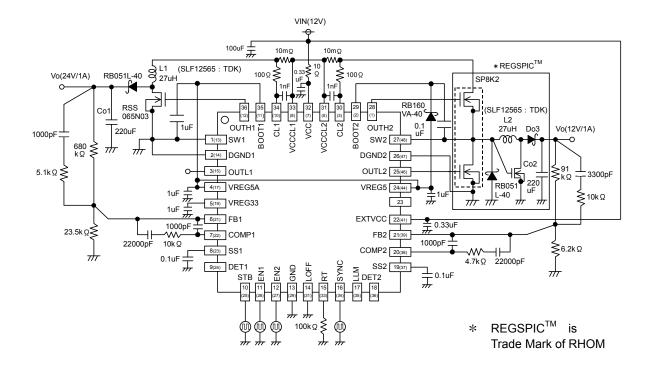

Fig-16C (Step-Down: Low Input Voltage)

There are many factors(The PCB board layout, Output Current, etc.)that can affect the DCDC characteristics. Please verify and confirm using practical applications.

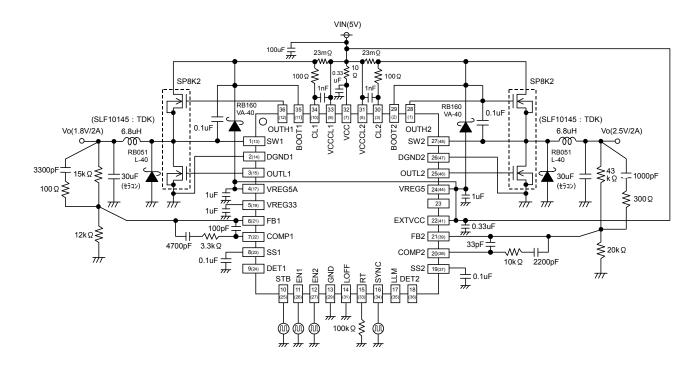

Fig-16D (Step-Up : and Step-Up-Down)

There are many factors(The PCB board layout, Output Current, etc.)that can affect the DCDC characteristics. Please verify and confirm using practical applications.

## Application component selection

## (1) Setting the output L value

Fig-17

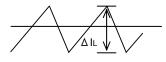

Output ripple current

The coil value significantly influences the output ripple current. Thus, as seen in equation (5), the larger the coil, and the higher the switching frequency, the lower the drop in ripple current.

$$\Delta IL = \frac{(VCC-VOUT) \times VOUT}{L \times VCC \times f} \quad [A] \cdot \cdot \cdot (5)$$

The optimal output ripple current setting is 30% of maximum current.  $\Delta$  IL = 0.3 × IOUTmax.[A] · · · (6)

$$L = \frac{(VCC-VOUT) \times VOUT}{\Delta IL \times VCC \times f} [H] \cdot \cdot \cdot (7)$$

$(\Delta IL : output ripple current f : switching frequency)$

\*\*Outputting a current in excess of the coil current rating will cause magnetic saturation of the coil and decrease efficiency.

Please establish sufficient margin to ensure that peak current does not exceed the coil current rating. \*\*Use low resistance (DCR, ACR) coils to minimize coil loss and increase efficiency.

## (2) Setting the output capacitor Co value

Select the output capacitor with the highest value for ripple voltage (VPP) tolerance and maximum drop voltage (at rapid load change). The following equation is used to determine the output ripple voltage.

Step down

$$\Delta V_{PP} = \Delta I_L \times R_{ESR} + \frac{\Delta I_L}{Co} \times \frac{Vo}{Vcc} \times \frac{1}{f}$$

[V] Note: f : switching frequency

Be sure to keep the output Co setting within the allowable ripple voltage range.

\*\*Please allow sufficient output voltage margin in establishing the capacitor rating. Note that low-ESR capacitors enable lower output ripple voltage.

Also, to meet the requirement for setting the output startup time parameter within the soft start time range, please factor in the conditions described in the capacitance equation (9) for output capacitors, below.

$$\text{Co} \leq \frac{\text{TSS} \times (\text{Limit} - \text{IOUT})}{\text{VOUT}} \qquad \qquad \text{Tss} : \text{ soft start time}$$

$$\text{ILimit} : \text{over current detection value (2/16) reference}$$

Note: less than optimal capacitance values may cause problems at startup.

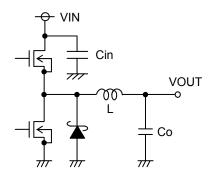

#### (3) Input capacitor selection

Fig-19

Input capacitor

The input capacitor serves to lower the output impedance of the power source connected to the input pin (VCC). Increased power supply output impedance can cause input voltage (VCC) instability, and may negatively impact oscillation and ripple rejection characteristics. Therefore, be certain to establish an input capacitor in close proximity to the VCC and GND pins. Select a low-ESR capacitor with the required ripple current capacity and the capability to withstand temperature changes without wide tolerance fluctuations. The ripple current IRMSS is determined using equation (10).

IRMS = IOUT

$$\times \sqrt{\text{VOUT (VCC-VOUT)}}$$

[A]  $\cdot \cdot \cdot \cdot$  (10)

Also, be certain to ascertain the operating temperature, load range and MOSFET conditions for the application in which the capacitor will be used, since capacitor performance is heavily dependent on the application's input power characteristics, substrate wiring and MOSFET gate drain capacity.

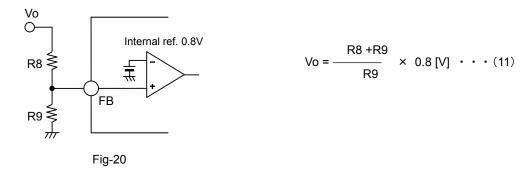

#### (4) Feedback resistor design

Please refer to the following equation in determining the proper feedback resistance. The recommended setting is in a range between  $10k\Omega$  and  $330k\Omega$ . Resistance less than  $10k\Omega$  risks decreased power efficiency, while setting the resistance value higher than  $330k\Omega$  will result in an internal error amp input bias current of 0.2uA increasing the offset voltage.

#### (5) Setting switching frequency

The triangular wave switching frequency can be set by connecting a resistor to the RT 15(33) pin. The RT sets the frequency by adjusting the charge/discharge current in relation to the internal capacitor. Refer to the figure below in determining proper RT resistance, noting that the recommended resistance setting is between  $50k\Omega$  and  $130k\Omega$ . Settings outside this range may render the switching function inoperable, and proper operation of the controller overall cannot be guaranteed when unsupported resistance values are used.

Fig-21 RT vs. switching frequency

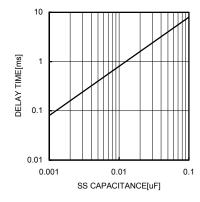

## (6) Setting the soft start delay

The soft start function is necessary to prevent an inrush of coil current and output voltage overshoot at startup. The figure below shows the relation between soft start delay time and capacitance, which can be calculated using equation (12) at right.

TSS =

$$\frac{1000 \text{ (Mp.)} \cdot 10000}{1000 \text{ (SS}(10 \,\mu\text{ A Typ.)})} [\text{sec}] \cdot \cdot \cdot (12)$$

Fig-22 SS capacitance vs. delay time

Recommended capacitance values are between 0.01uF and 0.1uF. Capacitance lower than 0.01uF may generate output overshoots. Please use high accuracy components (such as X5R) when implementing sequential startups involving other power sources. Be sure to test the actual devices and applications to be used, since the soft start time varies, depending on input voltage, output voltage and capacitance, coils and other characteristics.

## (7) Setting over current detection values

The current limit value (ILimit) is determined by the resistance of the RCL established between CL and VCCCL.

There are 2 current limit function (ON/OFF control type and OFF latch type) toggled by LOFF pin.

## • LOFF=L (0<LOFF<1V): Off Latch Type Current Limit

The output becomes OFF and latched when SS=H and, current limit operation, and the output voltage is less than or equal to 70% of Vo. The OFF latch is deactivated by re-inputting EN signal or VCC control input (switch OFF and ON once more).

## · LOFF=H (1<LOFF<VREG5): ON/OFF Control Type Current Limit

When the current goes beyond the threshold value, the current can be limited by reducing the ON Duty Cycle. When the load goes back to the normal operation, the output voltage also becomes back on to the specific level.

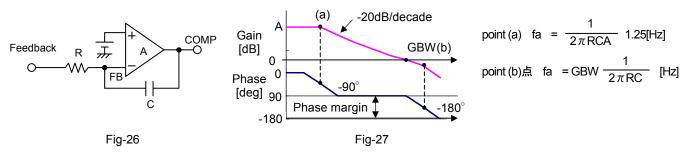

## (8) Method for determining phase compensation

Conditions for application stability

Feedback stability conditions are as follows:

• When gain is 1 (0dB) and phase shift is 150° or less (i.e., phase margin is at least 30°):

a dual-output high-frequency step-down switching regulator is required

Additionally, in DC/DC applications, sampling is based on the switching frequency; therefore, overall GBW may be set at no more than 1/10 the switching frequency. In summary, target characteristics for application stability are:

- Phase shift of 150° or less (i.e., phase margin of 30° or more) with gain of 1 (0dB)

- GBW (i.e., gain 0dB frequency) no more than 1/10 the switching frequency.

Stability conditions mandate a relatively higher switching frequency, in order to limit GBW enough to increase response.

The key to achieving successful stabilization using phase compensation is to cancel the secondary phase margin/delay (-180°) generated by LC resonance, by employing a dual phase lead. In short, adding two phase leads stabilizes the application.

GBW (the frequency at gain 1) is determined by the phase compensation capacitor connected to the error amp. Thus, a larger capacitor will serve to lower GBW if desired.

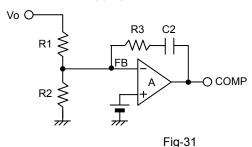

## ① General use integrator (low-pass filter) ② Integrator open loop characteristics

The error amp is provided with phase compensation similar to that depicted in figures ① and ② above and thus serves as the system's low-pass filter.

In DC/DC converter applications, R is established parallel to the feedback resistance.

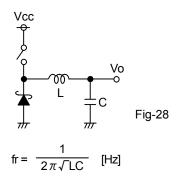

When electrolytic or other high-ESR output capacitors are used:

Phase compensation is relatively simple for applications employing high-ESR output capacitors (on the order of several Ω). In DC/DC converter applications, where LC resonance circuits are always incorporated, the phase margin at these locations is -180°. However, wherever ESR is present, a 90° phase lead is generated, limiting the net phase margin to -90° in the presence of ESR. Since the desired phase margin is in a range less than 150°, this is a highly advantageous approach in terms of the phase margin. However, it also has the drawback of increasing output voltage ripple components.

## 3 LC resonance circuit

Resonance point phase margin -180°

#### 4 ESR connected

fr =

$$\frac{\text{resonance point1}}{2\pi\sqrt{\text{LC}}}$$

[Hz] : Resonance Point

fesr =  $\frac{1}{2\pi\text{ResrC}}$  [Hz] :Zero

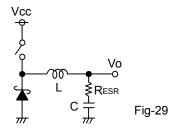

Since ESR changes the phase characteristics, only one phase lead need be provided for high-ESR applications. Please choose one of the following methods to add the phase lead.

## 5 Add C to feedback resistor

Phase lead fz =  $\frac{1}{2\pi \text{C1R1}}$  [Hz]

## 6 Add R3 to aggregator

Phase lead fz = -

Set the phase lead frequency close to the LC resonance frequency in order to cancel the LC resonance.

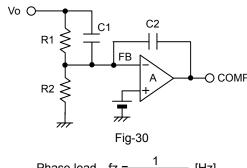

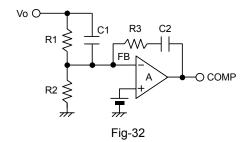

When using ceramic, OS-CON, or other low-ESR capacitors for the output capacitor:

Where low-ESR (on the order of tens of  $m\Omega$ ) output capacitors are employed, a two phase-lead insertion scheme is required, but this is different from the approach described in figure 3~6, since in this case the LC resonance gives rise to a 180° phase margin/delay. Here, a phase compensation method such as that shown in figure 7 below can be implemented.

## Phase compensation provided by secondary (dual) phase lead

Phase lead fz1 =

$$\frac{1}{2\pi R1C1}$$

[Hz]

Phase lead fz2 =  $\frac{1}{2\pi R3C2}$  [Hz]

LC resonance frequency fr =  $\frac{1}{2\pi \sqrt{LC}}$  [Hz]

Once the phase-lead frequency is determined, it should be set close to the LC resonance frequency. This technique simplifies the phase topology of the DCDC Converter. Therefore, it might need a certain amount of trial-and-error process. There are many factors(The PCB board layout, Output Current, etc.)that can affect the DCDC characteristics. Please verify and confirm using practical applications.

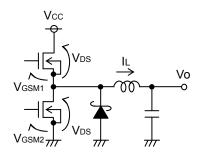

## (9) MOSFET selection

Fig-33

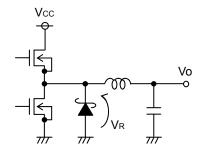

## (10) Schottky barrier diode selection

Fig-34

#### FET uses Nch MOS

- · VDS>Vcc

- VGSM1>BOOT-SW interval voltage

- VGSM2>VREG5

- Allowable current > voltage current + ripple current

- XShould be at least the over current protection value

- \*\*Select a low ON-resistance MOSFET for highest efficiency

- Reverse voltage VR>Vcc

- Allowable current > voltage current + ripple current

※Should be at least the over current protection value

※Select a low forward voltage, fast recovery diode for highest efficiency

- The shoot-through may happen when the input parasitic capacitance of FET is extremely big or the Duty ratio is less than or equal to 10%. Less than or equal to 1000pF input parasitic capacitance is recommended. Please confirm operation on the actual application since this character is affected by PCB layout and components.

## (11) Sequence function

## Circuit diagram

## VCC VREG5 VREG5 OUTH1 BOOT1 VCC BOOT2 OUTH2 Vo2 Vo<sub>1</sub> SW1 SW2 OUTL1 OUTL2 DGND1 DGND2 FB1 FB2 COMP1 COMP2 SS<sub>1</sub> SS2 DET2 DET1 STB EN1 EN2 GND

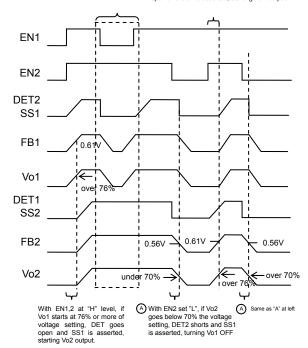

# Timing chart

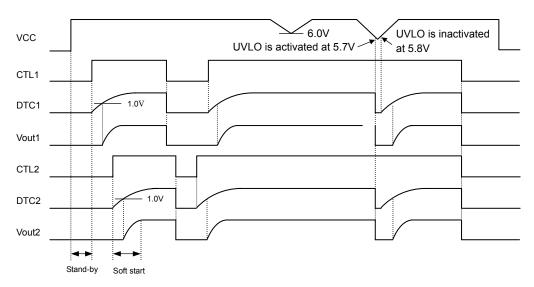

With EN1, 2 at "H" level, when EN1 goes "L", Vo1 turns OFF, but Vo2 output continues.

When EN1 stays "H" and EN2 returns to "H", DET1 is in open state; thus SS2 is asserted, and Vo2 output starts. If Vo2 is 76% of the voltage setting or higher, DET2 goes open and SS1 is asserted, starting Vo1 output.

Fig-35 Fig-36

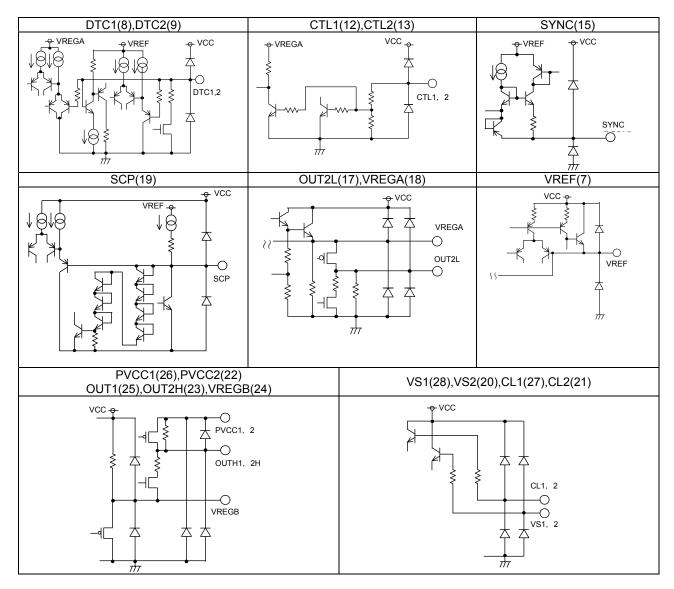

| 1(13), 27(48)PIN (SW1, SW2)<br>29(2), 35(11)PIN (BOOT2, BOOT1)<br>28(1), 36(15)PIN (OUTH1, OUTH2) | 2(14), 26(47)PIN (DGND1, DGND2)<br>3(15), 25(46)PIN (OUTL1, OUTL2)<br>24(44) VREG5 / 4(17)VREG5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14(31)PIN (LOFF)                                                       |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| BOOT □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □                                                          | OUTL DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VREG5  LOFF  172.2k  100k  135.8k  /////////////////////////////////// |

| 16(34)PIN (SYNC)                                                                                  | 6(21), 21(39)PIN (FB1, FB2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8(23), 19(37)PIN (SS1, SS2)                                            |

| VREG5  SYNC                                                                                       | VREG5 / VREG5A  The state of t | VREG5<br>/ VREG5A<br>SS  2k<br>\$50k                                   |

| 10(25), 11(26), 12(27)PIN<br>(STB, EN1, EN2)                                                      | 9(24), 18(36)PIN (DET1, DET2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15(33)PIN (RT)                                                         |

| VCC<br>STB<br>172.2k ₹ 100k<br>135.8k ₹ 100k                                                      | VREG5 / VREG5A  DET 10k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VREG5                                                                  |

| 17(35)PIN (LLM)                                                                                   | 30(3), 34(10)PIN (CL2, CL1)<br>31(5), 33(8)PIN (VCCCL2, VCCCL1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7(22), 20(38)PIN (COMP1, COMP2)                                        |

| VREG5A  LLM   308k                                                                                | VCCCL VCCCL Sp. 5k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VREG5<br>/ VREG5A<br>20 Ω<br>SkΩ<br>S5kΩ                               |

| 22(41)PIN (EXTV, CC)<br>24(44)PIN (VREG5)                                                         | 5(19)PIN (VREG33)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4(17)DIN (VREG5A)                                                      |

| VCC  EXTVCC VCC  VREG5 746.32k  \$255k                                                            | VCC<br>VREG5A<br>VREG33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VCC<br>VREG5A                                                          |

#### Operation notes

#### 1) Absolute maximum ratings

Exceeding the absolute maximum ratings for supply voltage, operating temperature or other parameters can damage or destroy the IC. When this occurs, it is impossible to identify the source of the damage as a short circuit, open circuit, etc. Therefore, if any special mode is being considered with values expected to exceed absolute maximum ratings, consider taking physical safety measures to protect the circuits, such as adding fuses.

#### 2) GND electric potential

Keep the GND terminal potential at the lowest (minimum) potential under any operating condition.

#### 3) Thermal design

Be sure that the thermal design allows sufficient margin for power dissipation (Pd) under actual operating conditions.

#### 4) Inter-pin shorts and mounting errors

Use caution when positioning the IC for mounting on printed surface boards. Connection errors may result in damage or destruction of the IC. The IC can also be damaged when foreign substances short output pins together, or cause shorts between the power supply and GND.

#### 5) Operation in strong electromagnetic fields

Use caution when operating in the presence of strong electromagnetic fields, as this may cause the IC to malfunction.

## 6) Testing on application boards

Connecting a capacitor to a low impedance pin for testing on an application board may subject the IC to stress. Be sure to discharge the capacitors after every test process or step. Always turn the IC power supply off before connecting it to or removing it from any of the apparatus used during the testing process. In addition, ground the IC during all steps in the assembly process, and take similar antistatic precautions when transporting or storing the IC.

#### 7) The output FET

The shoot-through may happen when the input parasitic capacitance of FET is extremely big or the Duty ratio is less than or equal to 10%. Less than or equal to 1000pF input parasitic capacitance is recommended. Please confirm operation on the actual application since this character is affected by PCB layout and components.

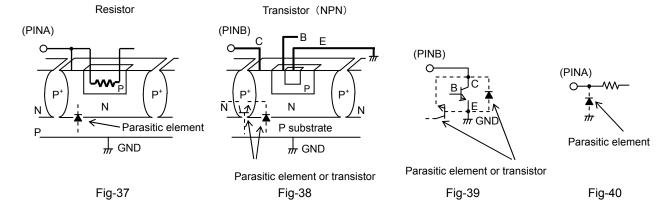

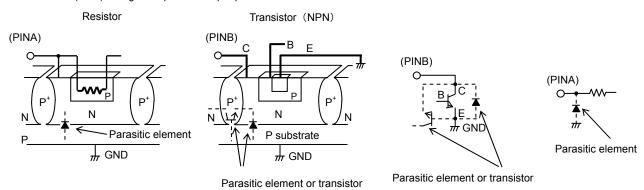

- 8) This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of these P layers with the N layers of other elements, creating a parasitic diode or transistor. Relations between each potential may form as shown in the example below, where a resistor and transistor are connected to a pin:

- O With the resistor, when GND> Pin A, and with the transistor (NPN), when GND>Pin B: The P-N junction operates as a parasitic diode

- O With the transistor (NPN), when GND> Pin B: The P-N junction operates as a parasitic transistor by interacting with the N layers of elements in proximity to the parasitic diode described above.

Parasitic diodes inevitably occur in the structure of the IC. Their operation can result in mutual interference between circuits, and can cause malfunctions, and, in turn, physical damage or destruction. Therefore, do not employ any of the methods under which parasitic diodes can operate, such as applying a voltage to an input pin lower than the (P substrate) GND.

#### 9) GND wiring pattern

When both a small-signal GND and high current GND are present, single-point grounding (at the set standard point) is recommended, in order to separate the small-signal and high current patterns, and to be sure voltage changes stemming from the wiring resistance and high current do not cause any voltage change in the small-signal GND. In the same way, care must be taken to avoid wiring pattern fluctuations in any connected external component GND.

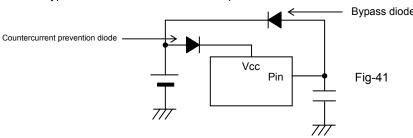

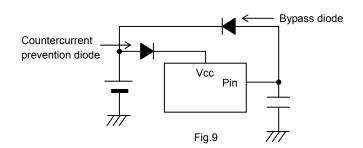

10) In some application and process testing, Vcc and pin potential may be reversed, possibly causing internal circuit or element damage. For example, when the external capacitor is charged, the electric charge can cause a Vcc short circuit to the GND. In order to avoid these problems, limiting output pin capacitance to 100 μ F or less and inserting a Vcc series countercurrent prevention diode or bypass diode between the various pins and the Vcc is recommended.

## 11) Thermal shutdown (TSD)

This IC is provided with a built-in thermal shutdown (TSD) circuit, which is designed to prevent thermal damage to or destruction of the IC. Normal operation should be within the power dissipation parameter, but if the IC should run beyond allowable Pd for a continued period, junction temperature (Tj) will rise, thus activating the TSD circuit, and turning all output pins OFF. When Tj again falls below the TSD threshold, circuits are automatically restored to normal operation. Note that the TSD circuit is only asserted beyond the absolute maximum rating. Therefore, under no circumstances should the TSD be used in set design or for any purpose other than protecting the IC against overheating

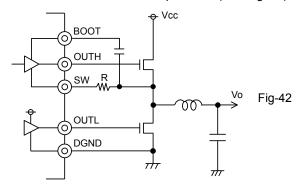

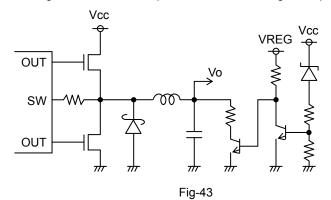

## 12) The SW pin

When the SW pin is connected in an application, its coil counter-electromotive force may give rise to a single electric potential. When setting up the application, make sure that the SW pin never exceeds the absolute maximum value. Connecting a resistor of several  $\Omega$  will reduce the electric potential. (See Fig. 43)

#### 13) Dropout operation

When input voltage falls below approximately output voltage / 0.9 (varying depending on operating frequency) the ON interval on the OUTL side MOS is lost, making boost applications and wrap operation impossible. If a small differential between input and output voltage is envisioned for a prospective application, connect the load such that the SW voltage drops to the GND level. Managing this load requires discharging the SW line capacitance (SW pin capacitance: approx. 500pF; OUTL side MOS D-S capacitance; Schottky capacitance). Supported loads can be calculated using the equation below.

Note that SW line capacitance is lower with smaller loads, and more stable operation is attained when low voltage bias circuits are configured as in the example below (Fig. 44). However, the degree to which line capacitance is reduced or operational stability is attained will vary depending on the board layout and components. Therefore, be certain to confirm the effectiveness of these design factors in actual operation before entering mass production.

15/28

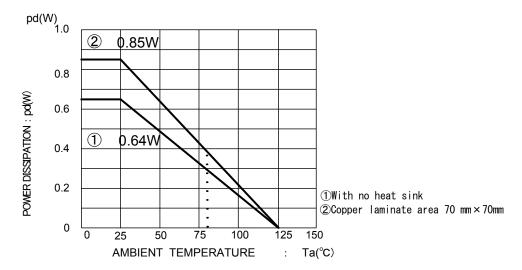

## Power dissipation vs. temperature characteristics

- 1 : Stand-alone IC

- ②: Mounted on Rohm standard board (70mm x 70mm x 1.6mm glass-epoxy board)

- 1 : Stand-alone IC

- ②: Mounted on Rohm standard board (70mm×70mm×1.6mm glass-epoxy board)

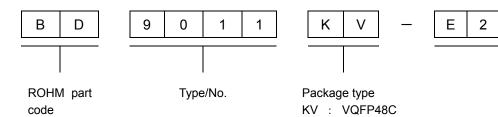

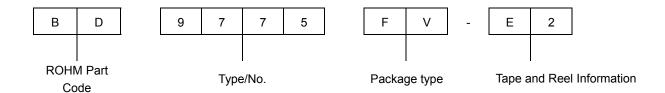

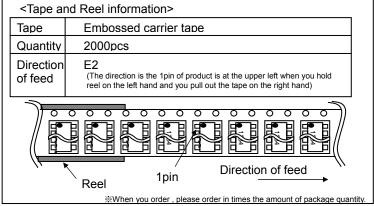

## Part order number

# **HQFN36V**

EKN: HQFN36V

## VQFP48C

## Description

BD9775FV,BD9011EKN/KV is Switching Controller with synchronous rectification(BD9775FV is 1channel synchronous rectification, BD9011EKN/KV is 2channel synchronous rectification.) and wide input range. It can contribute to ecological design(lower power consumption) for most of electronic equipments.

■BD9775FV (1channel synchronous rectification configuration)

## ● Features (BD9775FV)

- 1) 2channel Step-Down DC/DC FET driver

- 2) Synchronous rectification for channel 2

- 3) Able to synchronize to an external clock signal

- 4) Over Current Protection (OCP) by monitoring VDS of P channel FET

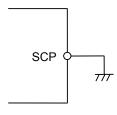

- 5) Short Circuit Protection (SCP) by delay time and latch method

- 6) Under Voltage Lock Out (UVLO)

- 7) Thermal Shut Down (TSD)

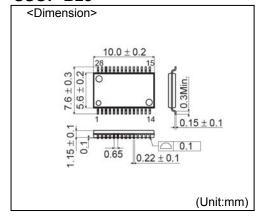

- 8) Package: SSOP-B28

## Applications (BD9775FV)

Car navigation system, Car Audio, Display, Flat TV

## ● Absolute maximum ratings (Ta=25°C)(BD9775FV)

| Parameter                   | Symbol | Limits      | Units |

|-----------------------------|--------|-------------|-------|

| Supply Voltage (VCC to GND) | Vcc    | 36          | V     |

| VREF to GND Voltage         | Vref   | 7           | V     |

| VREGA to GND Voltage        | Vrega  | 7           | V     |

| VREGB to VCC Voltage        | Vregb  | 7           | V     |

| OUT1, OUT2H to VCC Voltage  | Vouth  | 7           | V     |

| OUT2L to GND Voltage        | Voutl  | 7           | V     |

| Power Dissipation           | Pd     | 640(*1)     | mW    |

| Operating Temperature Range | Topr   | -40 to +85  | °C    |

| Storage Temperature Range   | Tstg   | -55 to +125 | °C    |

| Junction Temperature        | Tjmax  | +125        | °C    |

(\*1) Without heat sink, reduce to 6.4mW when Ta=25°C or above

Pd is 850mW mounted on 70x70x1.6mm, and reduce to 8.5mW/°C above 25°C.

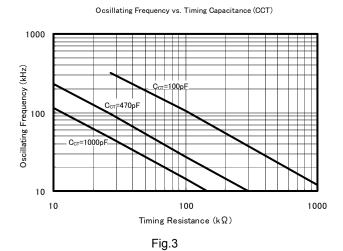

# ●Recommended operating conditions(Ta=-25 to +75°C)(BD9775FV)

| Parameter             | Symbol |     | Units |      |        |  |

|-----------------------|--------|-----|-------|------|--------|--|

| Farameter             | Symbol | MIN | TYP   | MAX  | Office |  |

| Supply Voltage        | VCC    | 6.0 | -     | 30.0 | V      |  |

| Oscillating Frequency | f osc  | 30  | 100   | 300  | KHz    |  |

| Timing Resistance     | RT     | 10  | 27    | 56   | ΚΩ     |  |

| Timing Capacitance    | СТ     | 100 | 470   | 4700 | pF     |  |

# ● Electrical characteristics (Ta=25°C, VCC=13.2V, fosc=100kHz, CTL1=3V, CTL2=3V) (BD9775FV)

| Development              | O. was basel |         | Limits  |         | 1.1  | Condition                  |  |

|--------------------------|--------------|---------|---------|---------|------|----------------------------|--|

| Parameter                | Symbol       | Min.    | Тур.    | Max.    | Unit | Condition                  |  |

| [Whole Device]           |              |         |         |         |      |                            |  |

| Stand-by Current         | Iccst        | _       | _       | 5       | μΑ   | CTL1,CTL2=0V               |  |

| Circuit Current          | Icc          | 2.5     | 4.2     | 7       | mA   | FB1,FB2=0V                 |  |

| [Reference Voltage]      |              |         |         |         |      |                            |  |

| VREF Output Voltage      | Vref         | 2.97    | 3.00    | 3.03    | V    | Io=-1mA                    |  |

| Line Regulation          | DVIi         | _       | _       | 10      | mV   | Vcc=7 to 18V,lo=-1mA       |  |

| Load Regulation          | DVIo         | -       | _       | 10      | mV   | Io=-0.1mA to -2mA          |  |

| Short Output Current     | los          | -60     | -22     | -5      | mA   |                            |  |

| Internal Voltage Regulat | or]          |         |         |         |      |                            |  |

| VREGA Output Voltage     | Vrega        | 4.5     | 5.0     | 5.5     | V    | Switching with COUT=5000pF |  |

| VREGB Output Voltage     | Vregb        | VCC-5.5 | VCC-5.0 | VCC-4.5 | V    | Switching with COUT=5000pF |  |

| VREGB Dropout Voltage    | Vdregb       | _       | 1.8     | 2.2     | V    | VREGB to GND Voltage       |  |

| [Oscillator]             |              |         |         |         |      |                            |  |

| Oscillating Frequency    | fosc         | 90      | 100     | 110     | kHz  | RT=27kΩ,CT=470pF           |  |

| Frequency Tolerance      | Dfosc        | _       | _       | 2       | %    | Vcc=7 to 18V               |  |

| [Synchronized Frequency  | <b>y</b> ]   |         |         |         |      |                            |  |

| Synchronized Frequency   | f osc2       | _       | 120     | _       | kHz  | FIN=120kHz                 |  |

| FIN Threshold Voltage    | Vthfin       | 1.2     | 1.4     | 1.6     | V    |                            |  |

| FIN Input Current        | IFIN         | -1      | _       | 1       | μΑ   | VFIN=1.4V                  |  |

| [Error Amplifier]        |              |         |         | T       | T    |                            |  |

| Threshold Voltage        | Vthea        | 0.98    | 1.00    | 1.02    | V    |                            |  |

| INV Input Bias Current   | Ibias        | -1      | _       | 1       | μΑ   |                            |  |

| Voltage Gain             | Av           | _       | 70      | -       | dB   | DC                         |  |

| Band Width               | Bw           | _       | 2.0     | _       | MHz  | Av=0dB                     |  |

| Maximum Output Voltage   | Vfbh         | 2.2     | 2.4     | 2.6     | V    | INV=0.5V                   |  |

| Minimum Output Voltage   | VfbI         | _       | _       | 0.1     | V    | INV=1.5V                   |  |

| Output Sink Current      | Isink        | 0.5     | 2       | 5.2     | mA   | FB1,2 Terminal             |  |

| Output Source Output     | Isource1     | -170    | -110    | -70     | μΑ   | FB1 Terminal               |  |

| Output Source Current    | Isource2     | -200    | -130    | -85     | μΑ   | FB2 Terminal               |  |

| D                                                      | 0       |          | Limits   |          | 11.20 | Condition                                            |  |

|--------------------------------------------------------|---------|----------|----------|----------|-------|------------------------------------------------------|--|

| Parameter                                              | Symbol  | Min.     | Тур.     | Max.     | Unit  | Condition                                            |  |

| [PWM Comparator]                                       |         | <u> </u> | 1        |          |       |                                                      |  |

| Threshold Voltage at 0%                                | Vth0    | 0.88     | 0.98     | 1.08     | V     | FB Voltage                                           |  |

| Threshold Voltage at 100%                              | Vth100  | 1.88     | 1.98     | 2.08     | V     | FB Voltage                                           |  |

| DTC Input Bias Current                                 | Idtc    | -1       | -        | 1        | μΑ    |                                                      |  |

| 【FET Driver】                                           |         | 1        |          |          |       |                                                      |  |

| Sink Current                                           | Isink   | 20       | 36       | 58       | mA    | VDS=0.4V                                             |  |

| Source Current                                         | Isource | -510     | -320     | -180     | mA    | VDS=0.4V                                             |  |

| ON Resistance                                          | RonN    | 7.0      | 11.0     | 17.8     | Ω     | OUT1,2H,2L : L                                       |  |

| ON Resistance                                          | RonP    | 0.7      | 1.4      | 2.2      | Ω     | OUT1,2H,2L : H                                       |  |

| Rise Time                                              | Tr      | _        | 20       | -        | nsec  | Switching with COUT=5000pF                           |  |

| Fall Time                                              | Tf      | _        | 100      | _        | nsec  | Switching with COUT=5000pF                           |  |

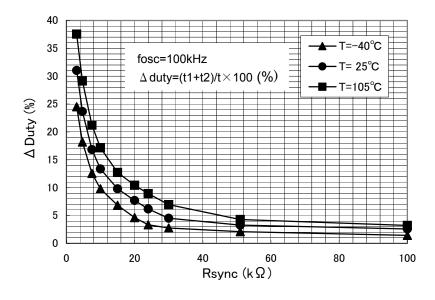

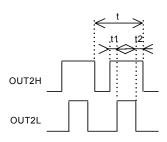

| Driver's Duty Cycle of<br>Synchronous<br>Rectification | ΔDuty   | 42       | 45       | 48       | %     | RSYNC=30K $\Omega$ , 50% of main driver's duty cycle |  |

| SYNC Terminal Voltage                                  | Vsync   | 1.45     | 1.55     | 1.65     | V     | Rsync=30KΩ,FB=1.5V                                   |  |

| Over Current Protection                                | (OCP)]  |          |          | ı        |       |                                                      |  |

| VS Threshold Voltage                                   | Vths    | VCC-0.24 | VCC-0.21 | VCC-0.18 | V     | RCL=21kΩ, the output tern off after detected 8 cycle |  |

|                                                        | IVSH    | -1       | _        | 1        | μΑ    | VS1,VS2=PBU                                          |  |

| VS Input Current                                       | IVSL    | -1       | -        | 1        | μΑ    | VS1,VS2=0V                                           |  |

| CL Input Current                                       | Icl     | 9        | 10       | 11       | μΑ    |                                                      |  |

| [Stand-by]                                             |         |          |          |          |       |                                                      |  |

| Threshold Voltage                                      | VctI    | 1.0      | 1.5      | 2.0      | V     |                                                      |  |

| CL Input Current                                       | Ictl    | 6        | 15       | 30       | μΑ    | CTL1,CTL2=3V                                         |  |

| Short Circuit Protection                               | (SCP)]  | I        |          | I        |       |                                                      |  |

| Timer Start Voltage                                    | Vtime   | 0.6      | 0.7      | 8.0      | V     | INV Voltage                                          |  |

| Threshold Voltage                                      | Vthscp  | 1.92     | 2.00     | 2.08     | V     | SCP Voltage                                          |  |

| Stand-by Voltage                                       | Vstscp  | _        | 10       | 100      | mV    | SCP Voltage                                          |  |

| Source current                                         | Isoscp  | -4.0     | -2.5     | -1.5     | μΑ    | SCP=1.0V                                             |  |

| 【Under Voltage Lock Out                                | (UVLO)] | <u> </u> |          |          |       |                                                      |  |

| Threshold Voltage                                      | Vuvlo   | 5.6      | 5.7      | 5.8      | V     | Vcc sweep down                                       |  |

| Hysteresis<br>Voltage Range                            | DVuvlo  | 0.05     | 0.1      | 0.15     | V     |                                                      |  |

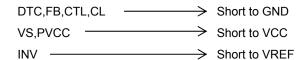

#### Pin Description 1 FB1 VS1 28 (BD9775FV) 2 INV1 CL1 27 PVCC1 26 3 RT 4 OUT1 25 VREGB 24 5 6 GND OUT2H 23 7 VREF PVCC2 22 8 DTC1 CL2 21 9 DTC2 VS2 20 10 INV2 SCP 19 11 FB2 VREGA 18 12 CTL1 OUT2L 17 PGND 16 13 CTL2 14 VCC SYNC 15

## ●Block Diagram (BD9775FV)

Fig.1

# ●PinNo/PinName (BD9775FV)

| Pin<br>No. | Pin<br>Name | Description                                                                                |

|------------|-------------|--------------------------------------------------------------------------------------------|

| 1          | FB1         | Error amplifier output pin (Channel 1)                                                     |

| 2          | INV1        | Error amplifier negative input pin (Channel 1)                                             |

| 3          | RT          | Oscillator frequency adjustment pin connected resistor                                     |

| 4          | СТ          | Oscillator frequency adjustment pin connected capacitor                                    |

| 5          | FIN         | Oscillator synchronization pulse signal input pin                                          |

| 6          | GND         | Low-noise ground                                                                           |

| 7          | VREF        | Reference voltage output pin                                                               |

| 8          | DTC1        | Maximum duty and soft start adjustment pin (Channel 1)                                     |

| 9          | DTC2        | Maximum duty and soft start adjustment pin (Channel 2)                                     |

| 10         | INV2        | Error amplifier negative input pin (Channel 2)                                             |

| 11         | FB2         | Error amplifier output pin (Channel 2)                                                     |

| 12         | CTL1        | Enable/stand-by control input (Channel 1)                                                  |

| 13         | CTL2        | Enable/stand-by control input (Channel 2)                                                  |

| 14         | VCC         | Main power supply pin                                                                      |

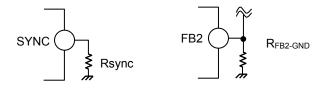

| 15         | SYNC        | Synchronous rectification timing adjustable pin                                            |

| 16         | PGND        | Power ground (connected low-side gate driver and digital ground)                           |

| 17         | OUT2L       | Low-side ( synchronous rectifier ) gate driver output pin (Channel 2)                      |

| 18         | VREGA       | Connected capacitor for internal regulator                                                 |

| 19         | SCP         | Delay time of short circuit protection adjustment pin connected capacitor                  |

| 20         | VS2         | Over current detection voltage monitor pin (connected FET drain, Channel 2)                |

| 21         | CL2         | Over current detection voltage adjustment pin connected capacitor and resistor (Channel 2) |

| 22         | PVCC2       | High-side gate driver power supply input (Channel 2)                                       |

| 23         | OUT2H       | High-side gate driver output pin (Channel 2)                                               |

| 24         | VREGB       | Connected capacitor for internal regulator                                                 |

| 25         | OUT1        | High-side gate driver output pin (Channel 1)                                               |

| 26         | PVCC1       | High-side gate driver power supply input (Channel 1)                                       |

| 27         | CL1         | Over current detection voltage adjustment pin connected capacitor and resistor (Channel 1) |

| 28         | VS1         | Over current detection voltage monitor pin (connected FET drain, Channel 1)                |

## ●FUNCTION EXPLANATION (BD9775FV)

## 1.DC/DC Converter

· Reference Voltage

Stable voltage of compensated temperature, is generated from the power supply voltage (VCC). The reference voltage is 3.0V, the accuracy is  $\pm 1\%$ . Place a capacitor with low ESR (several decades m $\Omega$ ) between VREF and GND.

Internal Regulator A (VREGA)

5V is generated the power supply voltage. The voltage is for the driver of the synchronous rectification's MOSFET. Place a capacitor with low ESR (several decades  $m\Omega$ ) between VREGA and PGND.

#### Internal regulator B (VREGB)

(VCC-5V) is generated from the power supply voltage. The voltage is for the driver of the main MOSFET switch. Place a capacitor with low ESR (several decades  $m\Omega$ ) between VREGB and PVCC.

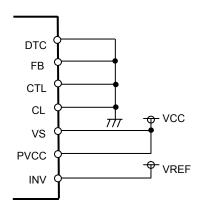

#### Oscillator

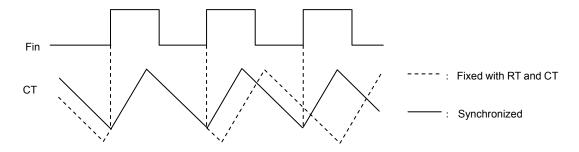

Placing a resistor and a capacitor to RT and CT, respectively, generates two triangle waves for both cannels, and each wave is opposite phase. The waves are input to the PWM comparators for CH1 and CH2. Also, the oscillating frequency can be slightly adjusted (less than 20%) by putting external clock pulse into Fin pin, which is higher frequency than the fixed one.

#### Error Amplifier

It amplifies the difference, between the establish output voltage and the actual output one detected at INV. And amplified voltage comes out from FB. The comparing voltage is 1.0V and the accuracy is  $\pm 2\%$ . The phase can be compensated externally by placing a resistor and a capacitor between INV and FB.

## PWM Comparator

It converts the output voltage from error amplifier into PWM waveform, then output to MOSFET driver.

#### MOSFET Driver

The main drivers (OUT1, OUT2H) are for P-channel MOSFETs, and the driver (OUT2L) for synchronous rectification is for N-channel MOSFET. The values of output voltage are clamp to VREGB, VREGA, respectively. All drivers' output configurations are push-pull type. In addition, the output current capability is 36mA for the sink current and 320mA (Vds=0.4V) for the source current.

#### 2.Channel Control

Each output can be individually turned on or off with CTL1 and CTL2. When the CTL is "H" (more than 1.5V), it becomes turned on

## 3.Protection

## Over Current Protection (OCP)

When detected over current (detecting drop voltage of the main MOSFET's ON resistance), the MOSFET switch becomes turned off, and the energy on DTC pin is discharged. After discharged, the output restarts automatically. The level of the OCP detection threshold can be set by the resistance, which is connected between VCC and CL.

#### Short Circuit Protection (SCP)

When either output goes down and the voltage on INV pin gets lower than 0.7V, a capacitor placed on SCP is started to charge.

When the SCP pin becomes more than 2.0V, the main MOSFET switches of both outputs are turned off; then, the outputs are latched. While they are latched, the IC can be reset by restarting VCC or CTL, or discharging SCP.

## Under Voltage Lock Out (UVLO)