The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# H8S/2678 Group, H8S/2678R Group, H8S/2676 F-ZTAT™

Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8S Family/H8S/2600 Series

| H8S/2676  | HD64F2676  |

|-----------|------------|

|           | HD6432676  |

| H8S/2675  | HD6432675  |

| H8S/2674R | HD6412674R |

| H8S/2673  | HD6432673  |

| H8S/2670  | HD6412670  |

|           |            |

lardware

Rev. 3.00

Revision Date: Mar 17, 2006

RenesasTechnology www.renesas.com

### **General Precautions on Handling of Product**

### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

### Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Main Revisions in This Edition

- 5. Contents

- 6. Overview

- 7. Description of Functional Modules

- · CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 8. List of Registers

- 9. Electrical Characteristics

- 10. Appendix

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

### **Preface**

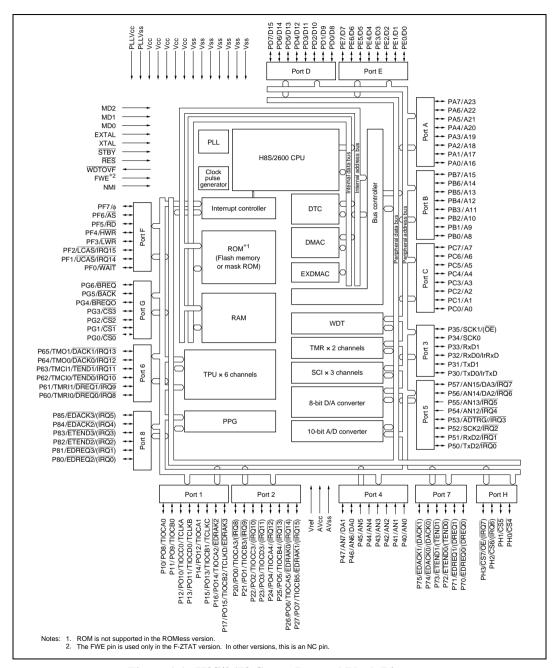

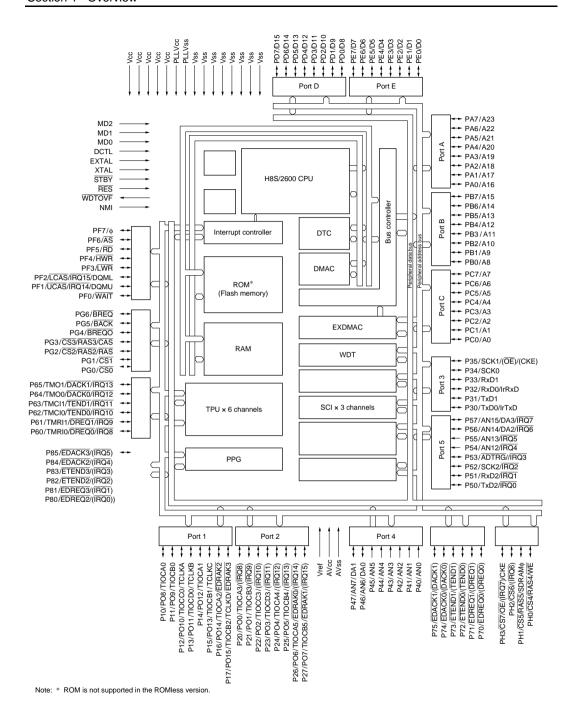

The H8S/2678 Group and H8S/2678R Group are microcomputers (MCU) made up of the H8S/2600 CPU employing Renesas' original architecture as their cores, and the peripheral functions required to configure a system.

The H8S/2600 CPU has an internal 32-bit configuration, sixteen 16-bit general registers, and a simple and optimized instruction set for high-speed operation. The H8S/2600 CPU can handle a 16-Mbyte linear address space.

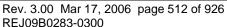

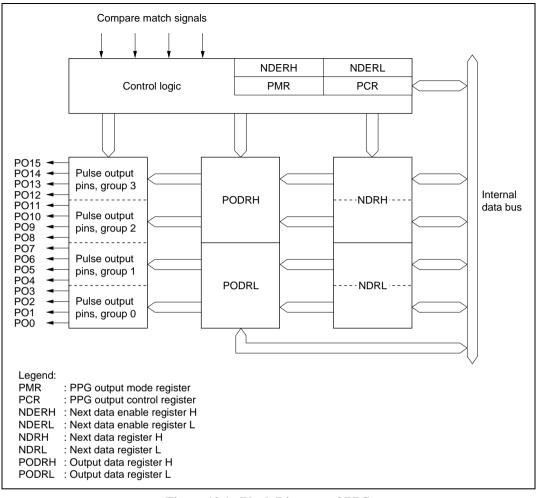

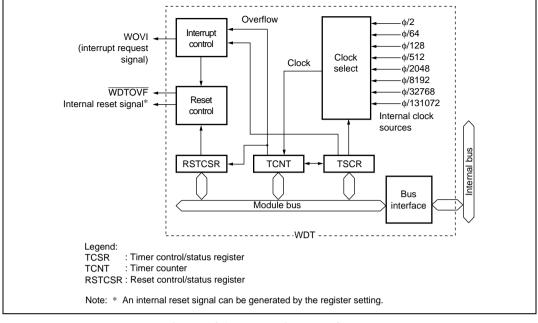

This LSI is equipped with direct memory access controller (DMAC and EXDMAC) and data transfer controller (DTC) bus masters, ROM and RAM, a 16-bit timer pulse unit (TPU), a programmable pulse generator (PPG), an 8-bit timer (TMR), a watchdog timer (WDT), a serial communication interface (SCI and IrDA), a 10-bit A/D converter, an 8-bit D/A converter, and I/O ports as on-chip peripheral modules required for system configuration

A high functionality bus controller is also provided, enabling fast and easy connection of DRAM, SDRAM, and other kinds of memory.

A single-power flash memory (F-ZTAT<sup>TM\*</sup>) version and masked ROM version are available for this LSI's ROM. The F-ZTAT version provides flexibility as it can be reprogrammed in no time to cope with all situations from the early stages of mass production to full-scale mass production. This is particularly applicable to application devices with specifications that will most probably change.

This manual describes this LSI's hardware.

Note: \* F-ZTAT<sup>TM</sup> is a trademark of Renesas Technology Corp.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Target users are expected to understand the fundamentals of

electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the target users.

Refer to the H8S/2600 Series, H8S/2000 Series Programming Manual for a

detailed description of the instruction set.

Notes on reading this manual:

In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

Rev. 3.00 Mar 17, 2006 page v of I

In order to understand the details of the CPU's functions

Read the H8S/2600 Series, H8S/2000 Series Programming Manual.

In order to understand the details of a register when its name is known

Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 23, List of Registers.

Examples: Register name: The following notation is used for cases when the same or a

similar function, e.g. 16-bit timer pulse unit or serial

communication, is implemented on more than one channel: XXX\_N (XXX is the register name and N is the channel

number)

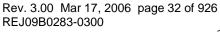

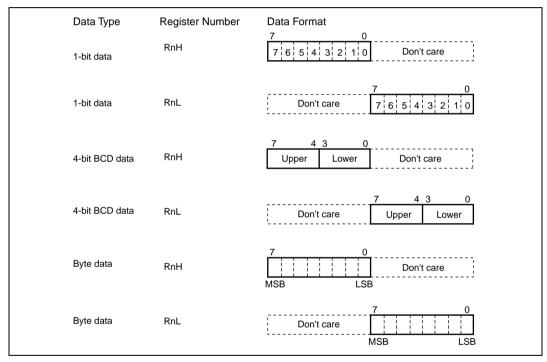

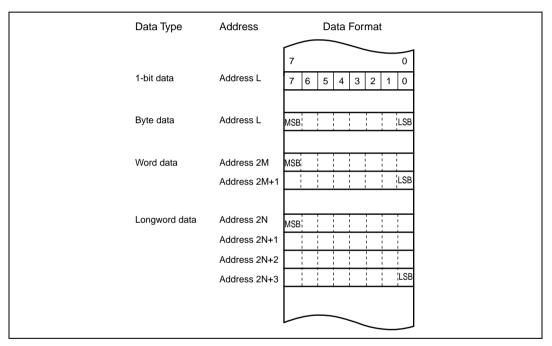

Bit order: The MSB is on the left and the LSB is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal:  $\overline{xxxx}$

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com

H8S/2678 Group and H8S/2678R Group manuals:

| Document Title                                      | Document No. |

|-----------------------------------------------------|--------------|

| H8S/2678 Group, H8S/2678R Group Hardware Manual     | This manual  |

| H8S/2600 Series, H8S/2000 Series Programming Manual | REJ09B0139   |

User's manuals for development tools:

| Document Title                                                                                          | Document No. |

|---------------------------------------------------------------------------------------------------------|--------------|

| H8S, H8/300 Series C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual                   | REJ10B0058   |

| H8S, H8/300 Series Simulator/Debugger User's Manual                                                     | ADE-702-037  |

| H8S, H8/300 Series High-performance Embedded Workshop,<br>High-performance Debugging Interface Tutorial | ADE-702-231  |

| High-performance Embedded Workshop User's Manual                                                        | ADE-702-201  |

# Main Revisions in This Edition

| Item                             | Page   | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| All                              | _      | All references to Hitachi, Hitachi, Ltd., Hitachi<br>Semiconductors, and other Hitachi brand names changed to<br>Renesas Technology Corp. Designation for categories<br>changed from "series" to "group"                                                                                                                                                                            |  |  |

| 6.2 Input/Output Pins            | 124    | Symbols amended                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Table 6.1 Pin Configuration      |        | Upper column address strobe/upper data mask enable (Before) $\overline{\text{UCAS}}/\overline{\text{DQMU}} \rightarrow \text{(After)} \ \overline{\text{UCAS}}/\overline{\text{DQMU}}$                                                                                                                                                                                              |  |  |

|                                  |        | Lower column address strobe/upper data mask enable (Before) $\overline{\text{LCAS}}/\overline{\text{DQML}} \to (\text{After}) \ \overline{\text{LCAS}}/\overline{\text{DQML}}$                                                                                                                                                                                                      |  |  |

|                                  | 124    | I/O description amended                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                  |        | Data Transfer acknowledge 0 (DMAC) (Before) $\overline{\text{DACK0}} \rightarrow$ (After) $\overline{\text{Output}}$                                                                                                                                                                                                                                                                |  |  |

| 7.5.1 Transfer                   | 288    | Table 7.4 amended                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Modes                            |        | Transfer Mode Transfer Source Remarks                                                                                                                                                                                                                                                                                                                                               |  |  |

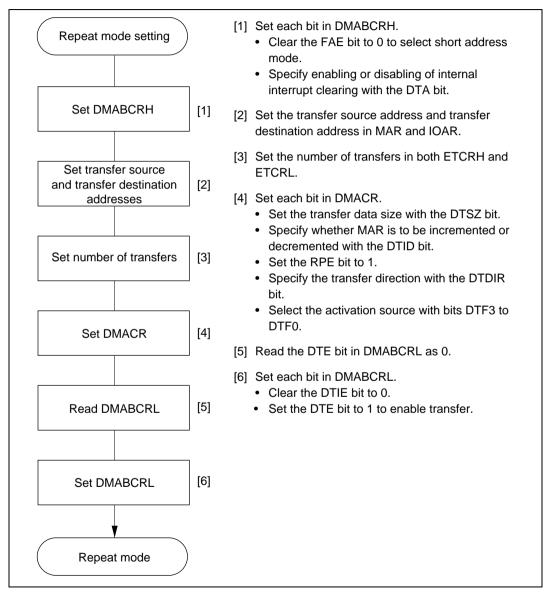

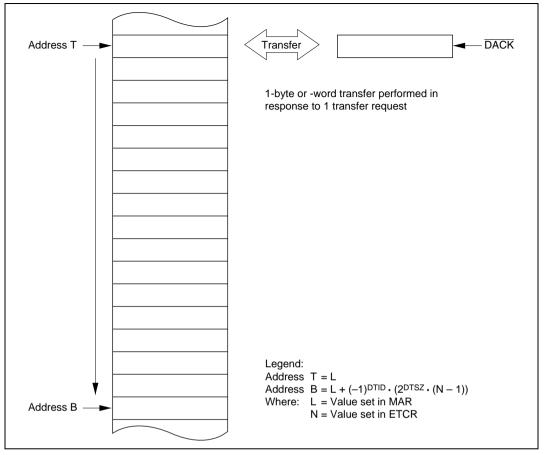

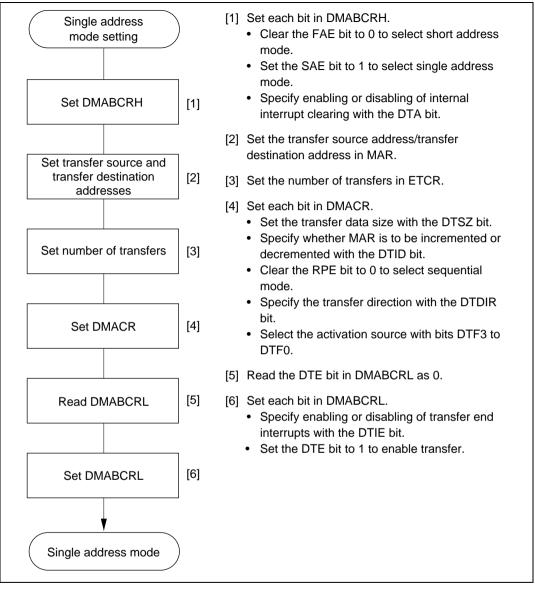

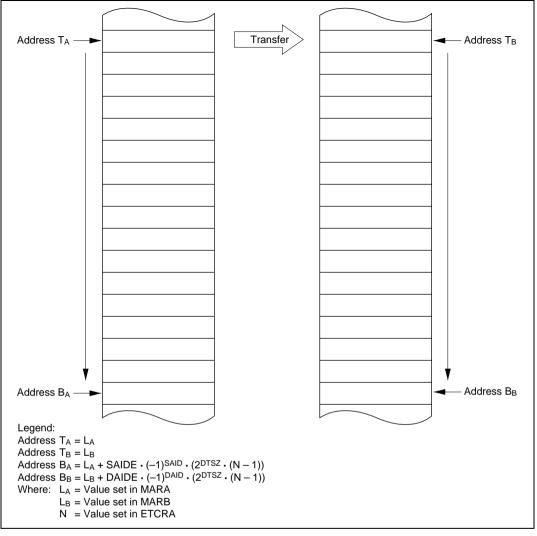

| Table 7.4 DMAC<br>Transfer Modes |        | Short address mode  (1) Sequential mode  • Memory address incremented or decremented by 1 or 2  • Number of transfers: 1 to 65,536 (2) Idle mode • Memory address fixed • Number of transfers: 1 to 66,536 (3) Repeat mode • Memory address incremented or decremented by 1 or 2  • Continues transfer after sending number of transfers (1 to 256) and restoring the initial value |  |  |

|                                  | 289    | Transfer Mode Transfer Source Remarks  Full Normal mode Auto-request • Max. 2-channel operation, combining channels A and B  (1) Auto-request • Transfer request is internally held  • Number of transfers (1 to 65,536) is continuously sent  • Burst/cycle steal transfer can be selected                                                                                         |  |  |

| Section 10 I/O Ports             | 428 to | Notes amended                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Table 10.1 Port                  | 432    | Modes 3*1, 7                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Functions                        |        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                |  |  |

|                                  | 432    | Notes: 1. Mode 3 is not supported in H8S/2378 Group.                                                                                                                                                                                                                                                                                                                                |  |  |

|                                  |        | 2. These pins are not supported in H8S/2678 Group.                                                                                                                                                                                                                                                                                                                                  |  |  |

| Item                                                    | Page | Revision (See Manual for Details)                                                                                                 |

|---------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 10.2.4 Pin Functions                                    | 445  | P27/PO7/TIOCB5/(IRQ15)/EDRAK1                                                                                                     |

|                                                         |      | Description amended                                                                                                               |

|                                                         |      | (Before) $\overline{\text{IRQ5}}$ interrupt input $\rightarrow$ (After) $\overline{\text{IRQ15}}$ interrupt input                 |

|                                                         | 445  | Note 2 amended                                                                                                                    |

|                                                         |      | Note: 2. IRQ15 input when ITS15 = 1.                                                                                              |

| 10.6.4 Pin Functions                                    | 471  | P61/TMRI1/DREQ1/IRQ9                                                                                                              |

|                                                         |      | Description amended                                                                                                               |

|                                                         |      | The pin function is switched as shown below according to the combination of bit DMACS in PFCR2, bit P61DDR and bit ITS9 in ITSR.  |

|                                                         | 471  | P60/TMRI0/DREQ0/IRQ8                                                                                                              |

|                                                         |      | Description amended                                                                                                               |

|                                                         |      | The pin function is switched as shown below according to the combination of bit DMACS in PFCR2, bit P60DDR; and bit ITS8 in ITSR. |

| 10.7.4 Pin Functions                                    | 477  | P71/DREQ1/EDREQ1                                                                                                                  |

|                                                         |      | Description amended                                                                                                               |

|                                                         |      | The pin function is switched as shown below according to the combination of bit P71DDR and bit DMACS in PFCR2.                    |

|                                                         | 477  | P70/DREQ0/EDREQ0                                                                                                                  |

|                                                         |      | Description amended                                                                                                               |

|                                                         |      | The pin function is switched as shown below according to the combination of bit P70DDR and bit DMACS in PFCR2.                    |

| 10.9.5 Port A Open<br>Drain Control Register<br>(PAODR) | 486  | Note deleted from bit table                                                                                                       |

| 10.9.6 Port Function                                    | 486  | Note * added                                                                                                                      |

| Control Register 1 (PFCR1)                              |      | Note: * Only in H8S/2678R Group.                                                                                                  |

| Item                                                                      | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.15.4 Pin                                                               | 515  | PG3/CS3/RAS3/CAS, PG2/CS2/RAS2/RAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Functions                                                                 |      | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                           |      | The pin function is switched as shown below according to the operating mode, bit EXPE, bit PGnDDR, bit CSnE, and bits RMTS2 to RMTS0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                           | 515  | • PG1/CS1, PG0/CS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                           |      | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                           |      | The pin function is switched as shown below according to the operating mode, bit EXPE, bit PGnDDR, and bit CSnE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10.16.4 Pin                                                               | 520  | • PH1/CS5/RAS5/SDRAMφ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Functions                                                                 |      | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                           |      | The pin function is switched as shown below according to the operating mode, DCTL pin, bit EXPE, bit CS5E, bits RMTS2 to RMTS0, and bit PH1DDR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.1 Features                                                             | 523  | Table 11.1 amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 11.1 TPU                                                            |      | Item Channel 0 Channel 1 Channel 2 Channel 3 Channel 4 Channel 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Functions                                                                 |      | DTC TGR TGR TGR TGR TGR TGR activation compare compare compare compare compare compare match or match or match or match or match or input capture input capture input capture input capture input capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                           |      | DMAC TGRA_0 TGRA_1 TGRA_2 TGRA_3 TGRA_4 TGRA_5 activation compare compare compare compare compare compare match or match |

|                                                                           |      | A/D TGRA_0 TGRA_1 TGRA_2 TGRA_3 TGRA_4 TGRA_5 converter compare compare compare compare compare compare trigger match or |

|                                                                           |      | PPG TGRA_0/ TGRA_1/ TGRA_2/ TGRA_3/ — — trigger TGRB_0 TGRB_1 TGRB_2 TGRB_3 compare compare compare compare match or match or match or match or input capture input capture input capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11.3.9 Timer                                                              | 558  | Bits 7, 6 initial value amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Synchronous Register (TSYR)                                               |      | (Before) - → (After) All 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.3.9 Bit Rate                                                           | 679  | Table 15.2 amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Generator (BRR)                                                           |      | Mode Bit Rate Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Table 15.2<br>Relationships<br>between N Setting in<br>BRR and Bit Rate B |      | Smart Card Interface Mode $B = \frac{\phi \times 10^6}{S \times 2^{2ri\pm 1} \times (N+1)} \qquad \text{Error (\%)} = \left\{ \frac{\phi \times 10^6}{B \times S \times 2^{2ri\pm 1} \times (N+1)} - 1 \right\} \times 100$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Item                             | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

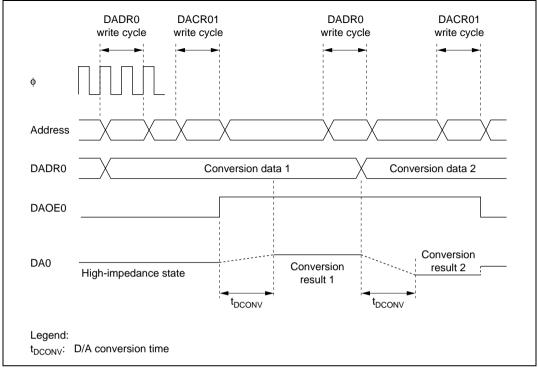

| 17.4 Operation                   | 769  | Description added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                  |      | [2] Set the DAOE0 bit The output value is expressed by the following formula:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                  |      | $\frac{\text{DADR contents}}{256} \times \text{Vref}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

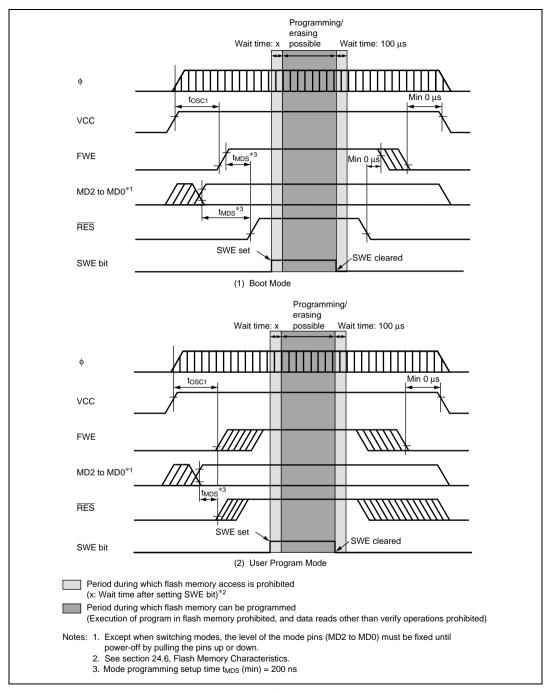

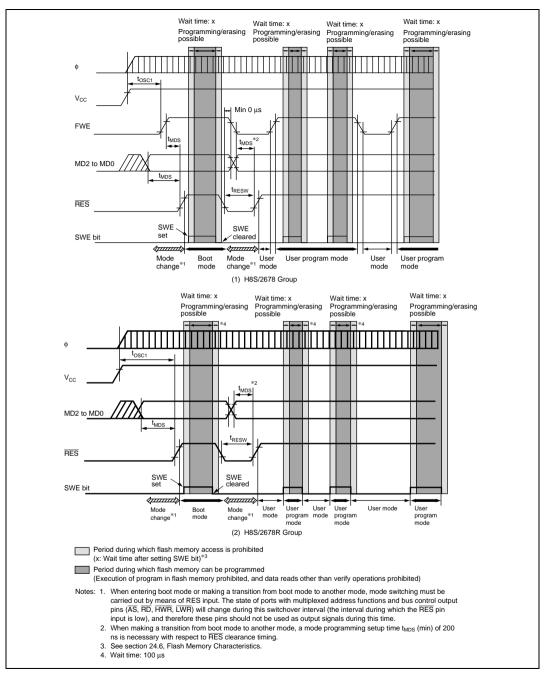

| 19.12 Usage Notes                | 804  | Figure 19.12 amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

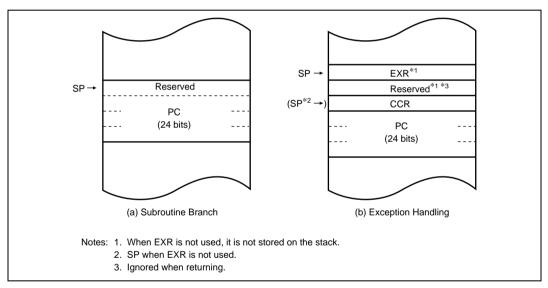

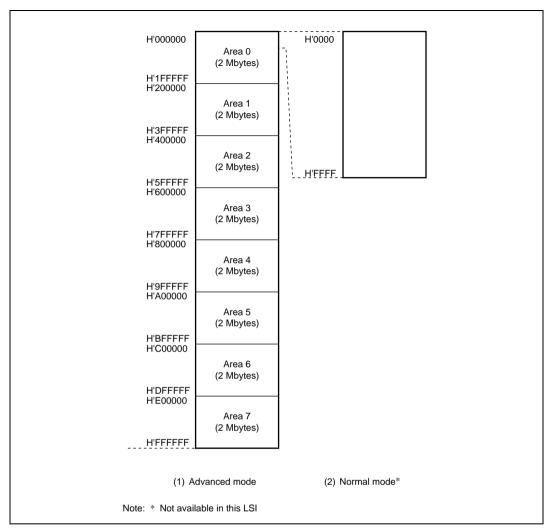

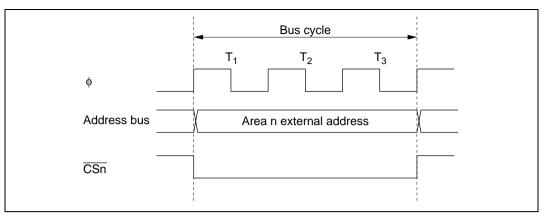

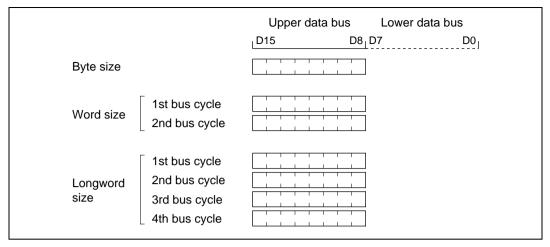

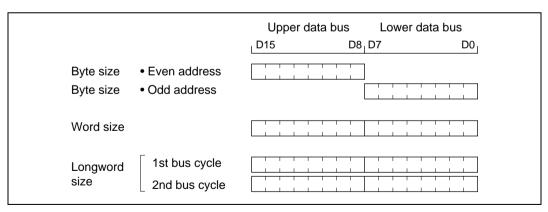

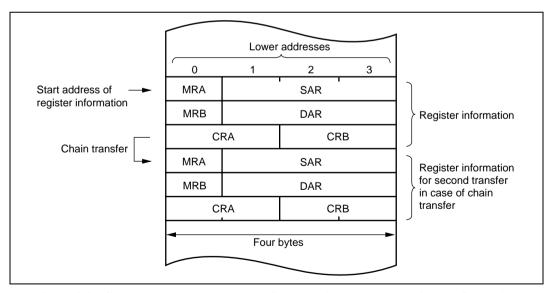

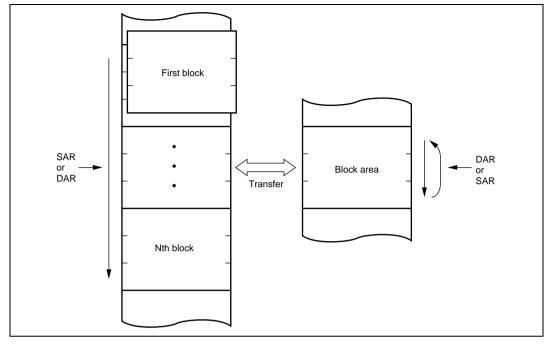

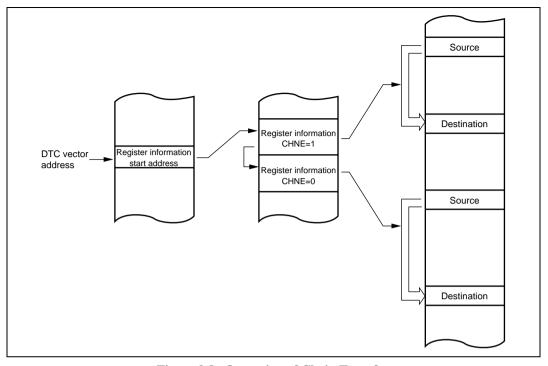

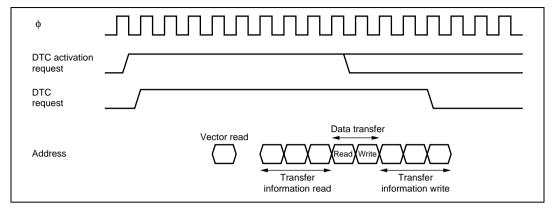

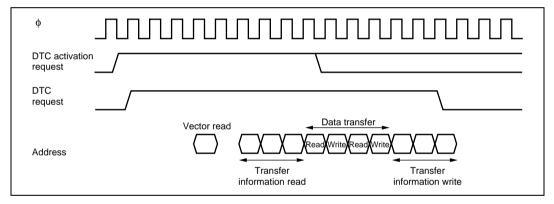

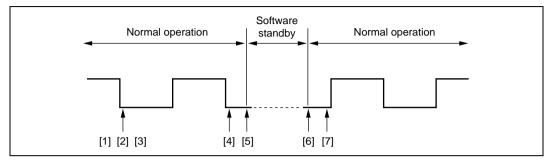

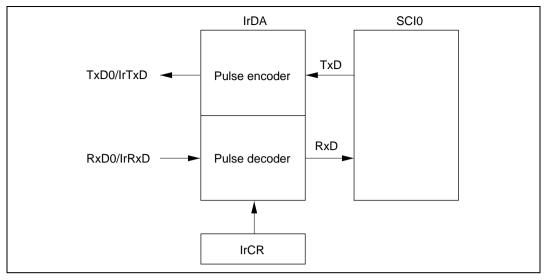

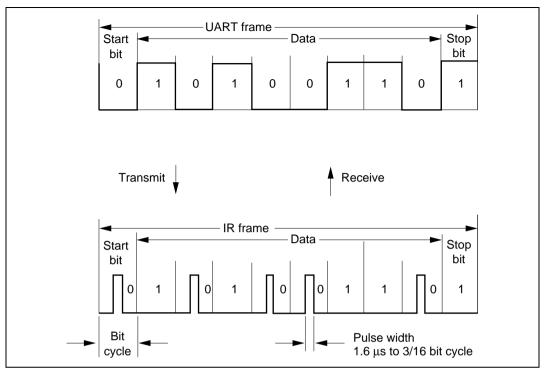

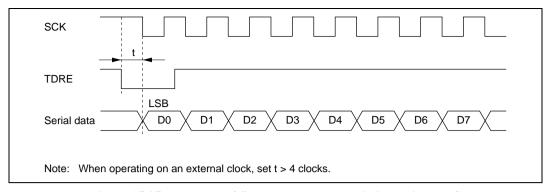

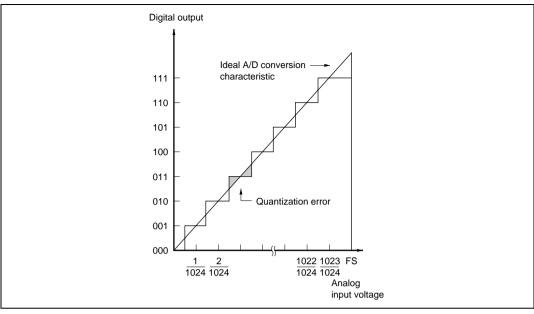

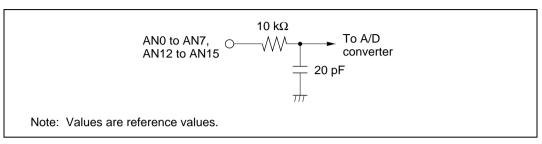

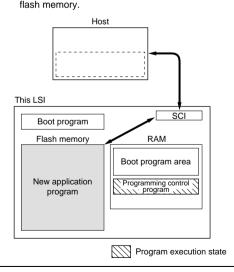

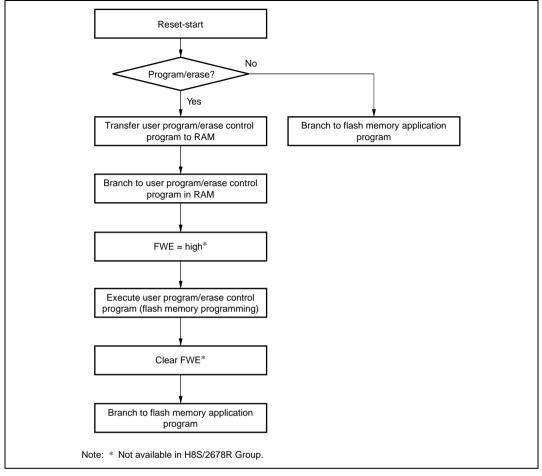

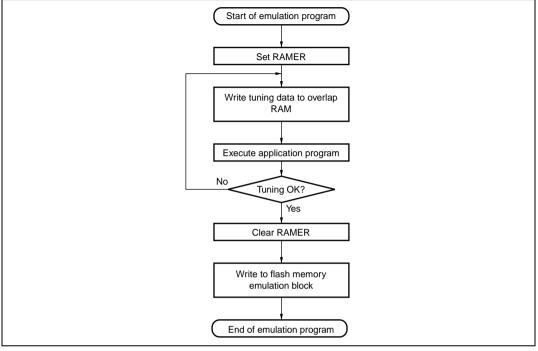

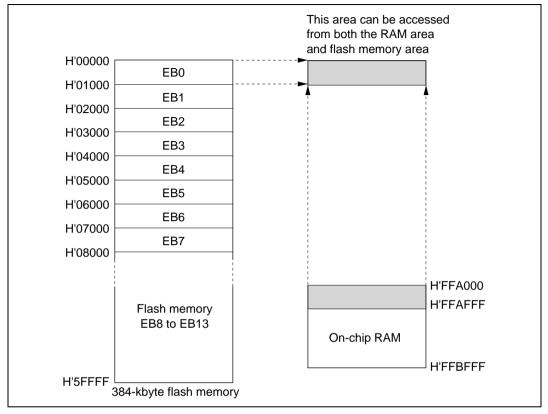

| Figure 19.12 Power-              |      | Programming/<br>erasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |