Data Sheet

#### July 21, 2005

# CMOS Micropower Over/Under Voltage Detector

intersil

The ICL7665S Super CMOS Micropower Over/Under Voltage Detector contains two low power, individually programmable Voltage detectors on a single CMOS chip. Requiring typically  $3\mu$ A for operation, the device is intended for battery-operated systems and instruments which require high or low voltage warnings, settable trip points, or fault monitoring and correction. The trip points and hysteresis of the two voltage detectors are individually programmed via external resistors. An internal bandgap-type reference provides an accurate threshold voltage while operating from any supply in the 1.6V to 16V range.

The ICL7665S, Super Programmable Over/Under Voltage Detector is a direct replacement for the industry standard ICL7665B offering *wider* operating voltage and temperature ranges, *improved* threshold accuracy (ICL7665SA), and temperature coefficient, and *guaranteed* maximum supply current. All improvements are highlighted in the electrical characteristics section. *All critical parameters are guaranteed over the entire commercial and industrial temperature ranges.*

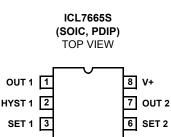

# Pinout

GND

HYST 2

### Features

- Guaranteed 10µA Maximum Quiescent Current Over Temperature

- Guaranteed Wider Operating Voltage Range Over Entire

Operating Temperature Range

- · 2% Threshold Accuracy (ICL7665SA)

- · Dual Comparator with Precision Internal Reference

- 100ppm/°C Temperature Coefficient of Threshold Voltage

- 100% Tested at 2V

- Output Current Sinking Ability ..... Up to 20mA

- Individually Programmable Upper and Lower Trip Voltages and Hysteresis Levels

- · Pb-Free Plus Anneal Available (RoHS Compliant)

## Applications

- Pocket Pagers

- · Portable Instrumentation

- · Charging Systems

- · Memory Power Back-Up

- · Battery Operated Systems

- Portable Computers

- Level Detectors

## **Ordering Information**

| ſ                             |                     |                            | -              |

|-------------------------------|---------------------|----------------------------|----------------|

| PART NUMBER                   | TEMP.<br>RANGE (°C) | PACKAGE                    | PKG.<br>DWG. # |

| ICL7665SACBA*                 | 0 to 70             | 8 Ld SOIC (N)              | M8.15          |

| ICL7665SACBAZ*<br>(See Note)  | 0 to 70             | 8 Ld SOIC (N)<br>(Pb-free) | M8.15          |

| ICL7665SACBAZA*<br>(See Note) | 0 to 70             | 8 Ld SOIC (N)<br>(Pb-free) | M8.15          |

| ICL7665SACPA                  | 0 to 70             | 8 Ld PDIP                  | E8.3           |

| ICL7665SAIBA*                 | -40 to 85           | 8 Ld SOIC (N)              | M8.15          |

| ICL7665SAIBAZA*<br>(See Note) | -40 to 85           | 8 Ld SOIC (N)<br>(Pb-free) | M8.15          |

| ICL7665SAIPA                  | -40 to 85           | 8 Ld PDIP                  | E8.3           |

| ICL7665SCBA*                  | 0 to 70             | 8 Ld SOIC (N)              | M8.15          |

| ICL7665SCBAZ*<br>(See Note)   | 0 to 70             | 8 Ld SOIC (N)<br>(Pb-free) | M8.15          |

| ICL7665SCBAZA*<br>(See Note)  | 0 to 70             | 8 Ld SOIC (N)<br>(Pb-free) | M8.15          |

| ICL7665SCPA                   | 0 to 70             | 8 Ld PDIP                  | E8.3           |

| ICL7665SCPAZ<br>(See Note)    | 0 to 70             | 8 Ld PDIP**<br>(Pb-free)   | E8.3           |

| ICL7665SIBA*                  | -40 to 85           | 8 Ld SOIC (N)              | M8.15          |

| ICL7665SIBAZ*<br>(See Note)   | -40 to 85           | 8 Ld SOIC (N)<br>(Pb-free) | M8.15          |

| ICL7665SIBAZA*<br>(See Note)  | -40 to 85           | 8 Ld SOIC (N)<br>(Pb-free) | M8.15          |

\*Add "-T" suffix for tape and reel.

\*\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

## **Absolute Maximum Ratings**

| Supply Voltage (Note 2)0.3 to +18V<br>Output Voltages OUT1 and OUT20.3V to 18V<br>(with respect to GND) (Note 2) |

|------------------------------------------------------------------------------------------------------------------|

| (with respect to V+) (Note 2)<br>(with respect to V+) (Note 2)                                                   |

| Input Voltages SET1 and SET2 (GND -0.3V) to (V+ V- +0.3V)<br>(Note 2)                                            |

| Maximum Sink Output OUT1 and OUT2                                                                                |

| Maximum Source Output Current<br>HYST1 and HYST2                                                                 |

## **Operating Conditions**

| Temperature Range |              |

|-------------------|--------------|

| ICL7665SC         | 0°C to 70°C  |

| ICL7665SI         | 40°C to 85°C |

| Thermal Resistance (Typical, Note 1)     | θ <sub>JA</sub> (°C/W) |

|------------------------------------------|------------------------|

| PDIP Package*                            | 115                    |

| SOIC Package                             | 160                    |

| Maximum Junction Temperature (Plastic)   |                        |

| Maximum Junction Temperature (CERDIP)    | 175°C                  |

| Maximum Storage Temperature Range65      | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 10s) | 300°C                  |

| (SOIC - Lead Tips Only)                  |                        |

|                                          |                        |

\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

- 1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

- 2. Due to the SCR structure inherent in the CMOS process used to fabricate these devices, connecting any terminal to voltages greater than (V++0.3V) or less than (GND 0.3V) may cause destructive device latchup. For these reasons, it is recommended that no inputs from external sources not operating from the same power supply be applied to the device before its supply is established, and that in multiple supply systems, the supply to the ICL7665S be turned on first. If this is not possible, current into inputs and/or outputs must be limited to ±0.5mA and voltages must not exceed those defined above.

| Electrical Specifications | The specifications below are applicable to both the ICL7665S and ICL7665SA. V+ = 5V, $T_A$ = 25°C, |

|---------------------------|----------------------------------------------------------------------------------------------------|

|                           | Test Circuit Figure 7. Unless Otherwise Specified                                                  |

| PARAMETER                                                              | SYMBOL                                | TES                                                                          | T CONDITIONS                                      | MIN   | TYP  | MAX   | UNITS |

|------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------|-------|------|-------|-------|

| Operating Supply Voltage                                               | V+                                    | ICL7665S                                                                     | T <sub>A</sub> = 25°C                             | 1.6   | -    | 16    | V     |

|                                                                        |                                       |                                                                              | $0^{\bullet}C \leq T_A \leq 70^{\bullet}C$        | 1.8   | -    | 16    | V     |

|                                                                        |                                       |                                                                              | $\text{-25°C} \leq \text{T}_A \leq 85°\text{C}$   | 1.8   | -    | 16    | V     |

|                                                                        |                                       | ICL7665SA                                                                    | $0^{\bullet}C \leq T_A \leq 70^{\bullet}C$        | 1.8   | -    | 16    | V     |

|                                                                        |                                       |                                                                              | $\text{-25°C} \leq \text{T}_{A} \leq \text{85°C}$ | 1.8   | -    | 16    | V     |

| Supply Current                                                         | +                                     | $GND \leq V_{SET1}, V_{SET2}$                                                | ₂ ≤ V+, All Outputs Open Circu                    | iit   |      |       |       |

|                                                                        |                                       | $0^{\bullet}C \leq T_A \leq 70^{\bullet}C$                                   | V+ = 2V                                           | -     | 2.5  | 10    | μA    |

|                                                                        |                                       |                                                                              | V+ = 9V                                           | -     | 2.6  | 10    | μA    |

|                                                                        |                                       |                                                                              | V+ = 15V                                          | -     | 2.9  | 10    | μA    |

|                                                                        |                                       | $-40^{\circ}C \leq T_A \leq 85^{\circ}C$                                     | V+ = 2V                                           | -     | 2.5  | 10    | μA    |

|                                                                        |                                       | V+ = 9V                                                                      | -                                                 | 2.6   | 10   | μA    |       |

|                                                                        |                                       |                                                                              | V+ = 15V                                          | -     | 2.9  | 10    | μA    |

| Input Trip Voltage                                                     | V <sub>SET1</sub>                     | ICL7665S                                                                     |                                                   | 1.20  |      | 1.40  | V     |

|                                                                        | V <sub>SET2</sub>                     | -                                                                            |                                                   | 1.20  | 1.30 | 1.40  | V     |

|                                                                        | V <sub>SET1</sub>                     | ICL7665SA                                                                    |                                                   | 1.275 | 1.30 | 1.325 | V     |

|                                                                        | V <sub>SET2</sub>                     | -                                                                            |                                                   | 1.275 | 1.30 | 1.325 | V     |

| Temperature Coefficient of                                             | $\Delta V_{SET}$                      | ICL7665S                                                                     |                                                   | -     | 200  | -     | ppm   |

| V <sub>SET</sub>                                                       | ΔΤ                                    | ICL7665SA                                                                    | 65SA - 100                                        | 100   | -    | ppm   |       |

| Supply Voltage Sensitivity of<br>V <sub>SET1</sub> , V <sub>SET2</sub> | $\frac{\Delta V_{SET}}{\Delta V_{S}}$ | $\begin{array}{l} R_{OUT1},R_{OUT2},R_{HY3}\\ 2V\leq V+\leq 10V \end{array}$ | <sub>ST1</sub> , R <sub>2HYST2</sub> = 1MΩ,       | -     | 0.03 | -     | %/V   |

## Electrical Specifications The

The specifications below are applicable to both the ICL7665S and ICL7665SA. V+ = 5V,  $T_A = 25^{\circ}C$ , Test Circuit Figure 7. Unless Otherwise Specified (Continued)

| PARAMETER                              | SYMBOL                                   | TEST                                                                                      | CONDITIONS                            | MIN | TYP   | MAX   | UNITS |

|----------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|-----|-------|-------|-------|

| Output Leakage Currents of             | IOLK                                     | $V_{SET}$ = 0V or $V_{SET} \ge 2$                                                         | V                                     | -   | 10    | 200   | nA    |

| OUT and HYST                           | IHLK                                     |                                                                                           |                                       | -   | -10   | -100  | nA    |

|                                        | IOLK                                     | V+ = 15V, T <sub>A</sub> = 70°C                                                           |                                       | -   | -     | 2000  | nA    |

|                                        | IHLK                                     | _                                                                                         |                                       | -   | -     | -500  | nA    |

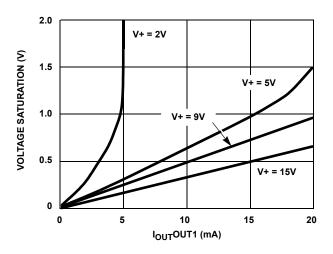

| Output Saturation Voltages             | V <sub>OUT1</sub>                        | V <sub>SET1</sub> = 2V,                                                                   | V+ = 2V                               | -   | 0.2   | 0.5   | V     |

|                                        |                                          | I <sub>OUT1</sub> = 2mA                                                                   | V+ = 5V                               | -   | 0.1   | 0.3   | V     |

|                                        |                                          |                                                                                           | V+ = 15V                              | -   | 0.06  | 0.2   | V     |

| Output Saturation Voltages             | V <sub>HYST1</sub>                       | V <sub>SET1</sub> = 2V,                                                                   | V+ = 2V                               | -   | -0.15 | -0.30 | V     |

|                                        |                                          | I <sub>HYST1</sub> = -0.5mA                                                               | V+ = 5V                               | -   | -0.05 | -0.15 | V     |

|                                        |                                          | V+ = 15V                                                                                  |                                       | -   | -0.02 | -0.10 | V     |

| Output Saturation Voltages             | V <sub>OUT2</sub>                        | V <sub>SET2</sub> = 0V,<br>I <sub>OUT2</sub> = 2mA                                        | V+ = 2V                               | -   | 0.2   | 0.5   | V     |

|                                        |                                          |                                                                                           | V+ = 5V                               | -   | 0.15  | 0.3   | V     |

|                                        |                                          |                                                                                           | V+ = 15V                              | -   | 0.11  | 0.25  | V     |

| Output Saturation Voltages             | V <sub>HYST2</sub>                       | V <sub>SET2</sub> = 2V                                                                    | V+ = 2V, I <sub>HYST2</sub> = -0.2mA  | -   | -0.25 | -0.8  | V     |

|                                        |                                          |                                                                                           | V+ = 5V, I <sub>HYST2</sub> = -0.5mA  | -   | -0.43 | -1.0  | V     |

|                                        |                                          |                                                                                           | V+ = 15V, I <sub>HYST2</sub> = -0.5mA | -   | -0.35 | -0.8  | V     |

| V <sub>SET</sub> Input Leakage Current | ISET                                     | $GND \leq V_{SET} \leq V \text{+}$                                                        |                                       | -   | 0.01  | 10    | nA    |

| $\Delta$ Input for Complete Output     | $\Delta V_{SET}$                         | $R_{OUT} = 4.7 k\Omega$ ,                                                                 | ICL7665S                              | -   | 1.0   | -     | mV    |

| Change                                 |                                          | R <sub>HYST</sub> = 20kΩ,<br>V <sub>OUT</sub> LO = 1% V+,<br>V <sub>OUT</sub> HI = 99% V+ | ICL7665SA                             | -   | 0.1   | -     | mV    |

| Difference in Trip Voltages            | V <sub>SET1</sub> -<br>V <sub>SET2</sub> | R <sub>OUT</sub> , R <sub>HYST</sub> = 1mW                                                |                                       | -   | ±5    | ±50   | mV    |

| Output/Hysteresis                      |                                          | R <sub>OUT</sub> , R <sub>HYST</sub> = 1mW                                                | ICL7665S                              | -   | ±1    | -     | mV    |

| Difference                             |                                          |                                                                                           | ICL7665SA                             | -   | ±0.1  | -     | mV    |

NOTES:

3. Derate above 25°C ambient temperature at 4mW/°C.

4. All significant improvements over the industry standard ICL7665 are highlighted.

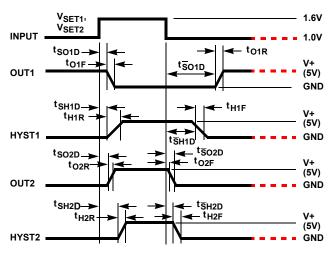

## **AC Electrical Specifications**

| PARAMETER           | SYMBOL             | TEST CONDITIONS                                                                                                 | MIN | TYP | MAX | UNITS |

|---------------------|--------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| OUTPUT DELAY TIMES  |                    |                                                                                                                 |     |     | 1   |       |

| Input Going HI      | t <sub>SO1D</sub>  | V <sub>SET</sub> Switched between 1.0V to 1.6V                                                                  | -   | 85  | -   | μs    |

|                     | t <sub>SH1D</sub>  | $R_{OUT}$ = 4.7kΩ, C <sub>L</sub> = 12pF<br>$R_{HYST}$ = 20kΩ, C <sub>L</sub> = 12pF                            | -   | 90  | -   | μS    |

| t <sub>SO2D</sub> - | -                  | 55                                                                                                              | -   | μS  |     |       |

|                     | t <sub>SH2D</sub>  | -                                                                                                               | -   | 55  | -   | μS    |

| Input Going LO      | t <del>s</del> o1D | V <sub>SET</sub> Switched between 1.6V to 1.0V                                                                  | -   | 75  | -   | μs    |

|                     | t <sub>SH1D</sub>  | R <sub>OUT</sub> = 4.7kΩ, C <sub>L</sub> = 12pF<br>R <sub>HYST</sub> = 20kΩ, C <sub>L</sub> = 12pF              | -   | 80  | -   | μS    |

|                     | t <sub>SO2D</sub>  |                                                                                                                 | -   | 60  | -   | μS    |

|                     | t <sub>SH2D</sub>  | _                                                                                                               | -   | 60  | -   | μs    |

| Output Rise Times   | t <sub>O1R</sub>   | V <sub>SET</sub> Switched between 1.0V to 1.6V                                                                  |     | 0.6 | -   | μS    |

|                     | t <sub>O2R</sub>   | <sup>—</sup> R <sub>OUT</sub> = 4.7kΩ, C <sub>L</sub> = 12pF<br>R <sub>HYST</sub> = 20kΩ, C <sub>L</sub> = 12pF | -   | 0.8 | -   | μS    |

|                     | t <sub>H1R</sub>   |                                                                                                                 | -   | 7.5 | -   | μs    |

|                     | t <sub>H2R</sub>   | _                                                                                                               | -   | 0.7 | -   | μS    |

| Output Fall Times   | t <sub>O1F</sub>   | V <sub>SET</sub> Switched between 1.0V to 1.6V                                                                  | -   | 0.6 | -   | μs    |

|                     | t <sub>O2F</sub>   | R <sub>OUT</sub> = 4.7kΩ, C <sub>L</sub> = 12pF<br>R <sub>HYST</sub> = 20kΩ, C <sub>L</sub> = 12pF              | -   | 0.7 | -   | μs    |

|                     | t <sub>H1F</sub>   |                                                                                                                 | -   | 4.0 | -   | μS    |

|                     | t <sub>H2F</sub>   |                                                                                                                 | -   | 1.8 | -   | μs    |

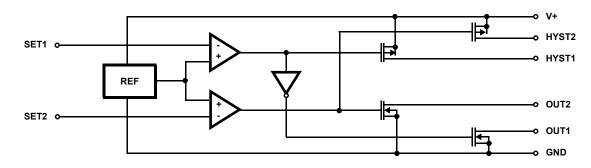

# Functional Block Diagram

$\label{eq:second} \begin{array}{l} \mbox{CONDITIONS} \mbox{ (Note 5)} \\ V_{SET1} > 1.3V, \mbox{ OUT1} \mbox{ Switch ON}, \mbox{ HYST1} \mbox{ Switch OFF} \\ V_{SET2} > 1.3V, \mbox{ OUT2} \mbox{ Switch OFF}, \mbox{ HYST2} \mbox{ Switch OFF} \\ V_{SET2} < 1.3V, \mbox{ OUT2} \mbox{ Switch ON}, \mbox{ HYST2} \mbox{ Switch OFF} \end{array}$

NOTE:

5. See Electrical Specifications for exact thresholds.

## **Typical Performance Curves**

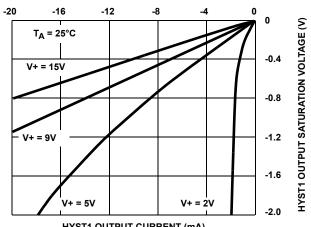

HYST1 OUTPUT CURRENT (mA)

FIGURE 3. HYST1 OUTPUT SATURATION VOLTAGE vs HYST1 OUTPUT CURRENT

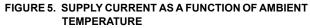

FIGURE 2. OUT2 SATURATION VOLTAGE AS A FUNCTION OF OUTPUT CURRENT

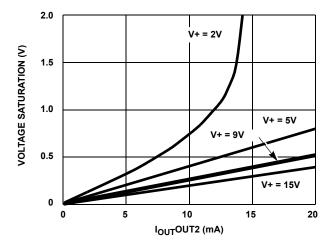

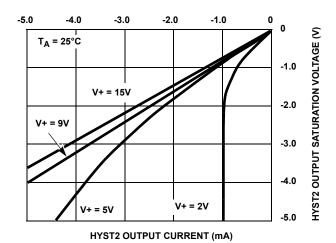

FIGURE 4. HYST2 OUTPUT SATURATION VOLTAGE vs

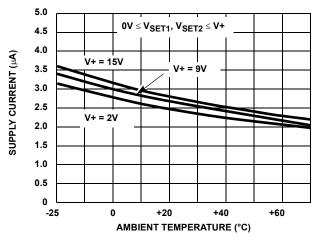

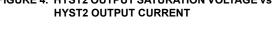

FIGURE 6. SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

# **Detailed Description**

As shown in the Functional Diagram, the ICL7665S consists of two comparators which compare input voltages on the SET1 and SET2 terminals to an internal 1.3V bandgap reference. The outputs from the two comparators drive open-drain N-channel transistors for OUT1 and OUT2, and open-drain P-channel transistors for HYST1 and HYST2 outputs. Each section, the Undervoltage Detector and the Overvoltage Detector, is independent of the other, although both use the internal 1.3V reference. The offset voltages of the two comparators will normally be unequal so  $V_{SET1}$  will generally not quite equal  $V_{SET2}$ .

The input impedance of the SET1 and SET2 pins are extremely high, and for most practical applications can be ignored. The four outputs are open-drain MOS transistors, and when ON behave as low resistance switches to their respective supply rails. This minimizes errors in setting up the hysteresis, and maximizes the output flexibility. The operating currents of the bandgap reference and the comparators are around 100nA each.

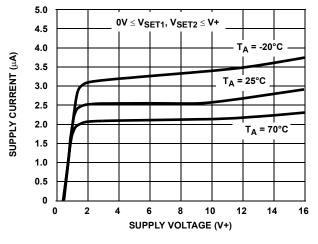

FIGURE 7. TEST CIRCUITS

# Precautions

Junction isolated CMOS devices like the ICL7665S have an inherent SCR or 4-layer PNPN structure distributed throughout the die. Under certain circumstances, this can be triggered into a potentially destructive high current mode. This latchup can be triggered by forward-biasing an input or output with respect to the power supply, or by applying excessive supply voltages. In very low current analog circuits, such as the ICL7665S, this SCR can also be triggered by applying the input power supply extremely rapidly ("instantaneously"), e.g., through a low impedance battery and an ON/OFF switch with short lead lengths. The rate-of-rise of the supply voltage can exceed  $100V/\mu s$  in such a circuit. A low impedance capacitor (e.g.,  $0.05\mu F$  disc ceramic) between the V+ and GND pins of the ICL7665S

can be used to reduce the rate-of-rise of the supply voltage in battery applications. In line operated systems, the rate-ofrise of the supply is limited by other considerations, and is normally not a problem.

If the SET voltages must be applied before the supply voltage V+, the input current should be limited to less than 0.5mA by appropriate external resistors, usually required for voltage setting anyway. A similar precaution should be taken with the outputs if it is likely that they will be driven by other circuits to levels outside the supplies at any time.

FIGURE 8. SWITCHING WAVEFORMS

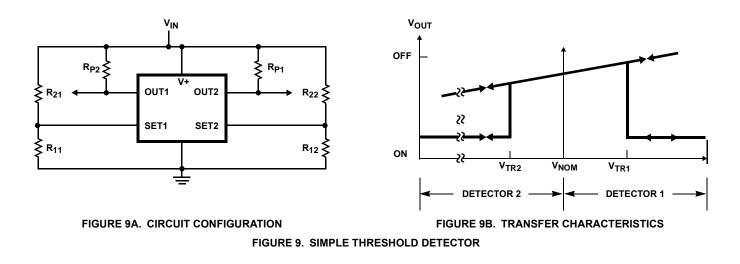

# Simple Threshold Detector

Figure 9 shows the simplest connection of the ICL7665S for threshold detection. From the graph 9B, it can be seen that at low input voltage OUT1 is OFF, or high, while OUT2 is ON, or low. As the input rises (e.g., at power-on) toward  $V_{NOM}$  (usually the eventual operating voltage), OUT2 goes high on reaching  $V_{TR2}$ . If the voltage rises above  $V_{NOM}$  as much as  $V_{TR1}$ , OUT1 goes low. The equation giving  $V_{SET1}$  and  $V_{SET2}$  are from Figure 9A:

$$V_{SET1} = V_{IN} \frac{R_{11}}{(R_{11} + R_{21})}$$

$V_{SET2} = V_{IN} \frac{R_{12}}{(R_{12} + R_{22})}$

Since the voltage to trip each comparator is nominally 1.3V, the value  $V_{\text{IN}}$  for each trip point can be found from

$$V_{TR1} = V_{SET1} \frac{(R_{11} + R_{21})}{R_{11}} = 1.3 \frac{(R_{11} + R_{21})}{R_{11}}$$

for detector 1

and

$$V_{TR2} = V_{SET2} \frac{(R_{12} + R_{22})}{R_{12}} = 1.3 \frac{(R_{12} + R_{22})}{R_{12}}$$

for detector 2

۱

When  $V_{\text{IN}}$  is very close to one of the trip voltage, normal variations and noise may cause it to wander back and forth across this level, leading to erratic output ON and OFF conditions. The addition of hysteresis, making the trip points slightly different for rising and falling inputs, will avoid this condition.

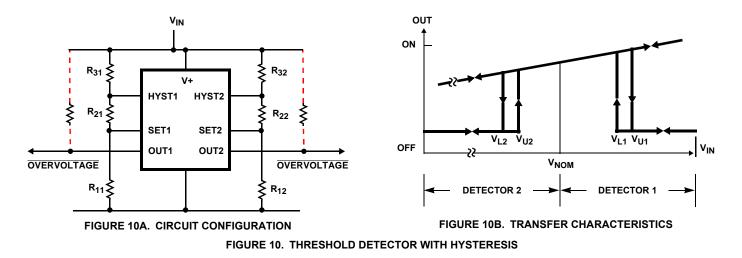

# Threshold Detector with Hysteresis

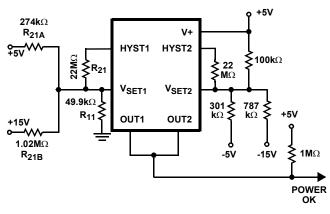

Figure 10A shows how to set up such hysteresis, while Figure 10B shows how the hysteresis around each trip point produces switching action at different points depending on whether  $V_{IN}$  is rising or falling (the arrows indicated direction of change. The HYST outputs are basically switches which short out  $R_{31}$  or  $R_{32}$  when  $V_{IN}$  is above the respective trip point. Thus if the input voltage rises from a low value, the trip point will be controlled by  $R_{1N}$ ,  $R_{2N}$ , and  $R_{3N}$ , until the trip point is reached. As this value is passed, the detector changes state,  $R_{3N}$  is shorted out, and the trip point becomes controlled by only  $R_{1N}$  and  $R_{2N}$ , a lower value. The input will then have to fall to this new point to restore the initial comparator state, but as soon as this occurs, the trip point will be raised again.

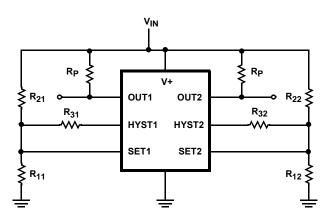

An alternative circuit for obtaining hysteresis is shown in Figure 11. In this configuration, the HYST pins put the extra resistor in parallel with the upper setting resistor. The values of the resistors differ, but the action is essentially the same. The governing equations are given in Table 1. These ignore the effects of the resistance of the HYST outputs, but these can normally be neglected if the resistor values are above about  $100k\Omega$ .

$$V_{TR2} = V_{SET2} \frac{(R_{12} + R_{22})}{R_{12}} = 1.3 \frac{(R_{12} + R_{22})}{R_{12}}$$

for detector 2

FIGURE 11. AN ALTERNATIVE HYSTERESIS CIRCUIT

#### TABLE 1. SET-POINT EQUATIONS

## Applications

### Single Supply Fault Monitor

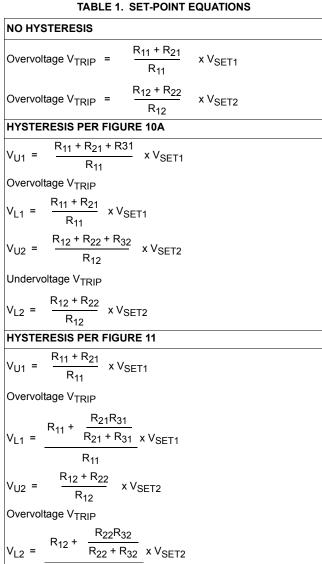

Figure 12 shows an over/under voltage fault monitor for a single supply. The overvoltage trip point is centered around 5.5V and the undervoltage trip point is centered around 4.5V. Both have some hysteresis to prevent erratic output ON and OFF conditions. The two outputs are connected in a wired OR configuration with a pullup resistor to generate a power OK signal.

FIGURE 12. FAULT MONITOR FOR A SINGLE SUPPLY

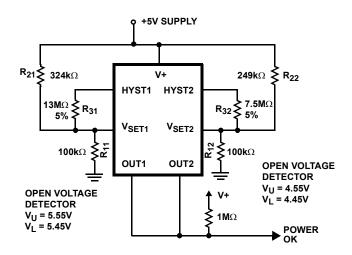

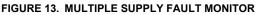

# Multiple Supply Fault Monitor

The ICL7665S can simultaneously monitor several supplies when connected as shown in Figure 13. The resistors are chosen such that the sum of the currents through R<sub>21A</sub>, R<sub>21B</sub>, and R<sub>31</sub> is equal to the current through R<sub>11</sub> when the two input voltage are at the desired low voltage detection point. The current through R11 at this point is equal to 1.3V/R<sub>11</sub>. The voltage at the  $V_{SET}$  input depends on the voltage of both supplies being monitored. The trip voltage of one supply while the other supply is at the nominal voltage will be different that the trip voltage when both supplies are below their nominal voltages.

The other side of the ICL7665S can be used to detect the absence of negative supplies. The trip points for OUT1 depend on both the negative supply voltages and the actual voltage of the +5V supply.

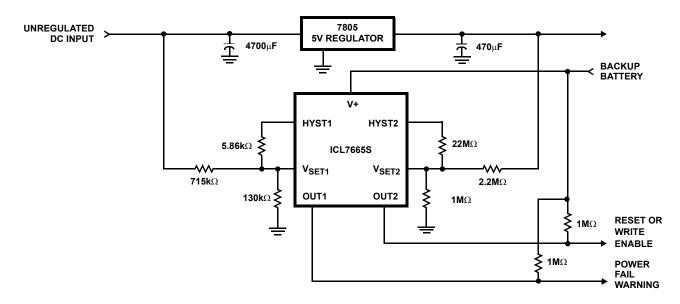

# Combination Low Battery Warning and Low Battery Disconnect

When using rechargeable batteries in a system, it is important to keep the batteries from being over discharged. The circuit shown in Figure 14 provides a low battery warning and also disconnects the low battery from the rest of the system to prevent damage to the battery. OUT1 is used to shutdown the ICL7663S when the battery voltage drops to the value where the load should be disconnected. As long as  $V_{SET1}$  is greater than 1.3V, OUT1 is low, but when  $V_{SET1}$  drops below 1.3V, OUT1 goes high shutting off the ICL7663S. OUT2 is used for low battery warning. When  $V_{SET2}$  is greater than 1.3V, OUT2 is high and the low battery warning is on. When  $V_{SET2}$  drops below 1.3V, OUT2 is low and the low battery warning goes off. The trip voltage for low battery warning can be set higher than the trip voltage for shutdown to give advance low battery warning before the battery is disconnected.

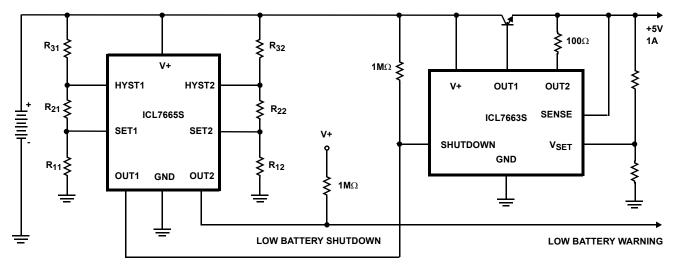

# Power Fail Warning and Powerup/Powerdown Reset

Figure 15 shows a power fail warning circuit with powerup/powerdown reset. When the unregulated DC input is above the trip point, OUT1 is low. When the DC input drops below the trip point, OUT1 shuts OFF and the power fail warning goes high. The voltage on the input of the 7805 will continue to provide 5V out at 1A until  $V_{IN}$  is less than 7.3V, this circuit will provide a certain amount of warning before the 5V output begins to drop.

The ICL7665S OUT2 is used to prevent a microprocessor from writing spurious data to a CMOS battery backup memory by causing OUT2 to go low when the 7805 5V output drops below the ICL7665S trip point.

FIGURE 14. LOW BATTERY WARNING AND LOW BATTERY DISCONNECT

FIGURE 15. POWER FAIL WARNING AND POWERUP/POWERDOWN RESET

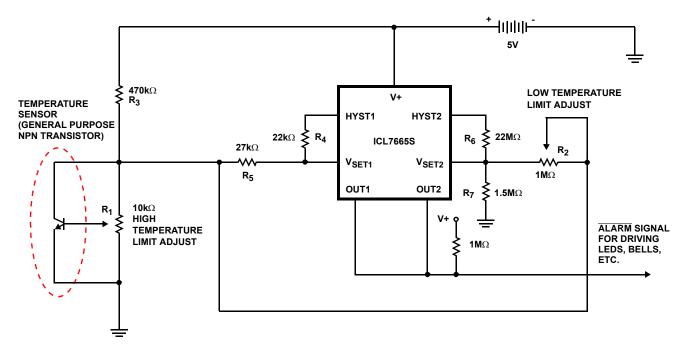

## Simple High/Low Temperature Alarm

Figure 16 illustrates a simple high/low temperature alarm which uses the ICL7665S with an NPN transistor. The voltage at the top of R<sub>1</sub> is determined by the V<sub>BE</sub> of the transistor and the position of R<sub>1</sub>'s wiper arm. This voltage has a negative temperature coefficient. R<sub>1</sub> is adjusted so that V<sub>SET2</sub> equals 1.3V when the NPN transistor's temperature reaches the temperature selected for the high temperature alarm. When this occurs, OUT2 goes low. R<sub>2</sub> is adjusted so that V<sub>SET1</sub> equals 1.3V when the NPN transistor's temperature reaches the temperature selected for the high temperature alarm. When this occurs, OUT2 goes low. R<sub>2</sub> is adjusted so that V<sub>SET1</sub> equals 1.3V when the NPN transistor's temperature reaches the temperature selected for the low temperature alarm. When the temperature drops below this limit, OUT1 goes low.

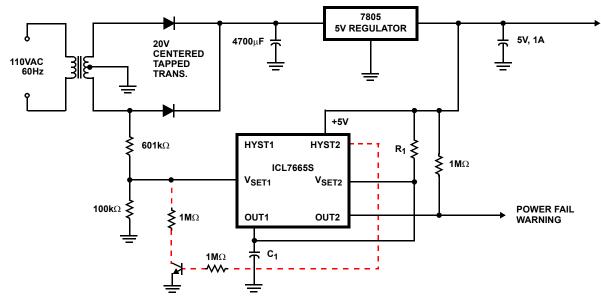

## AC Power Fail and Brownout Detector

Figure 17 shows a circuit that detects AC undervoltage by monitoring the secondary side of the transformer. The capacitor,  $C_1$ , is charged through  $R_1$  when OUT1 is OFF. With a normal 100 VAC input to the transformer, OUT1 will discharge  $C_1$  once every cycle, approximately every 16.7ms. When the AC input voltage is reduced, OUT1 will stay OFF, so that  $C_1$  does not discharge. When the voltage on  $C_1$  reaches 1.3V, OUT2 turns OFF and the power fail warning goes high. The time constant,  $R_1C_1$ , is chosen such that it takes longer than 16.7ms to charge  $C_1$  1.3V.

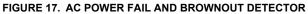

# Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

#### E8.3 (JEDEC MS-001-BA ISSUE D) 8 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | HES   | MILLIN   | IETERS |       |

|----------------|-------|-------|----------|--------|-------|

| SYMBOL         | MIN   | MAX   | MIN      | MAX    | NOTES |

| А              | -     | 0.210 | -        | 5.33   | 4     |

| A1             | 0.015 | -     | 0.39     | -      | 4     |

| A2             | 0.115 | 0.195 | 2.93     | 4.95   | -     |

| В              | 0.014 | 0.022 | 0.356    | 0.558  | -     |

| B1             | 0.045 | 0.070 | 1.15     | 1.77   | 8, 10 |

| С              | 0.008 | 0.014 | 0.204    | 0.355  | -     |

| D              | 0.355 | 0.400 | 9.01     | 10.16  | 5     |

| D1             | 0.005 | -     | 0.13     | -      | 5     |

| E              | 0.300 | 0.325 | 7.62     | 8.25   | 6     |

| E1             | 0.240 | 0.280 | 6.10     | 7.11   | 5     |

| е              | 0.100 | BSC   | 2.54     | BSC    | -     |

| e <sub>A</sub> | 0.300 | BSC   | 7.62 BSC |        | 6     |

| е <sub>В</sub> | -     | 0.430 | -        | 10.92  | 7     |

| L              | 0.115 | 0.150 | 2.93     | 3.81   | 4     |

| Ν              | 8     | 3     |          | 8      | 9     |

Rev. 0 12/93

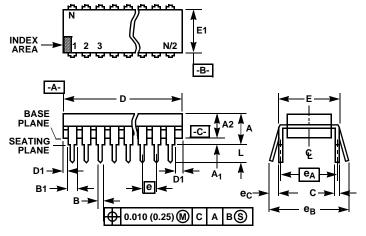

# Small Outline Plastic Packages (SOIC)

#### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

#### **M8.15** (JEDEC MS-012-AA ISSUE C) 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC    | IES    | MILLIN   | INCHES MILLIMETERS |       |

|--------|--------|--------|----------|--------------------|-------|

| SYMBOL | MIN    | MAX    | MIN      | MAX                | NOTES |

| А      | 0.0532 | 0.0688 | 1.35     | 1.75               | -     |

| A1     | 0.0040 | 0.0098 | 0.10     | 0.25               | -     |

| В      | 0.013  | 0.020  | 0.33     | 0.51               | 9     |

| С      | 0.0075 | 0.0098 | 0.19     | 0.25               | -     |

| D      | 0.1890 | 0.1968 | 4.80     | 5.00               | 3     |

| E      | 0.1497 | 0.1574 | 3.80     | 4.00               | 4     |

| е      | 0.050  | BSC    | 1.27 BSC |                    | -     |

| Н      | 0.2284 | 0.2440 | 5.80     | 6.20               | -     |

| h      | 0.0099 | 0.0196 | 0.25     | 0.50               | 5     |

| L      | 0.016  | 0.050  | 0.40     | 1.27               | 6     |

| Ν      | 8      |        | 8        |                    | 7     |

| α      | 0°     | 8°     | 0°       | 8°                 | -     |

Rev. 1 6/05

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com