Burr-Brown Products

ADS1212 ADS1213

SBAS064B – JANUARY 1996 – REVISED FEBRUARY 2004

# 22-Bit ANALOG-TO-DIGITAL CONVERTER

# FEATURES

- DELTA-SIGMA A/D CONVERTER

- 22 BITS NO MISSING CODES

- 20 BITS EFFECTIVE RESOLUTION AT 10Hz AND 16 BITS AT 1000Hz

- LOW POWER: 1.4mW

- DIFFERENTIAL INPUTS

- PROGRAMMABLE GAIN AMPLIFIER

- SPI<sup>™</sup> COMPATIBLE SSI INTERFACE

- PROGRAMMABLE CUTOFF FREQUENCY UP TO 6.25kHz

- INTERNAL/EXTERNAL REFERENCE

- ON-CHIP SELF-CALIBRATION

- ADS1213 INCLUDES 4-CHANNEL MUX

# **APPLICATIONS**

- INDUSTRIAL PROCESS CONTROL

- INSTRUMENTATION

- BLOOD ANALYSIS

- SMART TRANSMITTERS

- PORTABLE INSTRUMENTS

- WEIGH SCALES

- PRESSURE TRANSDUCERS

# DESCRIPTION

The ADS1212 and ADS1213 are precision, wide dynamic range, delta-sigma Analog-to-Digital (A/D) converters with 24-bit resolution operating from a single +5V supply. The differential inputs are ideal for direct connection to transducers or low-level voltage signals. The delta-sigma architecture is used for wide dynamic range and to ensure 22 bits of no-missing-code performance. An effective resolution of 20 bits is achieved through the use of a very low-noise input amplifier at conversion rates up to 10Hz. Effective resolutions of 16 bits can be maintained up to a sample rate of 1kHz through the use of the unique Turbo Modulator mode of operation. The dynamic range of the converters is further increased by providing a low-noise programmable gain amplifier with a gain range of 1 to 16 in binary steps.

The ADS1212 and ADS1213 are designed for high-resolution measurement applications in smart transmitters, industrial process control, weigh scales, chromatography and portable instrumentation. Both converters include a flexible synchronous serial interface that is SPI compatible and also offers a two-wire control mode for low-cost isolation.

The ADS1212 is a single channel converter and is offered in both DIP-18 and SO-18 packages. The ADS1213 includes a 4-channel input multiplexer and is available in DIP-24, SO-24, and SSOP-28 packages.

PATENTS PENDING

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

# SPECIFICATIONS

All specifications  $T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = DV_{DD} = +5V$ ,  $f_{XIN} = 1MHz$ , programmable gain amplifier setting of 1, Turbo Mode Rate of 1, REF<sub>OUT</sub> disabled,  $V_{BIAS}$  disabled, and external 2.5V reference, unless otherwise specified.

|                                                     |                                                                  | ADS                              | 1212U, P/ADS1213            | J, P, E                          |        |  |

|-----------------------------------------------------|------------------------------------------------------------------|----------------------------------|-----------------------------|----------------------------------|--------|--|

| PARAMETER                                           | CONDITIONS                                                       | MIN                              | ТҮР                         | MAX                              | UNITS  |  |

| ANALOG INPUT                                        |                                                                  |                                  |                             |                                  |        |  |

| Input Voltage Range <sup>(1)</sup>                  |                                                                  | 0                                |                             | +5                               | V      |  |

|                                                     | With V <sub>BIAS</sub> <sup>(2)</sup>                            | -10                              |                             | +10                              | V      |  |

| Input Impedance                                     | G = Gain, TMR = Turbo Mode Rate                                  |                                  | 20/(G • TMR) <sup>(3)</sup> |                                  | MΩ     |  |

| Programmable Gain Amplifier                         | User Programmable: 1, 2, 4, 8, or 16                             | 1                                |                             | 16                               |        |  |

| Input Capacitance                                   |                                                                  |                                  | 5                           |                                  | pF     |  |

| Input Leakage Current                               | At +25°C                                                         |                                  | 5                           | 50                               | pA     |  |

|                                                     | T <sub>MIN</sub> to T <sub>MAX</sub>                             |                                  |                             | 1                                | nA     |  |

| SYSTEMS PERFORMANCE                                 |                                                                  |                                  |                             |                                  |        |  |

| No Missing Codes                                    | $f_{DATA} = 10Hz$                                                | 22                               |                             |                                  | Bits   |  |

|                                                     | $f_{DATA} = 60Hz$                                                | 19                               |                             |                                  | Bits   |  |

|                                                     | $f_{DATA} = 100Hz$ , TMR of 4                                    | 21                               |                             |                                  | Bits   |  |

|                                                     | $f_{DATA} = 250Hz$ , TMR of 8                                    | 20                               |                             |                                  | Bits   |  |

|                                                     | $f_{DATA} = 500Hz$ , TMR of 16                                   | 20                               |                             |                                  | Bits   |  |

|                                                     | $f_{DATA} = 1000$ Hz, TMR of 16                                  | 18                               |                             |                                  | Bits   |  |

| Integral Linearity                                  | $f_{DATA} = 60Hz$                                                | -                                |                             | ±0.0015                          | %FSR   |  |

| <b>U C C C C C C C C C C</b>                        | $f_{DATA} = 1000$ Hz, TMR of 16                                  |                                  |                             | ±0.0015                          | %FSR   |  |

| Integral Linearity (Single-Ended)                   | DATA                                                             |                                  | 0.01                        |                                  | %FSR   |  |

| Unipolar Offset Error <sup>(4)</sup>                |                                                                  |                                  | See Note 5                  |                                  |        |  |

| Unipolar Offset Drift <sup>(6)</sup>                |                                                                  |                                  | 1                           |                                  | ppm/°C |  |

| Gain Error <sup>(4)</sup>                           |                                                                  |                                  | See Note 5                  |                                  |        |  |

| Gain Error Drift <sup>(6)</sup>                     |                                                                  |                                  | 4                           |                                  | ppm/°C |  |

| Common-Mode Rejection <sup>(9)</sup>                | At DC, T <sub>MIN</sub> to T <sub>MAX</sub>                      | 90                               | 100                         |                                  | dB     |  |

| common-mode rejections                              | 50Hz, $f_{DATA} = 50Hz^{(7)}$                                    | 160                              | 100                         |                                  | dB     |  |

|                                                     | $60Hz$ , $f_{DATA} = 60Hz^{(7)}$                                 | 160                              |                             |                                  | dB     |  |

| Normal-Mode Rejection                               | $50Hz$ , $f_{DATA} = 50Hz^{(7)}$                                 | 100                              |                             |                                  | dB     |  |

| Normal-Mode Rejection                               | $60Hz$ , $f_{DATA} = 50Hz^{(7)}$                                 | 100                              |                             |                                  | dB     |  |

| Output Noise                                        | $OOTZ, T_{DATA} = OOTZ^{(1)}$                                    |                                  | ypical Performance          | <br>Curves                       | uв     |  |

| Power Supply Rejection                              | DC, 50Hz, and 60Hz                                               | 60                               |                             |                                  | dB     |  |

| VOLTAGE REFERENCE                                   |                                                                  |                                  |                             |                                  |        |  |

| Internal Reference (REF <sub>OUT</sub> )            |                                                                  | 2.4                              | 2.5                         | 2.6                              | v      |  |

| Drift                                               |                                                                  |                                  | 25                          | 2.0                              | ppm/°C |  |

| Noise                                               |                                                                  |                                  | 50                          |                                  | μVp-p  |  |

| Load Current                                        | Source or Sink                                                   |                                  |                             | 1                                | mA     |  |

| Output Impedance                                    |                                                                  |                                  | 2                           |                                  | Ω      |  |

| External Reference (REF <sub>IN</sub> )             |                                                                  | 2.0                              | _                           | 3.0                              | v      |  |

| Load Current                                        |                                                                  |                                  |                             | 2.5                              | μÂ     |  |

| V <sub>BIAS</sub> Output                            | Using Internal Reference                                         | 3.15                             | 3.3                         | 3.45                             | V      |  |

| Drift                                               |                                                                  | 0110                             | 50                          | 0.10                             | ppm/°C |  |

| Load Current                                        | Source or Sink                                                   |                                  |                             | 10mA                             | PP     |  |

| DIGITAL INPUT/OUTPUT                                |                                                                  |                                  |                             |                                  |        |  |

| Logic Family                                        |                                                                  | Т                                | TL Compatible CMC           | DS                               |        |  |

| Logic Level: (all except X <sub>IN</sub> )          |                                                                  |                                  |                             |                                  |        |  |

| V <sub>IH</sub>                                     | I <sub>IH</sub> = +5μA                                           | 2.0                              |                             | DV <sub>DD</sub> +0.3            | V      |  |

| V <sub>IL</sub>                                     | $I_{IL} = +5\mu A$                                               | -0.3                             |                             | 0.8                              | V      |  |

| V <sub>OH</sub>                                     | I <sub>OH</sub> = 2 TTL Loads                                    | 2.4                              |                             |                                  | V      |  |

| V <sub>OL</sub>                                     | $I_{OL} = 2$ TTL Loads                                           |                                  |                             | 0.4                              | V      |  |

| X <sub>IN</sub> Input Levels: V <sub>IH</sub>       |                                                                  | 3.5                              |                             | DV <sub>DD</sub> +0.3            | V      |  |

| V <sub>IL</sub>                                     |                                                                  | -0.3                             |                             | 0.8                              | V      |  |

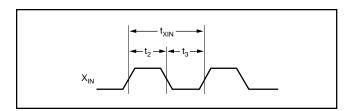

| X <sub>IN</sub> Frequency Range (f <sub>XIN</sub> ) |                                                                  | 0.5                              |                             | 2.5                              | MHz    |  |

| Output Data Rate (f <sub>DATA</sub> )               | User Programmable and TMR = 1 to 16                              | 0.96                             |                             | 6,250                            | Hz     |  |

|                                                     | $f_{XIN} = 500 \text{kHz}$                                       | 0.48                             |                             | 3,125                            | Hz     |  |

|                                                     | $f_{XIN} = 2.5 MHz$                                              | 2.4                              |                             | 15,625                           | Hz     |  |

| Data Format                                         |                                                                  |                                  |                             |                                  |        |  |

|                                                     |                                                                  | or Offset Binary                 |                             |                                  |        |  |

| SYSTEM CALIBRATION                                  |                                                                  |                                  |                             |                                  |        |  |

| Offset and Full-Scale Limits                        | V <sub>FS</sub> = Full-Scale Differential Voltage <sup>(8)</sup> | 0.7 • (2 • REF <sub>IN</sub> )/G | i                           |                                  |        |  |

| V <sub>FS</sub> –   V <sub>OS</sub>                 | V <sub>OS</sub> = Offset Differential Voltage <sup>(8)</sup>     |                                  | 1                           | 1.3 • (2 • REF <sub>IN</sub> )/G |        |  |

# **SPECIFICATIONS** (Cont.)

All specifications  $T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = DV_{DD} = +5V$ ,  $f_{XIN} = 1MHz$ , programmable gain amplifier setting of 1, Turbo Mode Rate of 1, REF<sub>OUT</sub> disabled, V<sub>BIAS</sub> disabled, and external 2.5V reference, unless otherwise specified.

|                                | CONDITIONS                           | ADS1 | 1212U, P/ADS1213 | U, P, E | UNITS |

|--------------------------------|--------------------------------------|------|------------------|---------|-------|

| PARAMETER                      |                                      | MIN  | ТҮР              | MAX     |       |

| POWER SUPPLY REQUIREMENTS      |                                      |      |                  |         |       |

| Power Supply Voltage           |                                      | 4.75 |                  | 5.25    | V     |

| Power Supply Current:          |                                      |      |                  |         |       |

| Analog Current                 |                                      |      | 95               |         | μΑ    |

| Digital Current                |                                      |      | 185              |         | μΑ    |

| Additional Analog Current with |                                      |      |                  |         |       |

| REF <sub>OUT</sub> Enabled     |                                      |      | 1.8              |         | mA    |

| V <sub>BIAS</sub> Enabled      | No Load                              |      | 1                |         | mA    |

| Power Dissipation              | At +25°C                             |      | 1.4              |         | mW    |

|                                | T <sub>MIN</sub> to T <sub>MAX</sub> |      |                  | 1.8     | mW    |

|                                | TMR of 16                            |      | 6                | 8.5     | mW    |

|                                | $f_{XIN} = 2.5MHz$                   |      | 2.2              |         | mW    |

|                                | $f_{XIN} = 2.5MHz$ , TMR of 16       |      | 7.5              |         | mW    |

|                                | Sleep Mode                           |      | 0.45             |         | mW    |

| TEMPERATURE RANGE              |                                      |      |                  |         |       |

| Specified                      |                                      | -40  |                  | +85     | °C    |

| Storage                        |                                      | -60  |                  | +125    | °C    |

NOTES: (1) In order to achieve the converter's full-scale range, the input must be fully differential  $(A_{IN}N = 2 \cdot REF_{IN} - A_{IN}P)$ . If the input is single-ended  $(A_{IN}N \text{ or } A_{IN}P)$  is fixed), then the full-scale range is one-half that of the differential range. (2) This range is set with external resistors and  $V_{BIAS}$  (as described in the text). Other ranges are possible. (3) Input impedance is higher with lower  $f_{XIN}$ . (4) Applies after calibration. (5) After system calibration, these errors will be of the order of the effective resolution of the converter. Refer to the Typical Performance Curves which apply to the desired mode of operation. (6) Recalibration can remove these errors. (7) The specification also applies at  $f_{DATA}/i$ , where i is 2, 3, 4, etc. (8) Voltages at the analog inputs must remain within AGND to  $AV_{DD}$ . (9) The common-mode rejection test is performed with 100mV differential input.

## **ABSOLUTE MAXIMUM RATINGS**

| Analog Input: Current                | -                                    |

|--------------------------------------|--------------------------------------|

|                                      | ±10mA, Continuous                    |

| Voltage                              | AGND -0.3V to AV <sub>DD</sub> +0.3V |

| AV <sub>DD</sub> to DV <sub>DD</sub> | –0.3V to 6V                          |

| AV <sub>DD</sub> to AGND             | –0.3V to 6V                          |

| DV <sub>DD</sub> to DGND             | –0.3V to 6V                          |

| AGND to DGND                         | ±0.3V                                |

| REF <sub>IN</sub> Voltage to AGND    | 0.3V to AV <sub>DD</sub> +0.3V       |

| Digital Input Voltage to DGND        | 0.3V to DV <sub>DD</sub> +0.3V       |

| Digital Output Voltage to DGND       | 0.3V to DV <sub>DD</sub> +0.3V       |

| Lead Temperature (soldering, 10s)    | +300°C                               |

| Power Dissipation (Any package)      | 500mW                                |

# PACKAGE/ORDERING INFORMATION

For the latest package and ordering information, see the Package Option Addendum located at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

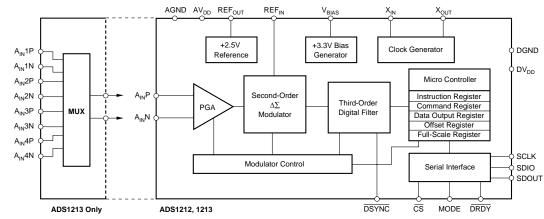

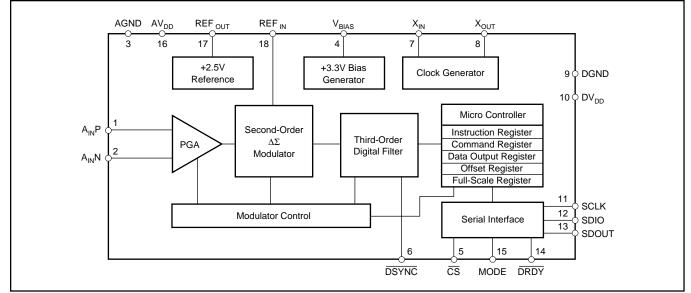

# ADS1212 SIMPLIFIED BLOCK DIAGRAM

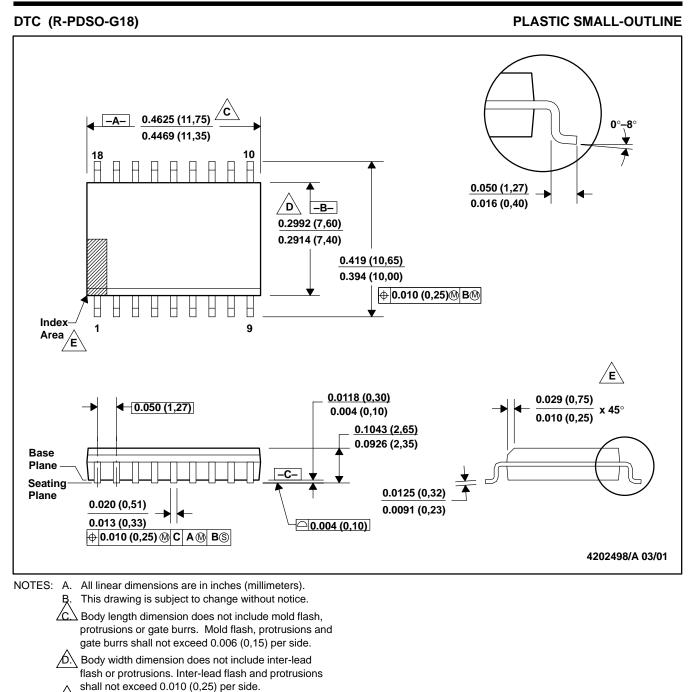

#### **ADS1212 PIN CONFIGURATION**

#### **ADS1212 PIN DEFINITIONS**

| PIN NO | NAME               | DESCRIPTION                                                     |

|--------|--------------------|-----------------------------------------------------------------|

| 1      | A <sub>IN</sub> P  | Noninverting Input.                                             |

| 2      | A <sub>IN</sub> N  | Inverting Input.                                                |

| 3      | AGND               | Analog Ground.                                                  |

| 4      | V <sub>BIAS</sub>  | Bias Voltage Output, +3.3V nominal.                             |

| 5      | CS                 | Chip Select Input.                                              |

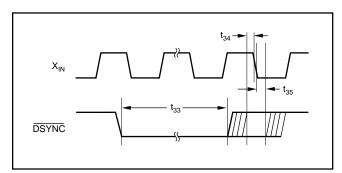

| 6      | DSYNC              | Control Input to Synchronize Serial Output Data.                |

| 7      | X <sub>IN</sub>    | System Clock Input.                                             |

| 8      | X <sub>OUT</sub>   | System Clock Output.                                            |

| 9      | DGND               | Digital Ground.                                                 |

| 10     | $DV_{DD}$          | Digital Supply, +5V nominal.                                    |

| 11     | SCLK               | Clock Input/Output for serial data transfer.                    |

| 12     | SDIO               | Serial Data Input (can also function as Serial Data<br>Output). |

| 13     | SDOUT              | Serial Data Output.                                             |

| 14     | DRDY               | Data Ready.                                                     |

| 15     | MODE               | SCLK Control Input (Master = 1, Slave = 0).                     |

| 16     | AV <sub>DD</sub>   | Analog Supply, +5V nominal.                                     |

| 17     | REF <sub>OUT</sub> | Reference Output, +2.5V nominal.                                |

| 18     | $REF_IN$           | Reference Input.                                                |

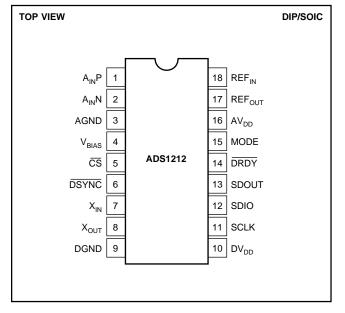

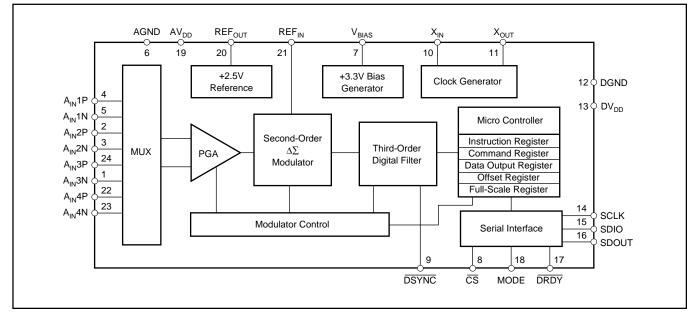

## ADS1213 SIMPLIFIED BLOCK DIAGRAM

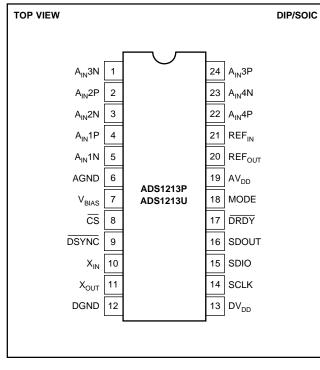

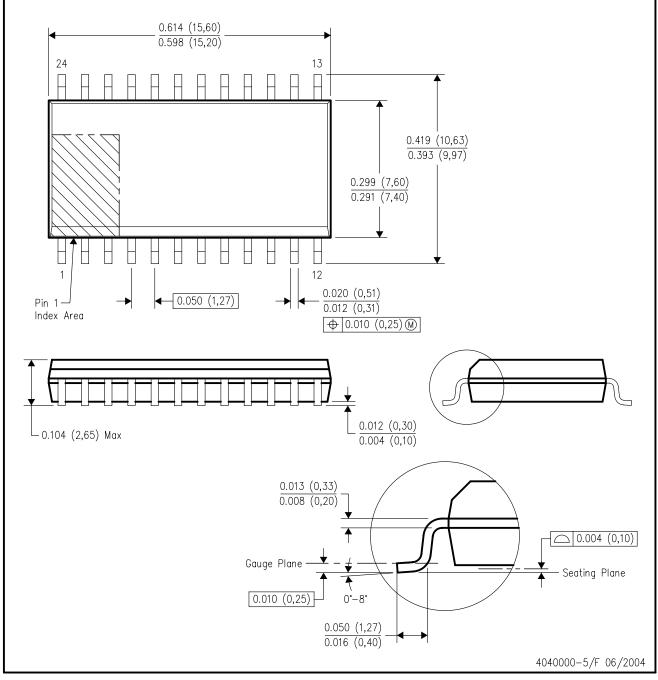

## ADS1213P AND ADS1213U PIN CONFIGURATION

# ADS1213P AND ADS1213U PIN DEFINITIONS

| PIN NO | NAME               | DESCRIPTION                                         |

|--------|--------------------|-----------------------------------------------------|

| 1      | A <sub>IN</sub> 3N | Inverting Input Channel 3.                          |

| 2      | A <sub>IN</sub> 2P | Noninverting Input Channel 2.                       |

| 3      | A <sub>IN</sub> 2N | Inverting Input Channel 2.                          |

| 4      | A <sub>IN</sub> 1P | Noninverting Input Channel 1.                       |

| 5      | A <sub>IN</sub> 1N | Inverting Input Channel 1.                          |

| 6      | AGND               | Analog Ground.                                      |

| 7      | V <sub>BIAS</sub>  | Bias Voltage Output, +3.3V nominal.                 |

| 8      | CS                 | Chip Select Input.                                  |

| 9      | DSYNC              | Control Input to Synchronize Serial Output Data.    |

| 10     | X <sub>IN</sub>    | System Clock Input.                                 |

| 11     | X <sub>OUT</sub>   | System Clock Output.                                |

| 12     | DGND               | Digital Ground.                                     |

| 13     | DV <sub>DD</sub>   | Digital Supply, +5V nominal.                        |

| 14     | SCLK               | Clock Input/Output for serial data transfer.        |

| 15     | SDIO               | Serial Data Input (can also function as Serial Data |

|        |                    | Output).                                            |

| 16     | SDOUT              | Serial Data Output.                                 |

| 17     | DRDY               | Data Ready.                                         |

| 18     | MODE               | SCLK Control Input (Master = 1, Slave = 0).         |

| 19     | AV <sub>DD</sub>   | Analog Supply, +5V nominal.                         |

| 20     | REFOUT             | Reference Output: +2.5V nominal.                    |

| 21     | REFIN              | Reference Input.                                    |

| 22     | A <sub>IN</sub> 4P | Noninverting Input Channel 4.                       |

| 23     | A <sub>IN</sub> 4N | Inverting Input Channel 4.                          |

| 24     | A <sub>IN</sub> 3P | Noninverting Input Channel 3.                       |

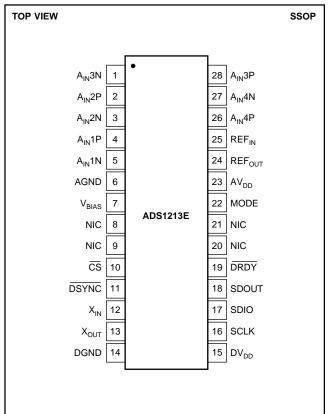

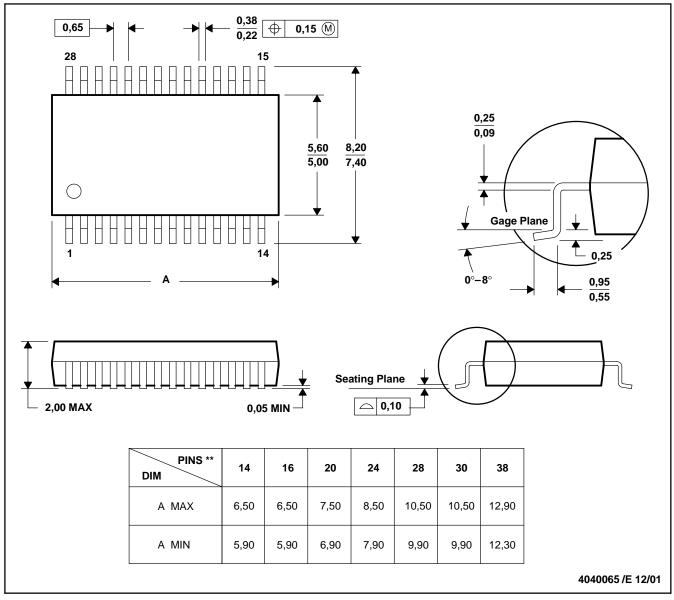

# ADS1213E PIN CONFIGURATION

#### ADS1213E PIN DEFINITIONS

| PIN NO | NAME               | DESCRIPTION                                         |

|--------|--------------------|-----------------------------------------------------|

| 1      | A <sub>IN</sub> 3N | Inverting Input Channel 3.                          |

| 2      | A <sub>IN</sub> 2P | Noninverting Input Channel 2.                       |

| 3      | A <sub>IN</sub> 2N | Inverting Input Channel 2.                          |

| 4      | A <sub>IN</sub> 1P | Noninverting Input Channel 1.                       |

| 5      | A <sub>IN</sub> 1N | Inverting Input Channel 1.                          |

| 6      | AGND               | Analog Ground.                                      |

| 7      | V <sub>BIAS</sub>  | Bias Voltage Output, +3.3V nominal.                 |

| 8      | NIC                | Not Internally Connected.                           |

| 9      | NIC                | Not Internally Connected.                           |

| 10     | CS                 | Chip Select Input.                                  |

| 11     | DSYNC              | Control Input to Synchronize Serial Output Data.    |

| 12     | X <sub>IN</sub>    | System Clock Input.                                 |

| 13     | X <sub>OUT</sub>   | System Clock Output.                                |

| 14     | DGND               | Digital Ground.                                     |

| 15     | DV <sub>DD</sub>   | Digital Supply, +5V nominal.                        |

| 16     | SCLK               | Clock Input/Output for serial data transfer.        |

| 17     | SDIO               | Serial Data Input (can also function as Serial Data |

|        |                    | Output).                                            |

| 18     | SDOUT              | Serial Data Output.                                 |

| 19     | DRDY               | Data Ready.                                         |

| 20     | NIC                | Not Internally Connected.                           |

| 21     | NIC                | Not Internally Connected.                           |

| 22     | MODE               | SCLK Control Input (Master = 1, Slave = 0).         |

| 23     | AV <sub>DD</sub>   | Analog Supply, +5V nominal.                         |

| 24     | REFOUT             | Reference Output: +2.5V nominal.                    |

| 25     | REFIN              | Reference Input.                                    |

| 26     | A <sub>IN</sub> 4P | Noninverting Input Channel 4.                       |

| 27     | A <sub>IN</sub> 4N | Inverting Input Channel 4.                          |

| 28     | A <sub>IN</sub> 3P | Noninverting Input Channel 3.                       |

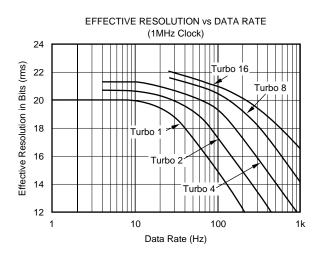

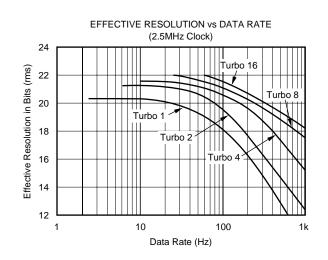

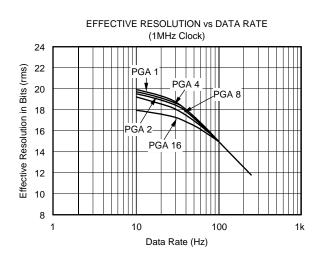

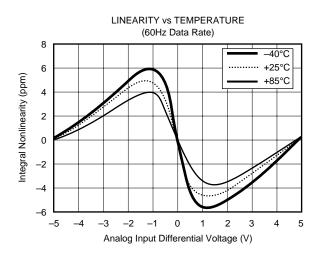

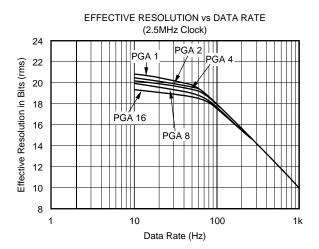

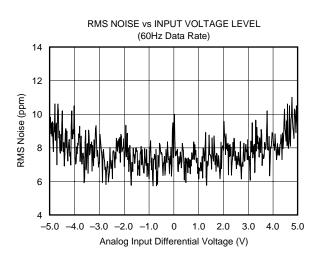

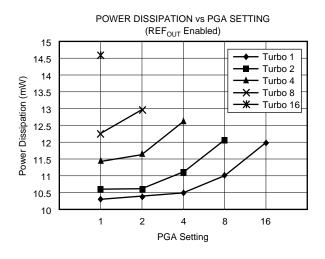

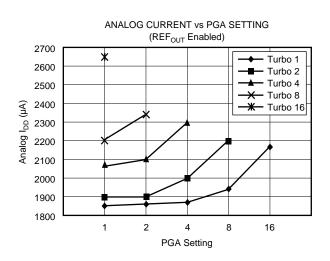

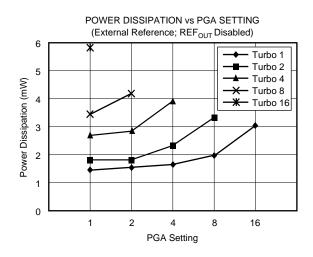

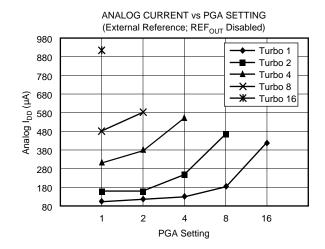

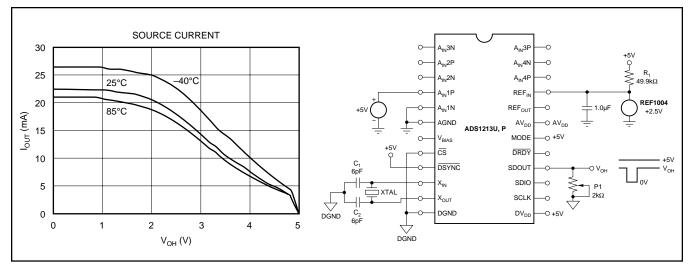

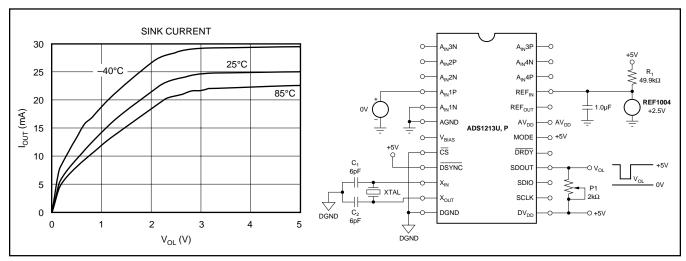

# **TYPICAL PERFORMANCE CURVES**

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = +5V$ ,  $f_{XIN} = 1MHz$ , programmable gain amplifier setting of 1, Turbo Mode Rate of 1, REF<sub>OUT</sub> disabled, V<sub>BIAS</sub> disabled, and external 2.5V reference, unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (Cont.)**

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = +5V$ ,  $f_{XIN} = 1$ MHz, programmable gain amplifier setting of 1, Turbo Mode Rate of 1, REF<sub>OUT</sub> disabled, V<sub>BIAS</sub> disabled, and external 2.5V reference, unless otherwise noted.

# THEORY OF OPERATION

The ADS1212 and ADS1213 are precision, high dynamic range, self-calibrating, 24-bit, delta-sigma A/D converters capable of achieving very high resolution digital results. Each contains a programmable gain amplifier (PGA); a second-order delta-sigma modulator; a programmable digital filter; a microcontroller including the Instruction, Command and Calibration registers; a serial interface; a clock generator circuit; and an internal 2.5V reference. The ADS1213 includes a 4-channel input multiplexer.

In order to provide low system noise, common-mode rejection of 100dB and excellent power supply rejection, the design topology is based on a fully differential switched capacitor architecture. Turbo Mode, a unique feature of the ADS1212/13, can be used to boost the sampling rate of the input capacitor, which is normally 7.8kHz with a 1MHz clock. By programming the Command Register, the sampling rate can be increased to 15.6kHz, 31.2kHz, 62.5kHz, or 125kHz. Each increase in sample rate results in an increase in performance when maintaining the same output data rate.

The programmable gain amplifier (PGA) of the ADS1212/ 13 can be set to a gain of 1, 2, 4, 8 or 16—substantially increasing the dynamic range of the converter and simplifying the interface to the more common transducers (see Table I). This gain is implemented by increasing the number of samples taken by the input capacitor from 7.8kHz for a gain of 1 to 125kHz for a gain of 16. Since the Turbo Mode and PGA functions are both implemented by varying the sampling frequency of the input capacitor, the combination of PGA gain and Turbo Mode Rate is limited to 16 (see Table II). For example, when using a Turbo Mode Rate of 8 (62.5kHz at 1MHz), the maximum PGA gain setting is 2.

|                 |                                             | LOG<br>UT <sup>(1)</sup> | ANALOG INPUT<br>UTILIZING V <sub>BIAS</sub> <sup>(1,2)</sup> |                                                   |  |

|-----------------|---------------------------------------------|--------------------------|--------------------------------------------------------------|---------------------------------------------------|--|

| GAIN<br>SETTING | FULL-EXAMPLESCALEVOLTAGERANGERANGE(3)(V)(V) |                          | FULL-<br>SCALE<br>RANGE<br>(V)                               | EXAMPLE<br>VOLTAGE<br>RANGE <sup>(3)</sup><br>(V) |  |

| 1               | 10                                          | 0 to 5                   | 40                                                           | ±10                                               |  |

| 2               | 5                                           | 1.25 to 3.75             | 20                                                           | ±5                                                |  |

| 4               | 2.5                                         | 1.88 to 3.13             | 10                                                           | ±2.5                                              |  |

| 8               | 1.25                                        | 2.19 to 2.81             | 5                                                            | ±1.25                                             |  |

| 16              | 0.625                                       | 2.34 to 2.66             | 2.5                                                          | ±0.625                                            |  |

| NOTE: (1) V     | Vith a 2.5V ref                             | erence, such as t        | he internal refe                                             | erence. (2) This                                  |  |

NOTE: (1) With a 2.5V reference, such as the internal reference. (2) This example utilizes the circuit in Figure 12. Other input ranges are possible. (3) The ADS1212/13 allows common-mode voltage as long as the absolute input voltage on  $A_{IN}P$  or  $A_{IN}N$  does not go below AGND or above  $AV_{DD}$ .

TABLE I. Full-Scale Range vs PGA Setting.

| TURBO MODE RATE | AVAILABLE PGA SETTINGS |

|-----------------|------------------------|

| 1               | 1, 2, 4, 8, 16         |

| 2               | 1, 2, 4, 8             |

| 4               | 1, 2, 4                |

| 8               | 1, 2                   |

| 16              | 1                      |

TABLE II. Available PGA Settings vs Turbo Mode Rate.

The output data rate of the ADS1212/13 can be varied from less than 1Hz to as much as 6.25kHz, trading off lower resolution results for higher data rates. In addition, the data rate determines the first null of the digital filter and sets the -3dB point of the input bandwidth (see the Digital Filter section). Changing the data rate of the ADS1212/13 does not result in a change in the sampling rate of the input capacitor. The data rate effectively sets the number of samples which are used by the digital filter to obtain each conversion result. A lower data rate results in higher resolution, lower input bandwidth, and different notch frequencies than a higher data rate. It does not result in any change in input impedance or modulator frequency, or any appreciable change in power consumption.

The ADS1212/13 also includes complete on-board calibration that can correct for internal offset and gain errors or limited external system errors. Internal calibration can be run when needed, or automatically and continuously in the background. System calibration can be run as needed and the appropriate input voltages must be provided to the ADS1212/ 13. For this reason, there is no continuous system calibration mode. The calibration registers are fully readable and writable. This feature allows for switching between various configurations—different data rates, Turbo Mode Rates, and gain settings—without re-calibrating.

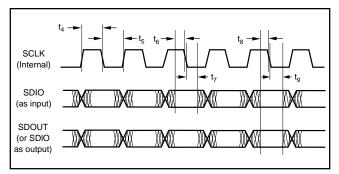

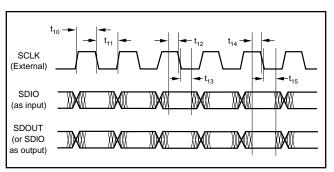

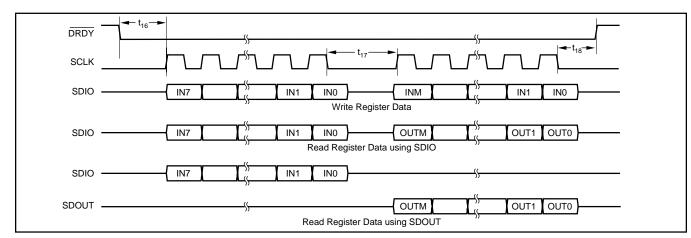

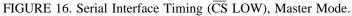

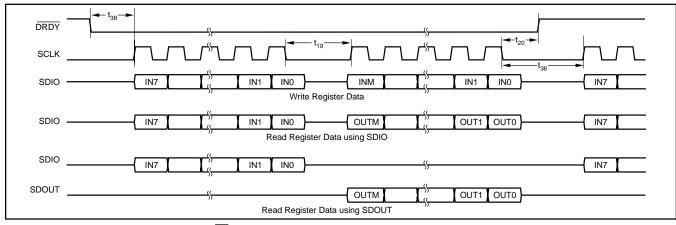

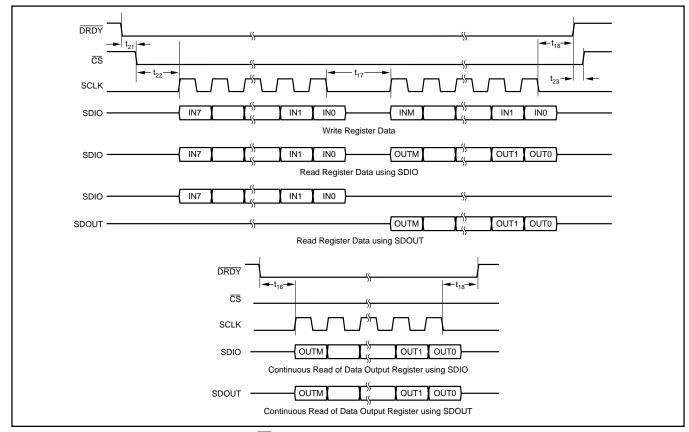

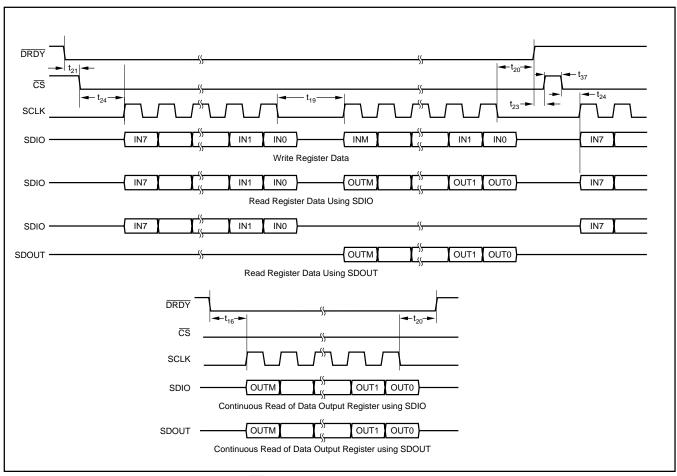

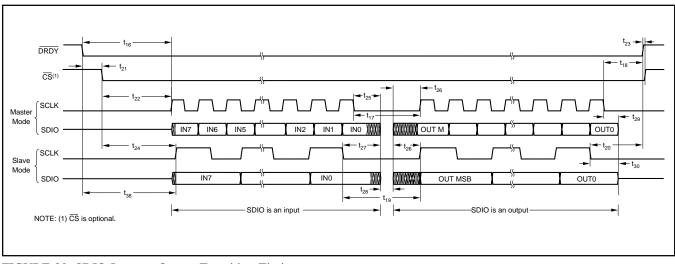

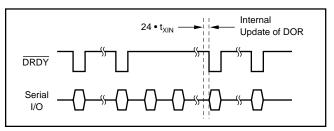

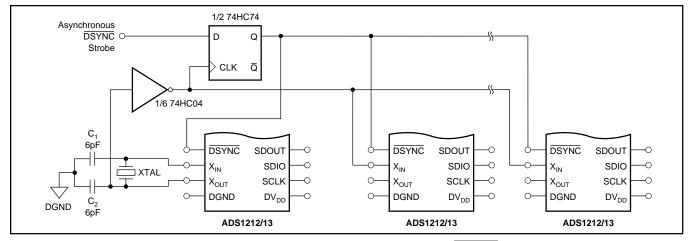

The various settings, rates, modes, and registers of the ADS1212/13 are read or written via a synchronous serial interface. This interface can operate in either a self-clocked mode (Master Mode) or an externally clocked mode (Slave Mode). In the Master Mode, the serial clock (SCLK) frequency is one-quarter of the ADS1212/13  $X_{IN}$  clock frequency.

The high resolution and flexibility of the ADS1212/13 allow these converters to fill a wide variety of A/D conversion tasks. In order to ensure that a particular configuration will meet the design goals, there are several important items which must be considered. These include (but are certainly not limited to) the needed resolution, required linearity, desired input bandwidth, power consumption goal, and sensor output voltage.

The remainder of this data sheet discusses the operation of the ADS1212/13 in detail. In order to allow for easier comparison of different configurations, "effective resolution" is used as the figure of merit for most tables and graphs. For example, Table III shows a comparison between data rate (and –3dB input bandwidth) versus PGA setting at a Turbo Mode Rate of 1 and a clock rate of 1MHz. See the Definition of Terms section for a definition of effective resolution.

| DATA<br>RATE | -3DB<br>FREQUENCY | EFFECTIVE RESOLUTION (BITS RMS) |        |    |    |    |  |

|--------------|-------------------|---------------------------------|--------|----|----|----|--|

| (HZ)         | (HZ)              | G = 1                           | G = 16 |    |    |    |  |

| 10           | 2.62              | 20                              | 20     | 20 | 19 | 18 |  |

| 25           | 6.55              | 19                              | 19     | 19 | 18 | 18 |  |

| 30           | 7.86              | 19                              | 19     | 18 | 18 | 17 |  |

| 50           | 13.1              | 17                              | 17     | 17 | 17 | 16 |  |

| 60           | 15.7              | 17                              | 17     | 17 | 16 | 16 |  |

| 100          | 26.2              | 15                              | 15     | 15 | 15 | 15 |  |

| 250          | 65.5              | 12                              | 12     | 12 | 12 | 12 |  |

TABLE III. Effective Resolution vs Data Rate and Gain Setting. (Turbo Mode Rate of 1 and a 1MHz clock.)

#### **DEFINITION OF TERMS**

An attempt has been made to be consistent with the terminology used in this data sheet. In that regard, the definition of each term is given as follows:

**Analog Input Differential Voltage**—For an analog signal that is fully differential, the voltage range can be compared to that of an instrumentation amplifier. For example, if both analog inputs of the ADS1212 are at 2.5V, then the differential voltage is 0V. If one is at 0V and the other at 5V, then the differential voltage magnitude is 5V. But, this is the case regardless of which input is at 0V and which is at 5V, while the digital output result is quite different.

The analog input differential voltage is given by the following equation:  $A_{IN}P - A_{IN}N$ . Thus, a positive digital output is produced whenever the analog input differential voltage is positive, while a negative digital output is produced whenever the differential is negative.

For example, when the converter is configured with a 2.5V reference and placed in a gain setting of 2, the positive full-scale output is produced when the analog input differential is 2.5V. The negative full-scale output is produced when the differential is -2.5V. In each case, the actual input voltages must remain within the AGND to AV<sub>DD</sub> range (see Table I).

Actual Analog Input Voltage—The voltage at any one analog input relative to AGND.

**Full-Scale Range (FSR)**—As with most A/D converters, the full-scale range of the ADS1212/13 is defined as the "input" which produces the positive full-scale digital output minus the "input" which produces the negative full-scale digital output.

For example, when the converter is configured with a 2.5V reference and is placed in a gain setting of 2, the full-scale range is: [2.5V (positive full scale) minus -2.5V (negative full scale)] = 5V.

**Typical Analog Input Voltage Range**—This term describes the actual voltage range of the analog inputs which will cover the converter's full-scale range, assuming that each input has a common-mode voltage that is greater than  $\text{REF}_{\text{IN}}/\text{PGA}$  and smaller than  $(\text{AV}_{\text{DD}} - \text{REF}_{\text{IN}}/\text{PGA})$ .

For example, when the converter is configured with a 2.5V reference and placed in a gain setting of 2, the typical input voltage range is 1.25V to 3.75V (common-mode voltage = 2.5V). However, an input range of 0V to 2.5V (common-mode voltage = 1.25V) or 2.5V to 5V (common-mode voltage = 3.75V) would also cover the converter's full-scale range.

**Voltage Span**—This is simply the magnitude of the typical analog input voltage range. For example, when the converter is configured with a 2.5V reference and placed in a gain setting of 2, the input voltage span is 2.5V.

Least Significant Bit (LSB) Weight—This is the theoretical amount of voltage that the differential voltage at the analog input would have to change in order to observe a change in the output data of one least significant bit. It is computed as follows:

LSB Weight =

$$\frac{\text{Full-Scale Range}}{2^{N}}$$

where N is the number of bits in the digital output.

**Effective Resolution**—The effective resolution of the ADS1212/13 in a particular configuration can be expressed in two different units: bits rms (referenced to output) and microvolts rms (referenced to input). Computed directly from the converter's output data, each is a statistical calculation based on a given number of results. Knowing one, the other can be computed as follows:

ER in bits rms =

$$\frac{20 \bullet \log \left(\frac{\left(\frac{10 \text{ V}}{\text{PGA}}\right)}{\text{ER in Vrms}}\right) - 1.76}{6.02}$$

ER in Vrms =

$$\frac{\left(\frac{10V}{PGA}\right)}{\left(\frac{6.02 \bullet ER \text{ in bits rms} + 1.76}{20}\right)}$$

The 10V figure in each calculation represents the full-scale range of the ADS1212/13 in a gain setting of 1. This means that both units are absolute expressions of resolution—the performance in different configurations can be directly compared regardless of the units. Comparing the resolution of different gain settings expressed in bits rms requires accounting for the PGA setting.

**Main Controller**—A generic term for the external microcontroller, microprocessor, or digital signal processor which is controlling the operation of the ADS1212/13 and receiving the output data.

$\mathbf{f}_{\mathbf{XIN}}$ —The frequency of the crystal oscillator or CMOS compatible input signal at the  $X_{IN}$  input of the ADS1212/13.

$f_{MOD}$ —The frequency or speed at which the modulator of the ADS1212/13 is running, given by the following equation:

$$f_{MOD} = \frac{f_{XIN} \bullet Turbo Mode}{128}$$

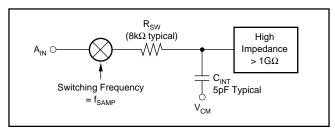

$f_{SAMP}$ —The frequency or switching speed of the input sampling capacitor. The value is given by the following equation:

$$f_{SAMP} = \frac{f_{XIN} \bullet Turbo Mode \bullet Gain Setting}{128}$$

$\mathbf{f}_{DATA}$ ,  $\mathbf{t}_{DATA}$ —The frequency of the digital output data produced by the ADS1212/13 or the inverse of this (the period), respectively,  $\mathbf{f}_{DATA}$  is also referred to as the data rate.

$$f_{DATA} = \frac{f_{XIN} \bullet Turbo Mode}{128 \bullet (Decimation Ratio + 1)} , \quad t_{DATA} = \frac{1}{f_{DATA}}$$

**Conversion Cycle**—The term "conversion cycle" usually refers to a discrete A/D conversion operation, such as that performed by a successive approximation converter. As used here, a conversion cycle refers to the  $t_{DATA}$  time period. However, each digital output is actually based on the modulator results from the last three  $t_{DATA}$  time periods.

#### **DIGITAL FILTER**

The digital filter of the ADS1212/13 computes the output result based on the most recent results from the delta-sigma modulator. The number of modulator results that are used depend on the decimation ratio set in the Command Register. At the most basic level, the digital filter can be thought of as simply averaging the modulator results and presenting this average as the digital output.

While the decimation ratio determines the number of modulator results to use, the modulator runs faster at higher Turbo Modes. These two items, together with the ADS1212/13 clock frequency, determine the output data rate:

$$f_{DATA} = \frac{f_{XIN} \bullet \text{Turbo Mode}}{128 \bullet (\text{Decimation Ratio} + 1)}$$

Also, since the conversion result is essentially an average, the data rate determines where the resulting notches are in the digital filter. For example, if the output data rate is 1kHz, then a 1kHz input frequency will average to zero during the 1ms conversion cycle. Likewise, a 2kHz input frequency will average to zero, etc.

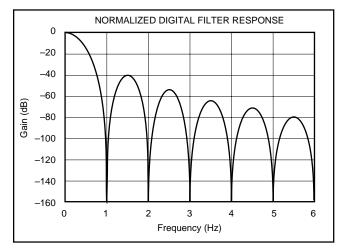

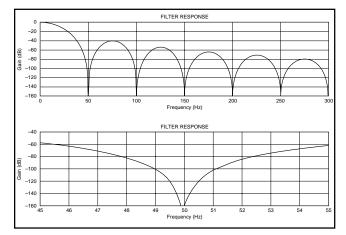

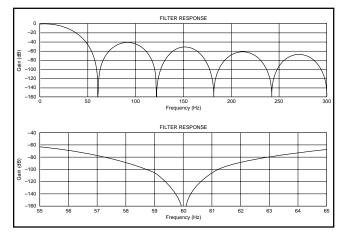

In this manner, the data rate can be used to set specific notch frequencies in the digital filter response (see Figure 1 for the normalized response of the digital filter). For example, if the rejection of power line frequencies is desired, then the data rate can simply be set to the power line frequency. Figures 2 and 3 show the digital filter response for a data rate of 50Hz and 60Hz, respectively.

FIGURE 1. Normalized Digital Filter Response.

FIGURE 2. Digital Filter Response at a Data Rate of 50Hz.

FIGURE 3. Digital Filter Response at a Data Rate of 60Hz.

If the effective resolution at a 50Hz or 60Hz data rate is not adequate for the particular application, then power line frequencies could still be rejected by operating the ADS1212/13 at 25/30Hz, 16.7/20Hz, 12.5/15Hz, etc. If a higher data rate is needed, then power line frequencies must either be rejected before conversion (with an analog notch filter) or after conversion (with a digital notch filter running on the main controller).

ADS1212, 1213 SBAS064A

#### **Filter Equation**

The digital filter is described by the following transfer function:

$$|H(f)| = \frac{\sin\left(\frac{\pi \bullet f \bullet N}{f_{MOD}}\right)}{N \bullet \sin\left(\frac{\pi \bullet f}{f_{MOD}}\right)}$$

where N is the Decimation Ratio.

This filter has a  $(\sin(x)/x)^3$  response and is referred to a  $\sin^3$  filter. For the ADS1212/13, this type of filter allows the data rate to be changed over a very wide range (nearly four orders of magnitude). However, the -3dB point of the filter is 0.262 times the data rate. And, as can be seen in Figures 1 and 2, the rejection in the stopband (frequencies higher than the first notch frequency) may only be -40dB.

These factors must be considered in the overall system design. For example, with a 50Hz data rate, a significant signal at 75Hz may alias back into the passband at 25Hz. The analog front end can be designed to provide the needed attenuation to prevent aliasing, or the system may simply provide this inherently. Another possibility is increasing the data rate and then post filtering with a digital filter on the main controller.

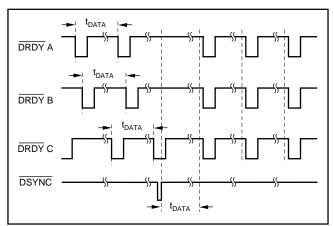

#### **Filter Settling**

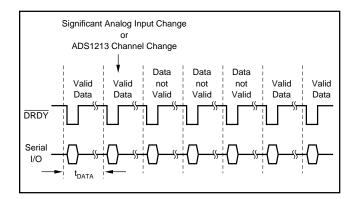

The number of modulator results used to compute each conversion result is three times the Decimation Ratio. This means that any step change (or any channel change for the ADS1213) will require at least three conversions to fully settle. However, if the change occurs asynchronously, then at least four conversions are required to ensure complete settling. For example, on the ADS1213, the fourth conversion result after a channel change will be valid (see Figure 4).

FIGURE 4. Asynchronous ADS1212/13 Analog Input Voltage Step or ADS1213 Channel Change to Fully Settled Output Data.

#### TURBO MODE

The ADS1212/13 offers a unique Turbo Mode feature which can be used to increase the modulator sampling rate by 2, 4, 8, or 16 times normal. With the increase of modulator sampling frequency, there can be a substantial increase in

the effective resolution of the output data at a given data rate, but there is also an increase in power dissipation. For Turbo Mode Rates 2 and 4, the increase is slight. For rates 8 and 16, the increase is more substantial. See the Typical Performance Curves for more information.

In a Turbo Mode Rate of 16, the ADS1212/13 can offer 16 bits of effective resolution at a 1kHz data rate. A comparison of effective resolution versus Turbo Mode Rates and output data rates is shown in Table IV while Table V shows the corresponding noise level in  $\mu$ Vrms.

|                      | EFFECTIVE RESOLUTION (BITS RMS) |                         |                         |                         |                          |  |  |

|----------------------|---------------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--|--|

| DATA<br>RATE<br>(HZ) | TURBO<br>MODE<br>RATE 1         | TURBO<br>MODE<br>RATE 2 | TURBO<br>MODE<br>RATE 4 | TURBO<br>MODE<br>RATE 8 | TURBO<br>MODE<br>RATE 16 |  |  |

| 10                   | 20                              | 21                      | 21                      |                         |                          |  |  |

| 20                   | 19                              | 20                      | 21                      | 21                      |                          |  |  |

| 40                   | 18                              | 20                      | 21                      | 21                      | 21                       |  |  |

| 50                   | 17                              | 19                      | 20                      | 21                      | 21                       |  |  |

| 60                   | 17                              | 19                      | 20                      | 21                      | 21                       |  |  |

| 100                  | 15                              | 17                      | 19                      | 21                      | 21                       |  |  |

| 250                  | 12                              | 14                      | 16                      | 19                      | 20                       |  |  |

| 1000                 |                                 |                         | 12                      | 14                      | 16                       |  |  |

| TABLE IV. Effective Resolution vs Data Rate and Turbo Mode |

|------------------------------------------------------------|

| Rate. (Gain setting of 1 and 1MHz clock.)                  |

|                      | NOISE LEVEL (µVrms)     |                         |                         |                         |                          |  |  |

|----------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--|--|

| DATA<br>RATE<br>(Hz) | TURBO<br>MODE<br>RATE 1 | TURBO<br>MODE<br>RATE 2 | TURBO<br>MODE<br>RATE 4 | TURBO<br>MODE<br>RATE 8 | TURBO<br>MODE<br>RATE 16 |  |  |

| 10                   | 7.6                     | 3.8                     | 3.8                     |                         |                          |  |  |

| 20                   | 15                      | 7.6                     | 3.8                     | 3.8                     |                          |  |  |

| 40                   | 30                      | 7.6                     | 3.8                     | 3.8                     | 3.8                      |  |  |

| 50                   | 60                      | 15                      | 7.6                     | 3.8                     | 3.8                      |  |  |

| 60                   | 60                      | 15                      | 7.6                     | 3.8                     | 3.8                      |  |  |

| 100                  | 240                     | 60                      | 15                      | 3.8                     | 3.8                      |  |  |

| 250                  | 1900                    | 480                     | 120                     | 15                      | 7.6                      |  |  |

| 1000                 |                         |                         | 1900                    | 480                     | 120                      |  |  |

TABLE V. Noise Level vs Data Rate and Turbo Mode Rate.(Gain setting of 1 and 1MHz clock.)

The Turbo Mode feature allows trade-offs to be made between the ADS1212/13  $X_{IN}$  clock frequency, power dissipation, and effective resolution. If a 0.5MHz clock is available but a 1MHz clock is needed to achieve the desired performance, a Turbo Mode Rate of 2X will result in the same effective resolution. Table VI provides a comparison of effective resolution at various clock frequencies, data rates, and Turbo Mode Rates.

| DATA<br>RATE<br>(Hz) | X <sub>IN</sub> CLOCK<br>FREQUENCY<br>(MHz) | TURBO<br>MODE<br>RATE | EFFECTIVE<br>RESOLUTION<br>(Bits rms) |

|----------------------|---------------------------------------------|-----------------------|---------------------------------------|

| 60                   | 2                                           | 2                     | 20                                    |

| 60                   | 1                                           | 4                     | 20                                    |

| 60                   | 0.5                                         | 8                     | 20                                    |

| 100                  | 2                                           | 2                     | 19                                    |

| 100                  | 1                                           | 4                     | 19                                    |

| 100                  | 0.5                                         | 8                     | 19                                    |

TABLE VI. Effective Resolution vs Data Rate, Clock Frequency, and Turbo Mode Rate. (Gain setting of 1.) The Turbo Mode Rate (TMR) is programmed via the Sampling Frequency bits of the Command Register. Due to the increase in input capacitor sampling frequency, higher Turbo Mode settings result in lower analog input impedance;

$A_{IN}$  Impedance ( $\Omega$ ) = (1MHz/f<sub>XIN</sub>)•20E6/(G•TMR)

where G is the gain setting. Because the modulator rate also changes in direct relation to the Turbo Mode setting, higher values result in a lower impedance for the REF<sub>IN</sub> input:

$$\text{REF}_{\text{IN}}$$

Impedance ( $\Omega$ ) = (1MHz/f<sub>XIN</sub>)•5E6/TMR

The Turbo Mode Rate can be set to 1, 2, 4, 8, or 16. Consult the graphs shown in the Typical Performance Curves for full details on the performance of the ADS1212/13 operating in different Turbo Mode Rates. Keep in mind that higher Turbo Mode Rates result in fewer available gain settings as shown in Table II.

## **PROGRAMMABLE GAIN AMPLIFIER**

The programmable gain amplifier gain setting is programmed via the PGA Gain bits of the Command Register. Changes in the gain setting (G) of the programmable gain amplifier results in an increase in the input capacitor sampling frequency. Thus, higher gain settings result in a lower analog input impedance:

$A_{IN}$  Impedance ( $\Omega$ ) = (1MHz/f<sub>XIN</sub>)•20E6/(G•TMR)

where TMR is the Turbo Mode Rate. Because the modulator speed does not depend on the gain setting, the input impedance seen at  $\text{REF}_{\text{IN}}$  does not change.

The PGA can be set to gains of 1, 2, 4, 8, or 16. These gain settings with their resulting full-scale range and typical voltage range are shown in Table I. Keep in mind that higher Turbo Mode Rates result in fewer available gain settings as shown in Table II.

## SOFTWARE GAIN

The excellent performance, flexibility, and low cost of the ADS1212/13 allow the converter to be considered for designs which would not normally need a 24-bit ADC. For example, many designs utilize a 12-bit converter and a highgain INA or PGA for digitizing low amplitude signals. For some of these cases, the ADS1212/13 by itself may be a solution, even though the maximum gain is limited to 16.

To get around the gain limitation, the digital result can simply be shifted up by "n" bits in the main controller resulting in a gain of "n" times G, where G is the gain setting. While this type of manipulation of the output data is obvious, it is easy to miss how much the gain can be increased in this manner on a 24-bit converter.

For example, shifting the result up by three bits when the ADS1212/13 is set to a gain of 16 results in an effective gain of 128. At lower data rates, the converter can easily provide more than 12 bits of resolution. Even higher gains are possible. The limitation is a combination of the needed data rate, desired noise performance, and desired linearity.

## CALIBRATION

The ADS1212/13 offers several different types of calibration, and the particular calibration desired is programmed via the Command Register. In the case of Background Calibration, the calibration will repeat at regular intervals indefinitely. For all others, the calibration is performed once and then normal operation is resumed.

Each type of calibration is covered in detail in its respective section. In general, calibration is recommended immediately after power-on and whenever there is a "significant" change in the operating environment. The amount of change which should cause a re-calibration is dependent on the application, effective resolution, etc. Where high accuracy is important, re-calibration should be done on changes in temperature and power supply. In all cases, re-calibration should be done when the gain, Turbo Mode, or data rate is changed.

After a calibration has been accomplished, the Offset Calibration Register and the Full-Scale Calibration Register contain the results of the calibration. The data in these registers are accurate to the effective resolution of the ADS1212/13's mode of operation during the calibration. Thus, these values will show a variation (or noise) equivalent to a regular conversion result.

For those cases where this error must be reduced, it is tempting to consider running the calibration at a slower data rate and then increasing the converter's data rate after the calibration is complete. Unfortunately, this will not work as expected. The reason is that the results calculated at the slower data rate would not be valid for the higher data rate. Instead, the calibration should be done repeatedly. After each calibration, the results can be read and stored. After the desired number of calibrations, the main controller can compute an average and write this value into the calibration registers. The resulting error in the calibration values will be reduced by the square root of the number of calibrations which were averaged.

The calibration registers can also be used to provide system offset and gain corrections separate from those computed by the ADS1212/13. For example, these might be burned into  $E^2PROM$  during final product testing. On power-on, the main controller would load these values into the calibration registers. A further possibility is a look-up table based on the current temperature.

Note that the values in the calibration registers will vary from configuration to configuration and from part to part. There is no method of reliably computing what a particular calibration register should be to correct for a given amount of system error. It is possible to present the ADS1212/13 with a known amount of error, perform a calibration, read the desired calibration register, change the error value, perform another calibration, read the new value and use these values to interpolate an intermediate value.

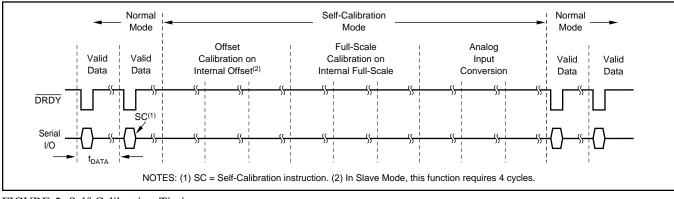

FIGURE 5. Self-Calibration Timing.

#### Self-Calibration

A self-calibration is performed after the bits 001 have been written to the Command Register Operation Mode bits (MD2 through MD0). This initiates the following sequence at the start of the next conversion cycle (see Figure 5). The DRDY signal will not go LOW but will remain HIGH and will continue to remain HIGH throughout the calibration sequence. The inputs to the sampling capacitor are disconnected from the converter's analog inputs and are shorted together. An offset calibration is performed over the next three conversion periods (four in Slave Mode). Then, the input to the sampling capacitor is connected across  $\text{REF}_{IN}$ , and a full-scale calibration is performed over the next three conversions.

After this, the Operation Mode bits are reset to 000 (Normal Mode) and the input capacitor is reconnected to the input. Conversions proceed as usual over the next three cycles in order to fill the digital filter. DRDY remains HIGH during this time. On the start of the fourth cycle, DRDY goes LOW indicating valid data and resumption of normal operation.

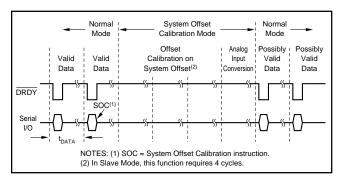

#### System Offset Calibration

A system offset calibration is performed after the bits 010 have been written to the Command Register Operation Mode bits (MD2 through MD0). This initiates the following sequence (see Figure 6). At the start of the next conversion cycle, the DRDY signal will not go LOW but will remain HIGH and will continue to remain HIGH throughout the calibration sequence. The offset calibration will be performed on the differential input voltage present at the converter's input over the next three conversion periods (four in Slave Mode). When this is done, the Operation

FIGURE 6. System Offset Calibration Timing.

Mode bits are reset to 000 (Normal Mode). A single conversion is done with  $\overrightarrow{\text{DRDY}}$  HIGH. After this conversion, the  $\overrightarrow{\text{DRDY}}$  signal goes LOW indicating resumption of normal operation.

Normal operation returns within a single conversion cycle because it is assumed that the input voltage at the converter's input is not removed immediately after the offset calibration is performed. In this case, the digital filter already contains a valid result.

For full system calibration, offset calibration must be performed first and then full-scale calibration. In addition, the offset calibration error will be the rms sum of the conversion error and the noise on the system offset voltage. See the System Calibration Limits section for information regarding the limits on the magnitude of the system offset voltage.

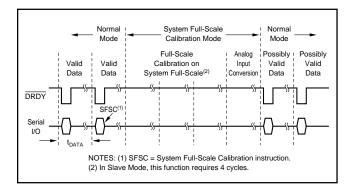

#### System Full-Scale Calibration

A system full-scale calibration is performed after the bits 011 have been written to the Command Register Operation Mode bits (MD2 through MD0). This initiates the following sequence (see Figure 7). At the start of the next conversion cycle, the DRDY signal will not go LOW but will remain HIGH and will continue to remain HIGH throughout the calibration sequence. The full-scale calibration will be performed on the differential input voltage ( $2 \cdot \text{REF}_{\text{IN}}/\text{G}$ ) present at the converter's input over the next three conversion periods (four in Slave Mode). When this is done, the Operation Mode bits are reset to 000 (Normal Mode). A single conversion is done with DRDY HIGH. After this conversion, the DRDY signal goes LOW indicating resumption of normal operation.

FIGURE 7. System Full-Scale Calibration Timing.

Normal operation returns within a single conversion cycle because it is assumed that the input voltage at the converter's input is not removed immediately after the full-scale calibration is performed. In this case, the digital filter already contains a valid result.

For full system calibration, offset calibration must be performed first and then full-scale calibration. The calibration error will be a sum of the rms noise on the conversion result and the input signal noise. See the System Calibration Limits section for information regarding the limits on the magnitude of the system full-scale voltage.

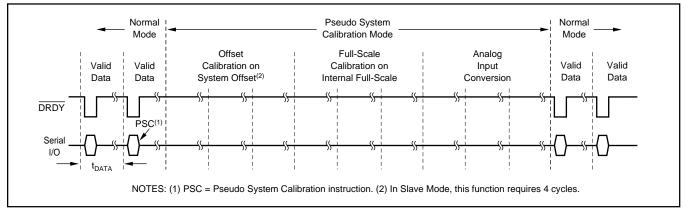

#### **Pseudo System Calibration**

The Pseudo System Calibration is performed after the bits 100 have been written to the Command Register Operation Mode bits (MD2 through MD0). This initiates the following sequence (see Figure 8). At the start of the next conversion cycle, the DRDY signal will not go LOW but will remain HIGH and will continue to remain HIGH throughout the calibration sequence. The offset calibration will be performed on the differential input voltage present at the converter's input over the next three conversion periods (four in Slave Mode). Then, the input to the sampling capacitor is disconnected from the converter's analog input and connected across  $\text{REF}_{\text{IN}}$ . A gain calibration is performed over the next three conversions.

After this, the Operation Mode bits are reset to 000 (Normal Mode) and the input capacitor is then reconnected to the input. Conversions proceed as usual over the next three cycles in order to fill the digital filter. DRDY remains HIGH during this time. On the next cycle, the DRDY signal goes LOW indicating valid data and resumption of normal operation.

The system offset calibration range of the ADS1212/13 is limited and is listed in the Specifications Table. For more information on how to use these specifications, see the System Calibration Limits section. To calculate  $V_{OS}$ , use 2 • REF<sub>IN</sub>/GAIN for  $V_{FS}$ .

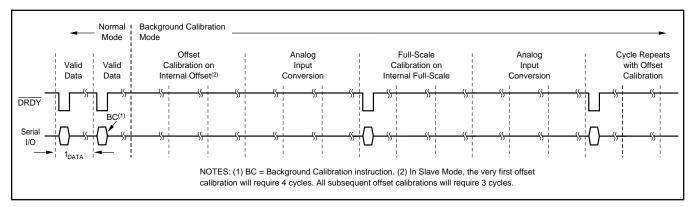

#### **Background Calibration**

The Background Calibration Mode is entered after the bits 101 have been written to the Command Register Operation Mode bits (MD2 through MD0). This initiates the following continuous sequence (see Figure 9). At the start of the next conversion cycle, the DRDY signal will not go LOW but will remain HIGH. The inputs to the sampling capacitor are disconnected from the converter's analog input and shorted together. An offset calibration is performed over the next three conversion periods (in Slave Mode, the very first offset calibration requires four periods, and all subsequent offset calibrations require three periods). Then, the input capacitor is reconnected to the input. Conversions proceed as usual over the next three cycles in order to fill the digital filter. DRDY remains HIGH during this time. On the next cycle, the DRDY signal goes LOW indicating valid data.

FIGURE 8. Pseudo System Calibration Timing.

FIGURE 9. Background Calibration Timing.

Also, during this cycle, the sampling capacitor is disconnected from the converter's analog input and is connected across  $\text{REF}_{\text{IN}}$ . A gain calibration is initiated and proceeds over the next three conversions. After this, the input capacitor is once again connected to the analog input. Conversions proceed as usual over the next three cycles in order to fill the digital filter. DRDY remains HIGH during this time. On the next cycle, the DRDY signal goes LOW indicating valid data, the input to the sampling capacitor is shorted, and an offset calibration is initiated. At this point, the Background Calibration sequence repeats.

In essence, the Background Calibration Mode performs continuous self-calibration where the offset and gain calibrations are interleaved with regular conversions. Thus, the data rate is reduced by a factor of 6. The advantage is that the converter is continuously adjusting to environmental changes such as ambient or component temperature (due to airflow variations).

The ADS1212/13 will remain in the Background Calibration Mode indefinitely. To move to any other mode, the Command Register Operation Mode bits (MD2 through MD0) must be set to the appropriate values.

# System Calibration Offset and Full-Scale Calibration Limits

The System Offset and Full-Scale Calibration range of the ADS1212/13 is limited and is listed in the Specifications Table. The range is specified as:

$$\begin{array}{l} (V_{FS} - \mid V_{OS} \mid) < 1.3 \bullet (2 \bullet REF_{IN})/GAIN \\ (V_{FS} - \mid V_{OS} \mid) > 0.7 \bullet (2 \bullet REF_{IN})/GAIN \end{array}$$

where  $V_{FS}$  is the system full-scale voltage and  $|V_{OS}|$  is the absolute value of the system offset voltage. In the following discussion, keep in mind that these voltages are differential voltages.

For example, with the internal reference (2.5V) and a gain of two, the previous equations become (after some manipulation):

$$V_{FS} - 3.25 < V_{OS} < V_{FS} - 1.75$$

If  $V_{FS}$  is perfect at 2.5V (positive full-scale), then  $V_{OS}$  must be greater than -0.75V and less than 0.75V. Thus, when offset calibration is performed, the positive input can be no more than 0.75V below or above the negative input. If this range is exceeded, the ADS1212/13 may not calibrate properly.

This calculation method works for all gains other than one. For a gain of one and the internal reference (2.5V), the equation becomes:

$$V_{FS} - 6.5 < V_{OS} < V_{FS} - 3.5$$

With a 5V positive full-scale input,  $V_{OS}$  must be greater than -1.5V and less than 1.5V. Since the offset represents a common-mode voltage and the input voltage range in a gain of one is 0V to 5V, a common-mode voltage will cause the actual input voltage to possibly go below 0V or above 5V. The specifications also show that for the specifications to be valid, the input voltage must not go below AGND by more than 30mV or above AV<sub>DD</sub> by more than 30mV.

This will be an important consideration in many systems which use a 2.5V or greater reference, as the input range is constrained by the expected power supply variations. In addition, the expected full-scale voltage will impact the allowable offset voltage (and vice-versa) as the combination of the two must remain within the power supply and ground potentials, regardless of the results obtained via the range calculation shown previously.

There are only two solutions to this constraint: either the system design must ensure that the full-scale and offset voltage variations will remain within the power supply and ground potentials, or the part must be used in a gain of 2 or greater.

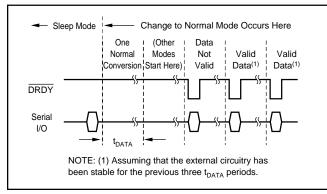

## SLEEP MODE

The Sleep Mode is entered after the bits 110 have been written to the Command Register Operation Mode bits (MD2 through MD0). This mode is exited by entering a new mode into the MD2-MD0 bits.

The Sleep Mode causes the analog section and a good deal of the digital section to power down. For full analog power down, the  $V_{BIAS}$  generator and the internal reference must also be powered down by setting the BIAS and REFO bits in the Command Register accordingly. The power dissipation shown in the Specifications Table is with the internal reference and the  $V_{BIAS}$  generator disabled.

To establish serial communication with the converter while it is in Sleep Mode, one of the following procedures must be used: If  $\overline{CS}$  is being used, simply taking  $\overline{CS}$  LOW will enable serial communication to proceed normally. If  $\overline{CS}$  is not being used (tied LOW) and the ADS1212/13 is in the Master Mode, then a falling edge must be produced on the SDIO line. If SDIO is LOW, the SDIO line must be taken HIGH for  $4 \cdot t_{XIN}$  periods (minimum) and then taken LOW. Alternatively, SDIO can be forced HIGH after putting the ADS1212/13 to "sleep" and then taken LOW when the Sleep Mode is to be exited. Finally, if  $\overline{CS}$  is not being used (tied LOW) and the ADS1212/13 is in the Slave Mode, then simply sending a normal Instruction Register command will re-establish communication.

Once serial communication is resumed, the Sleep Mode is exited by changing the MD2-MD0 bits to any other mode. When a new mode (other than Sleep) has been entered, the ADS1212/13 will execute a very brief internal power-up sequence of the analog and digital circuitry. Once this has been done, one normal conversion cycle is performed before the new mode is actually entered. At the end of this conversion cycle, the new mode takes effect and the converter will respond accordingly. The DRDY signal will remain HIGH through the first conversion cycle. It will also remain HIGH through the second, even if the new mode is the Normal Mode.

If the  $V_{BIAS}$  generator and/or the internal reference have been disabled, then they must be manually re-enabled via the appropriate bits in the Command Register. In addition, the internal reference will have to charge the external bypass capacitor(s) and possibly other circuitry. There may also be

considerations associated with  $V_{BIAS}$  and the settling of external circuitry. All of these must be taken into account when determining the amount of time required to resume normal operation. The timing diagram shown in Figure 10 does not take into account the settling of external circuitry.

FIGURE 10. Sleep Mode to Normal Mode Timing.

# ANALOG OPERATION

# ANALOG INPUT

The input impedance of the analog input changes with ADS1212/13 clock frequency ( $f_{XIN}$ ), gain (G), and Turbo Mode Rate (TMR). The relationship is:

$A_{IN}$  Impedance ( $\Omega$ ) = (1MHz/f<sub>XIN</sub>)•20E6/(G•TMR)

Figure 11 shows the basic input structure of the ADS1212. The ADS1213 includes an input multiplexer, but this has little impact on the analysis of the input structure. The impedance is directly related to the sampling frequency of the input capacitor. The  $X_{IN}$  clock rate sets the basic sampling rate in a gain of 1 and Turbo Mode Rate of 1. Higher gains and higher Turbo Mode Rates result in an increase of the sampling rate, while slower clock ( $X_{IN}$ ) frequencies result in a decrease.

FIGURE 11. Analog Input Structure.

This input impedance can become a major point of consideration in some designs. If the source impedance of the input signal is significant or if there is passive filtering prior to the ADS1212/13, then a significant portion of the signal can be lost across this external impedance. How significant this effect is depends on the desired system performance.

There are two restrictions on the analog input signal to the ADS1212/13. Under no conditions should the current into or out of the analog inputs exceed 10mA. In addition, while

the analog signal must reside within this range, the linearity of the ADS1212/13 is only ensured when the actual analog input voltage resides within a range defined by AGND – 30mV and AV<sub>DD</sub> +30mV. This is due to leakage paths which occur within the part when AGND and AV<sub>DD</sub> are exceeded.

For this reason, the 0V to 5V input range (gain of 1 with a 2.5V reference) must be used with caution. Should  $AV_{DD}$  be 4.75V, the analog input signal would swing outside of the tested specifications of the device. Designs utilizing this mode of operation should consider limiting the span to a slightly smaller range. Common-mode voltages are also a significant concern in this mode and must be carefully analyzed.

An input voltage range of 0.75V to 4.25V is the smallest span that is allowed if a full system calibration will be performed (see the Calibration section for more details). This also assumes an offset error of zero. A better choice would be 0.5V to 4.5V (a full-scale range of 9V). This span would allow some offset error, gain error, power supply drift, and common-mode voltage while still providing full system calibration over reasonable variation in each of these parameters.

The actual input voltage exceeding AGND or  $AV_{DD}$  should not be a concern in higher gain settings as the input voltage range will reside well within 0V to 5V. This is true unless the common-mode voltage is large enough to place positive fullscale or negative full-scale outside of the AGND to  $AV_{DD}$  range.

## **REFERENCE INPUT**

The input impedance of the  $\text{REF}_{\text{IN}}$  input changes with clock frequency  $(f_{\text{XIN}})$  and Turbo Mode Rate (TMR). The relationship is:

$REF_{IN}$  Impedance ( $\Omega$ ) = (1MHz/f<sub>XIN</sub>)•5E6/TMR

Unlike the analog input, the reference input impedance has a negligible dependency on the PGA gain setting.

The reference input voltage can vary between 2V and 3V. A nominal voltage of 2.5V appears at  $\text{REF}_{\text{OUT}}$ , and this can be directly connected to  $\text{REF}_{\text{IN}}$ . Higher reference voltages will cause the full-scale range to increase while the internal circuit noise of the converter remains approximately the same. This will increase the LSB weight but not the internal noise, resulting in increased signal-to-noise ratio and effective resolution. Likewise, lower reference voltages will decrease the signal-to-noise ratio and effective resolution.

# **REFERENCE OUTPUT**

The ADS1212/13 contains an internal +2.5V reference. Tolerances, drift, noise, and other specifications for this reference are given in the Specification Table. Note that it is not designed to sink or to source more than 1mA of current. In addition, loading the reference with a dynamic or variable load is not recommended. This can result in small changes in reference voltage as the load changes. Finally, for designs approaching or exceeding 20 bits of effective resolution, a low-noise external reference is recommended as the internal reference may not have adequate performance.

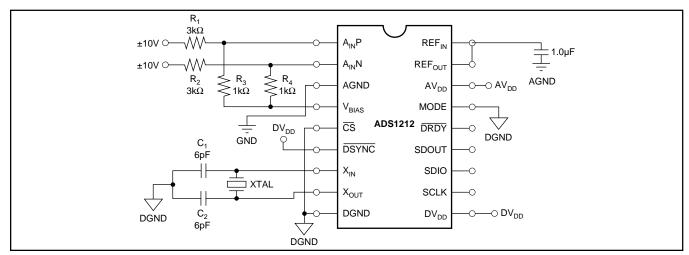

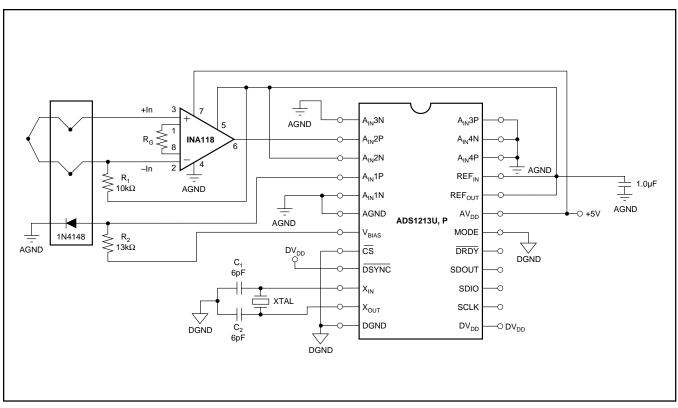

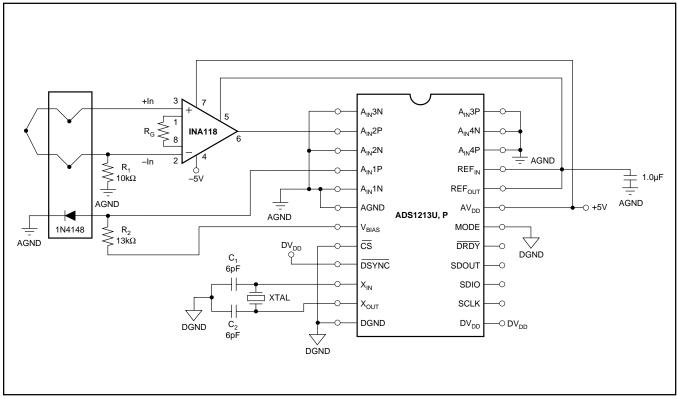

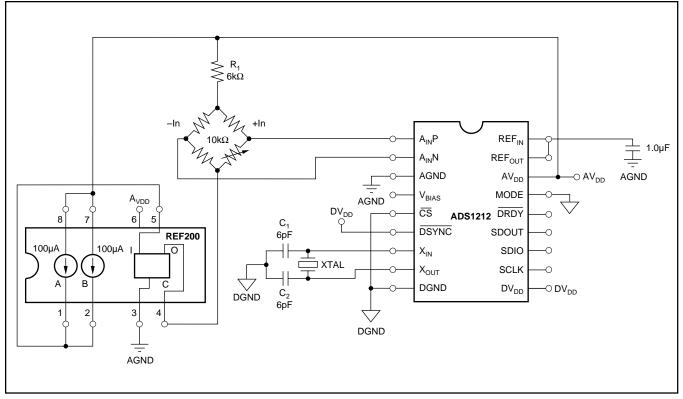

FIGURE 12. ±10V Input Configuration Using V<sub>BIAS</sub>.

The circuitry which generates the +2.5V reference can be disabled via the Command Register and will result in a lower power dissipation. The reference circuitry consumes a little over 1.6mA of current with no external load. When the ADS1212/13 is in its default state, the internal reference is enabled.

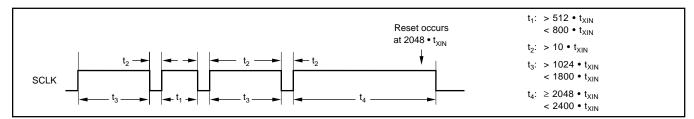

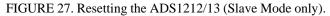

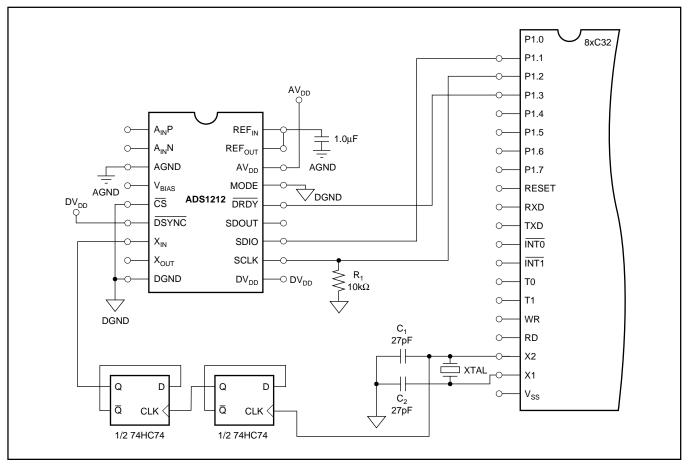

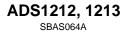

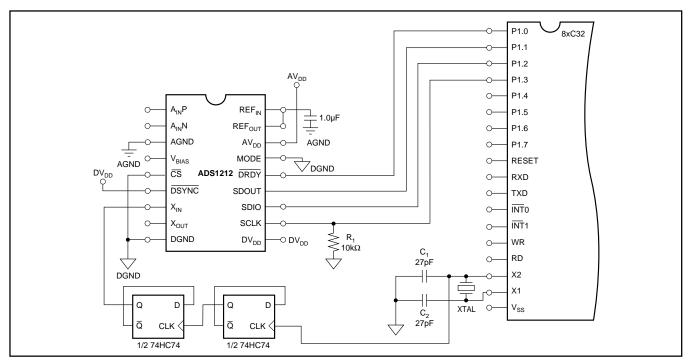

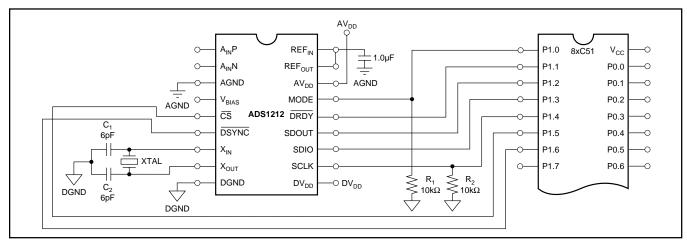

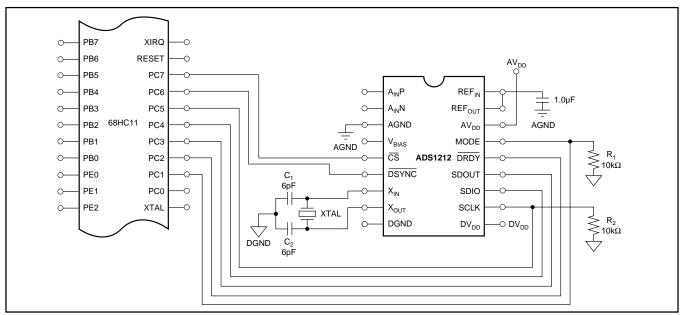

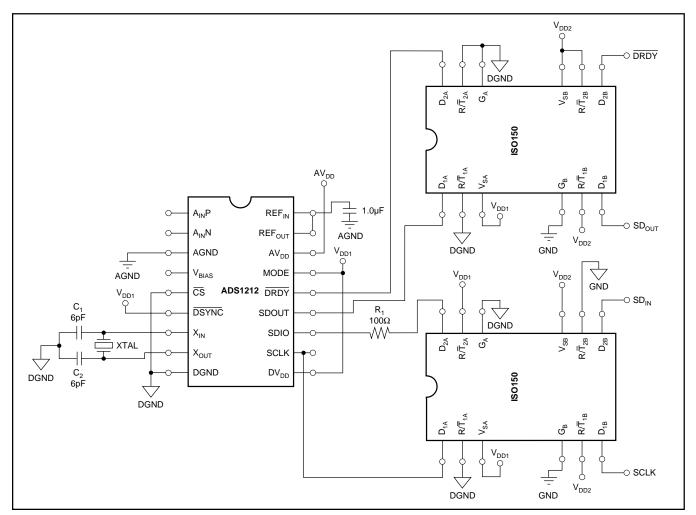

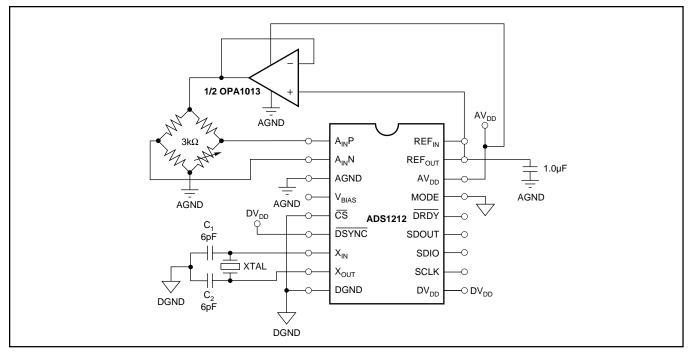

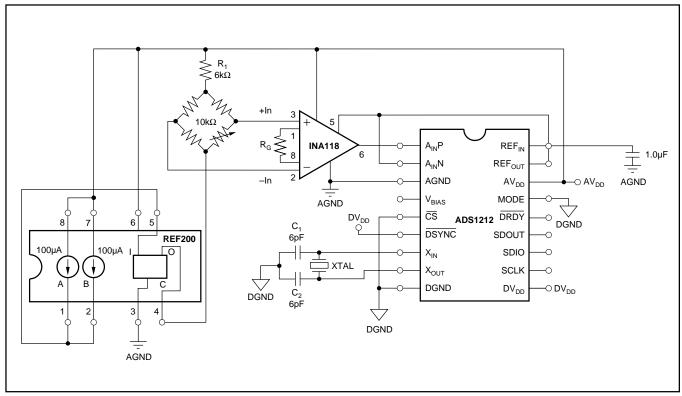

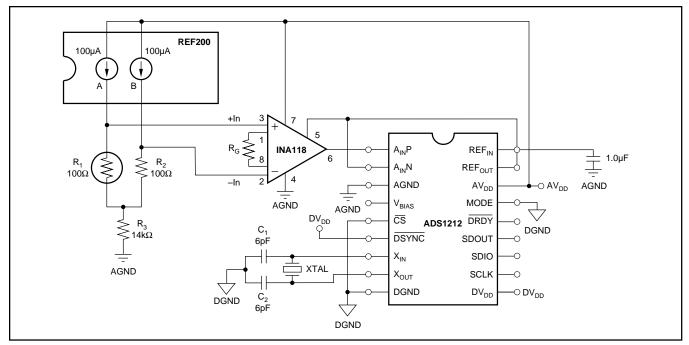

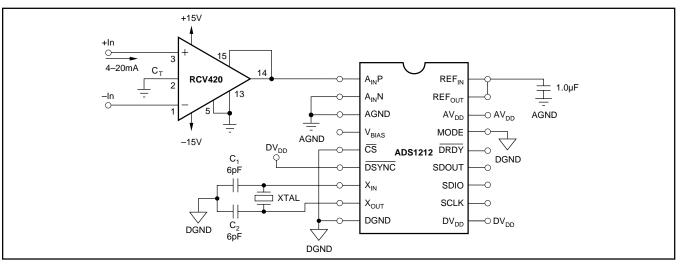

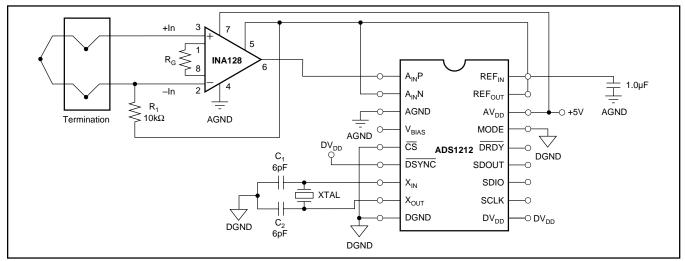

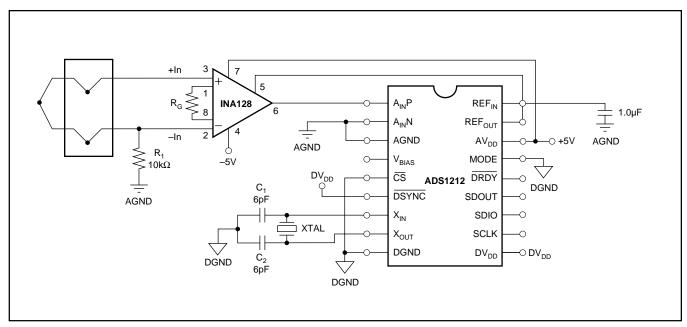

## V<sub>BIAS</sub>