# Low Cost, High Speed **Differential Amplifier**

AD8132

#### **FEATURES**

**High speed** 350 MHz -3 dB bandwidth 1200 V/us slew rate Resistor settable gain Internal common-mode feedback to improve gain and phase balance -68 dB @ 10 MHz Separate input to set the common-mode output voltage Low distortion: -99 dBc SFDR @ 5 MHz 800 Ω Load Low power: 10.7 mA @ 5 V Power supply range: +2.7 V to ±5.5 V

#### **APPLICATIONS**

Low power differential ADC drivers Differential gain and differential filtering Video line drivers Differential in/out level shifting Single-ended input to differential output drivers **Active transformers**

#### **GENERAL DESCRIPTION**

The AD8132 is a low cost differential or single-ended input to differential output amplifier with resistor settable gain. The AD8132 is a major advancement over op amps for driving differential input ADCs or for driving signals over long lines. The AD8132 has a unique internal feedback feature that provides output gain and phase matching balanced to -68 dB at 10 MHz, suppressing harmonics and reducing radiated EMI.

Manufactured using ADI's next generation XFCB bipolar process, the AD8132 has a −3 dB bandwidth of 350 MHz and delivers a differential signal with -99 dBc SFDR at 5 MHz, despite its low cost. The AD8132 eliminates the need for a transformer with high performance ADCs, preserving the low frequency and dc information. The common-mode level of the differential output is adjustable by applying a voltage on the V<sub>OCM</sub> pin, easily level shifting the input signals for driving single-supply ADCs. Fast overload recovery preserves sampling accuracy.

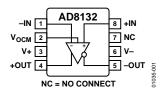

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The AD8132 can also be used as a differential driver for the transmission of high speed signals over low cost twisted pair or coaxial cables. The feedback network can be adjusted to boost the high frequency components of the signal. The AD8132 can be used for either analog or digital video signals or for other high speed data transmission. The AD8132 is capable of driving either cat3 or cat5 twisted pair or coaxial with minimal line attenuation. The AD8132 has considerable cost and performance improvements over discrete line driver solutions.

Differential signal processing reduces the effects of ground noise that plagues ground referenced systems. The AD8132 can be used for differential signal processing (gain and filtering) throughout a signal chain, easily simplifying the conversion between differential and single-ended components.

The AD8132 is available in both SOIC and MSOP packages for operation over -40°C to +125°C temperatures.

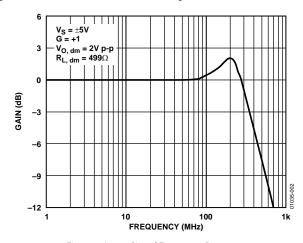

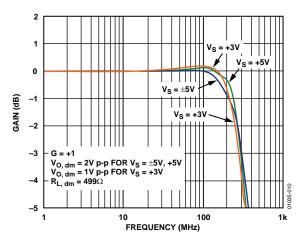

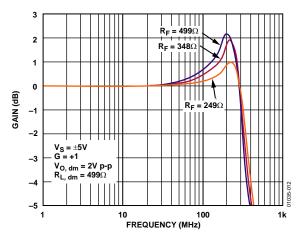

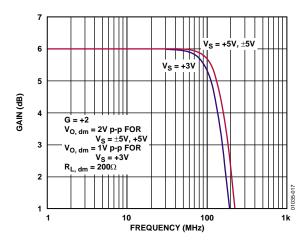

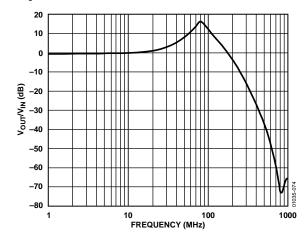

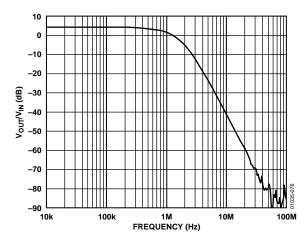

Figure 2. Large Signal Frequency Response

# **TABLE OF CONTENTS**

| Specifications                                            | Varying \$2                                                   | 22 |

|-----------------------------------------------------------|---------------------------------------------------------------|----|

| $\pm D_{IN}$ to $\pm OUT$ Specifications                  | $\beta 1 = 0$                                                 | 22 |

| V <sub>OCM</sub> to ±OUT Specifications                   | Estimating the Output Noise Voltage                           | 22 |

| ±D <sub>IN</sub> to ±OUT Specifications                   | Calculating an Application Circuit's Input Impedance          | 23 |

| V <sub>OCM</sub> to ±OUT Specifications 6                 | Input Common-Mode Voltage Range in Single-Supply Applications | 23 |

| ±D <sub>IN</sub> to ±OUT Specifications7                  | ••                                                            |    |

| V <sub>OCM</sub> to ±OUT Specifications7                  | Setting the Output Common-Mode Voltage                        | 23 |

| Absolute Maximum Ratings 8                                | Driving a Capacitive Load                                     | 23 |

| ESD Caution8                                              | Layout, Grounding, and Bypassing                              | 24 |

| Pin Configuration and Function Descriptions9              | Circuits                                                      | 24 |

| Typical Performance Characteristics                       | Applications                                                  | 25 |

| Test Circuits                                             | A/D Driver                                                    | 25 |

| Operational Description20                                 | Balanced Cable Driver                                         | 25 |

| Definition of Terms                                       | Transmit Equalizer                                            | 26 |

|                                                           | Low-Pass Differential Filter                                  | 26 |

| Basic Circuit Operation                                   | High Common-Mode Output Impedance Amplifier                   | 27 |

| Theory of Operation21                                     | Full-Wave Rectifier                                           | 27 |

| General Usage of the AD813221                             | Out Di                                                        | 20 |

| Resistorless Differential Amplifier (High Input Impedance | Outline Dimensions                                            | 29 |

| Inverting Amplifier)21                                    | Ordering Guide                                                | 29 |

| Other $\beta 2 = 1$ Circuits                              |                                                               |    |

| REVISION HISTORY                                          |                                                               |    |

| 12/04—Rev. C to Rev. D.                                   | 2/03—Rev. B to Rev. C.                                        |    |

| Changes to the General Description                        | Changes to SPECIFICATIONS                                     |    |

| Changes to the Specifications                             | Addition to Estimating the Output Noise Voltage section       |    |

| Changes to the Absolute Maximum Ratings                   | Updated OUTLINE DIMENSIONS                                    | 21 |

| Changes to the Ordering Guide                             | 1/02—Rev. A to Rev. B.                                        |    |

| Changes to the Oracinia Galacinimina.                     | Edits to TRANSMITTER FOULLIZER section                        | 1. |

## **SPECIFICATIONS**

## $\pm D_{\text{IN}}$ TO $\pm \text{OUT}$ SPECIFICATIONS

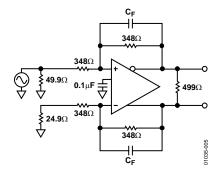

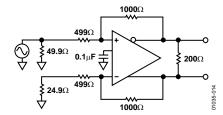

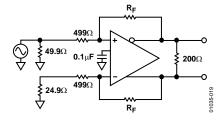

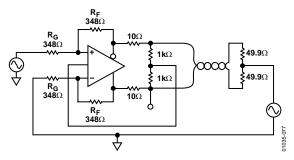

At 25°C,  $V_S = \pm 5$  V,  $V_{OCM} = 0$  V, G = 1,  $R_{L,dm} = 499$   $\Omega$ ,  $R_F = R_G = 348$   $\Omega$ , unless otherwise noted. For G = 2,  $R_{L,dm} = 200$   $\Omega$ ,  $R_F = 1000$   $\Omega$ ,  $R_G = 499$   $\Omega$ . Refer to Figure 56 and Figure 57 for test setup and label descriptions. All specifications refer to single-ended input and differential outputs, unless otherwise noted.

Table 1.

| Parameter                     | Conditions                                                                                         | Min  | Тур          | Max  | Unit               |

|-------------------------------|----------------------------------------------------------------------------------------------------|------|--------------|------|--------------------|

| DYNAMIC PERFORMANCE           |                                                                                                    |      |              |      |                    |

| -3 dB Large Signal Bandwidth  | V <sub>OUT</sub> = 2 V p-p                                                                         | 300  | 350          |      | MHz                |

|                               | $V_{OUT} = 2 \text{ V p-p, G} = 2$                                                                 |      | 190          |      | MHz                |

| -3 dB Small Signal Bandwidth  | $V_{OUT} = 0.2 \text{ V p-p}$                                                                      |      | 360          |      | MHz                |

|                               | $V_{OUT} = 0.2 \text{ V p-p, G} = 2$                                                               |      | 160          |      | MHz                |

| Bandwidth for 0.1 dB Flatness | $V_{OUT} = 0.2 \text{ V p-p}$                                                                      |      | 90           |      | MHz                |

|                               | $V_{OUT} = 0.2 \text{ V p-p, G} = 2$                                                               |      | 50           |      | MHz                |

| Slew Rate                     | $V_{OUT} = 2 V p-p$                                                                                | 1000 | 1200         |      | V/µs               |

| Settling Time                 | $0.1\%$ , $V_{OUT} = 2 V p-p$                                                                      |      | 15           |      | ns                 |

| Overdrive Recovery Time       | $V_{IN} = 5 \text{ V to } 0 \text{ V Step, } G = 2$                                                |      | 5            |      | ns                 |

| NOISE/HARMONIC PERFORMANCE    |                                                                                                    |      |              |      |                    |

| Second Harmonic               | $V_{OUT} = 2 \text{ V p-p, 1 MHz, R}_{L, dm} = 800 \Omega$                                         |      | -96          |      | dBc                |

|                               | $V_{OUT} = 2 \text{ V p-p, 5 MHz, R}_{L, dm} = 800 \Omega$                                         |      | -83          |      | dBc                |

|                               | $V_{OUT} = 2 \text{ V p-p}$ , 20 MHz, $R_{L,dm} = 800 \Omega$                                      |      | -73          |      | dBc                |

| Third Harmonic                | $V_{OUT} = 2 \text{ V p-p, 1 MHz, R}_{L, dm} = 800 \Omega$                                         |      | -102         |      | dBc                |

|                               | $V_{OUT} = 2 \text{ V p-p, 5 MHz, R}_{L, dm} = 800 \Omega$                                         |      | -98          |      | dBc                |

|                               | $V_{OUT} = 2 \text{ V p-p, } 20 \text{ MHz, } R_{L, dm} = 800 \Omega$                              |      | -67          |      | dBc                |

| IMD                           | 20 MHz, $R_{L,dm}$ = 800 Ω                                                                         |      | -76          |      | dBc                |

| IP3                           | 20 MHz, $R_{L,dm}$ = 800 Ω                                                                         |      | 40           |      | dBm                |

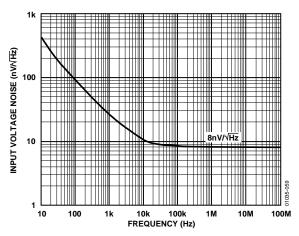

| Input Voltage Noise (RTI)     | f = 0.1 MHz to 100 MHz                                                                             |      | 8            |      | nV/√ <del>Hz</del> |

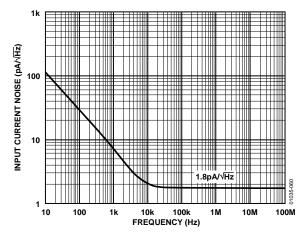

| Input Current Noise           | f = 0.1 MHz to 100 MHz                                                                             |      | 1.8          |      | pA/√Hz             |

| Differential Gain Error       | NTSC, $G = 2$ , $R_{L,dm} = 150 \Omega$                                                            |      | 0.01         |      | %                  |

| Differential Phase Error      | NTSC, $G = 2$ , $R_{L,dm} = 150 \Omega$                                                            |      | 0.10         |      | Degrees            |

| INPUT CHARACTERISTICS         |                                                                                                    |      |              |      |                    |

| Offset Voltage (RTI)          | $V_{OS, dm} = V_{OUT, dm}/2; V_{DIN+} = V_{DIN-} = V_{OCM} = 0 V$                                  |      | ±1.0         | ±3.5 | mV                 |

|                               | T <sub>MIN</sub> to T <sub>MAX</sub> Variation                                                     |      | 10           |      | μV/°C              |

| Input Bias Current            |                                                                                                    |      | 3            | 7    | μΑ                 |

| Input Resistance              | Differential                                                                                       |      | 12           |      | ΜΩ                 |

|                               | Common-Mode                                                                                        |      | 3.5          |      | ΜΩ                 |

| Input Capacitance             |                                                                                                    |      | 1            |      | pF                 |

| Input Common-Mode Voltage     |                                                                                                    |      | -4 to +3     |      | V                  |

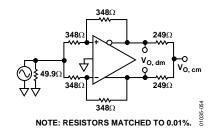

| CMRR                          | $\Delta V_{OUT, dm}/\Delta V_{IN, cm}$ ; $\Delta V_{IN, cm} = \pm 1$ V; Resistors Matched to 0.01% |      | -70          | -60  | dB                 |

| OUTPUT CHARACTERISTICS        |                                                                                                    |      |              |      |                    |

| Output Voltage Swing          | Maximum ΔV <sub>OUT</sub> ; Single-Ended Output                                                    |      | -3.6 to +3.6 |      | V                  |

| Output Current                |                                                                                                    |      | 70           |      | mA                 |

| Output Balance Error          | $\Delta V_{OUT, cm}/\Delta V_{OUT, dm}$ ; $\Delta V_{OUT, dm} = 1 \text{ V}$                       |      | -70          |      | dB                 |

## $V_{\text{OCM}}$ TO $\pm \text{OUT}$ SPECIFICATIONS

At 25°C,  $V_S = \pm 5$  V,  $V_{OCM} = 0$  V, G = 1,  $R_{L,dm} = 499$   $\Omega$ ,  $R_F = R_G = 348$   $\Omega$ , unless otherwise noted. For G = 2,  $R_{L,dm} = 200$   $\Omega$ ,  $R_F = 1000$   $\Omega$ ,  $R_G = 499$   $\Omega$ . Refer to Figure 56 and Figure 57 for test setup and label descriptions. All specifications refer to single-ended input and differential outputs, unless otherwise noted.

Table 2.

| Parameter                    | Conditions                                                                                   | Min   | Тур  | Max   | Unit               |

|------------------------------|----------------------------------------------------------------------------------------------|-------|------|-------|--------------------|

| DYNAMIC PERFORMANCE          |                                                                                              |       |      |       |                    |

| –3 dB Bandwidth              | $\Delta V_{OCM} = 600 \text{ mV p-p}$                                                        |       | 210  |       | MHz                |

| Slew Rate                    | $\Delta V_{OCM} = -1 \text{ V to } +1 \text{ V}$                                             |       | 400  |       | V/µs               |

| Input Voltage Noise (RTI)    | f = 0.1 MHz to 100 MHz                                                                       |       | 12   |       | nV/√ <del>Hz</del> |

| DC PERFORMANCE               |                                                                                              |       |      |       |                    |

| Input Voltage Range          |                                                                                              |       | ±3.6 |       | V                  |

| Input Resistance             |                                                                                              |       | 50   |       | kΩ                 |

| Input Offset Voltage         | $V_{OS, cm} = V_{OUT, cm}$ ; $V_{DIN+} = V_{DIN-} = V_{OCM} = 0 V$                           |       | ±1.5 | ±7    | mV                 |

| Input Bias Current           |                                                                                              |       | 0.5  |       | μΑ                 |

| V <sub>OCM</sub> CMRR        | $\Delta V_{OUT, dm}/\Delta V_{OCM}$ ; $\Delta V_{OCM} = \pm 1$ V; Resistors Matched to 0.01% |       | -68  |       | dB                 |

| Gain                         | $\Delta V_{OUT, cm}/\Delta V_{OCM}$ ; $\Delta V_{OCM} = \pm 1 \text{ V}$                     | 0.985 | 1    | 1.015 | V/V                |

| POWER SUPPLY                 |                                                                                              |       |      |       |                    |

| Operating Range              |                                                                                              | ±1.35 |      | ±5.5  | V                  |

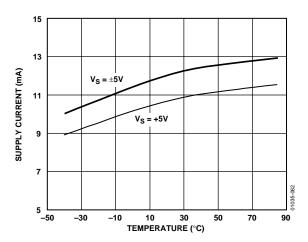

| Quiescent Current            | $V_{DIN+} = V_{DIN-} = V_{OCM} = 0 V$                                                        | 11    | 12   | 13    | mA                 |

|                              | T <sub>MIN</sub> to T <sub>MAX</sub> Variation                                               |       | 16   |       | μΑ/°C              |

| Power Supply Rejection Ratio | $\Delta V_{OUT, dm}/\Delta V_S$ ; $\Delta V_S = \pm 1 V$                                     |       | -70  | -60   | dB                 |

| OPERATING TEMPERATURE RANGE  |                                                                                              | -40   |      | +125  | °C                 |

## $\pm D_{\text{IN}}$ TO $\pm OUT$ SPECIFICATIONS

At 25°C,  $V_S = 5$  V,  $V_{OCM} = 2.5$  V, G = 1,  $R_{L,dm} = 499$   $\Omega$ ,  $R_F = R_G = 348$   $\Omega$ , unless otherwise noted. For G = 2,  $R_{L,dm} = 200$   $\Omega$ ,  $R_F = 1000$   $\Omega$ ,  $R_G = 499$   $\Omega$ . Refer to Figure 56 and Figure 57 for test setup and label descriptions. All specifications refer to single-ended input and differential outputs, unless otherwise noted.

Table 3.

| Parameter                     | Conditions                                                                                         | Min | Тур        | Max  | Unit   |

|-------------------------------|----------------------------------------------------------------------------------------------------|-----|------------|------|--------|

| DYNAMIC PERFORMANCE           |                                                                                                    |     |            |      |        |

| –3 dB Large Signal Bandwidth  | $V_{OUT} = 2 V p-p$                                                                                | 250 | 300        |      | MHz    |

|                               | $V_{OUT} = 2 V p-p, G = 2$                                                                         |     | 180        |      | MHz    |

| -3 dB Small Signal Bandwidth  | $V_{OUT} = 0.2 \text{ V p-p}$                                                                      |     | 360        |      | MHz    |

|                               | $V_{OUT} = 0.2 \text{ V p-p, G} = 2$                                                               |     | 155        |      | MHz    |

| Bandwidth for 0.1 dB Flatness | $V_{OUT} = 0.2 \text{ V p-p}$                                                                      |     | 65         |      | MHz    |

|                               | $V_{OUT} = 0.2 \text{ V p-p, G} = 2$                                                               |     | 50         |      | MHz    |

| Slew Rate                     | $V_{OUT} = 2 V p-p$                                                                                | 800 | 1000       |      | V/µs   |

| Settling Time                 | $0.1\%$ , $V_{OUT} = 2 V p-p$                                                                      |     | 20         |      | ns     |

| Overdrive Recovery Time       | $V_{IN} = 2.5 \text{ V to } 0 \text{ V Step, G} = 2$                                               |     | 5          |      | ns     |

| NOISE/HARMONIC PERFORMANCE    |                                                                                                    |     |            |      |        |

| Second Harmonic               | $V_{OUT} = 2 \text{ V p-p, 1 MHz, R}_{L,dm} = 800 \Omega$                                          |     | -97        |      | dBc    |

|                               | $V_{OUT} = 2 \text{ V p-p, 5 MHz, R}_{L, dm} = 800 \Omega$                                         |     | -100       |      | dBc    |

|                               | $V_{OUT} = 2 \text{ V p-p, } 20 \text{ MHz, } R_{L, dm} = 800 \Omega$                              |     | -74        |      | dBc    |

| Third Harmonic                | $V_{OUT} = 2 \text{ V p-p, 1 MHz, R}_{L, dm} = 800 \Omega$                                         |     | -100       |      | dBc    |

|                               | $V_{OUT} = 2 \text{ V p-p, 5 MHz, R}_{L, dm} = 800 \Omega$                                         |     | <b>-99</b> |      | dBc    |

|                               | $V_{OUT} = 2 \text{ V p-p, } 20 \text{ MHz, } R_{L, dm} = 800 \Omega$                              |     | -67        |      | dBc    |

| IMD                           | 20 MHz, $R_{L,dm}$ = 800 Ω                                                                         |     | -76        |      | dBc    |

| IP3                           | 20 MHz, $R_{L,dm}$ = 800 $Ω$                                                                       |     | 40         |      | dBm    |

| Input Voltage Noise (RTI)     | f = 0.1 MHz to 100 MHz                                                                             |     | 8          |      | nV/√Hz |

| Input Current Noise           | f = 0.1 MHz to 100 MHz                                                                             |     | 1.8        |      | pA/√Hz |

| Differential Gain Error       | NTSC, $G = 2$ , $R_{L,dm} = 150 \Omega$                                                            |     | 0.025      |      | %      |

| Differential Phase Error      | NTSC, $G = 2$ , $R_{L,dm} = 150 \Omega$                                                            |     | 0.15       |      | Degree |

| INPUT CHARACTERISTICS         |                                                                                                    |     |            |      |        |

| Offset Voltage (RTI)          | $V_{OS, dm} = V_{OUT, dm}/2$ ; $V_{DIN+} = V_{DIN-} = V_{OCM} = 2.5 \text{ V}$                     |     | ±1.0       | ±3.5 | mV     |

|                               | T <sub>MIN</sub> to T <sub>MAX</sub> Variation                                                     |     | 6          |      | μV/°C  |

| Input Bias Current            |                                                                                                    |     | 3          | 7    | μΑ     |

| Input Resistance              | Differential                                                                                       |     | 10         |      | ΜΩ     |

|                               | Common-Mode                                                                                        |     | 3          |      | ΜΩ     |

| Input Capacitance             |                                                                                                    |     | 1          |      | pF     |

| Input Common-Mode Voltage     |                                                                                                    |     | 1 to 3     |      | V      |

| CMRR                          | $\Delta V_{OUT, dm}/\Delta V_{IN, cm}$ ; $\Delta V_{IN, cm} = \pm 1$ V; Resistors Matched to 0.01% |     | -70        | -60  | dB     |

| OUTPUT CHARACTERISTICS        |                                                                                                    |     |            |      |        |

| Output Voltage Swing          | Maximum ΔV <sub>OUT</sub> ; Single-Ended Output                                                    |     | 1.0 to 4.0 |      | V      |

| Output Current                |                                                                                                    |     | 50         |      | mA     |

| Output Balance Error          | $\Delta V_{OUT, cm}/\Delta V_{OUT, dm}$ ; $\Delta V_{OUT, dm} = 1 \text{ V}$                       |     | -68        |      | dB     |

## $V_{\text{OCM}}$ TO $\pm \text{OUT}$ SPECIFICATIONS

At 25°C,  $V_S = 5$  V,  $V_{OCM} = 2.5$  V, G = 1,  $R_{L,dm} = 499$   $\Omega$ ,  $R_F = R_G = 348$   $\Omega$ , unless otherwise noted. For G = 2,  $R_{L,dm} = 200$   $\Omega$ ,  $R_F = 1000$   $\Omega$ ,  $R_G = 499$   $\Omega$ . Refer to Figure 56 and Figure 57 for test setup and label descriptions. All specifications refer to single-ended input and differential outputs, unless otherwise noted.

Table 4.

| Parameter                    | Conditions                                                                                                          | Min   | Тур        | Max   | Unit               |

|------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|------------|-------|--------------------|

| DYNAMIC PERFORMANCE          |                                                                                                                     |       |            |       |                    |

| –3 dB Bandwidth              | $\Delta V_{OCM} = 600 \text{ mV p-p}$                                                                               |       | 210        |       | MHz                |

| Slew Rate                    | $\Delta V_{OCM} = 1.5 \text{ V to } 3.5 \text{ V}$                                                                  |       | 340        |       | V/µs               |

| Input Voltage Noise (RTI)    | f = 0.1 MHz to 100 MHz                                                                                              |       | 12         |       | nV/√ <del>Hz</del> |

| DC PERFORMANCE               |                                                                                                                     |       |            |       |                    |

| Input Voltage Range          |                                                                                                                     |       | 1.0 to 3.7 |       | V                  |

| Input Resistance             |                                                                                                                     |       | 30         |       | kΩ                 |

| Input Offset Voltage         | $V_{OS, cm} = V_{OUT, cm}; V_{DIN+} = V_{DIN-} = V_{OCM} = 2.5 \text{ V}$                                           |       | ±5         | ±11   | mV                 |

| Input Bias Current           |                                                                                                                     |       | 0.5        |       | μΑ                 |

| V <sub>OCM</sub> CMRR        | $\Delta V_{OUT, dm}/\Delta V_{OCM}$ ; $\Delta V_{OCM} = 2.5 \text{ V} \pm 1 \text{ V}$ ; Resistors Matched to 0.01% |       | -66        |       | dB                 |

| Gain                         | $\Delta V_{OUT, cm}/\Delta V_{OCM}$ ; $\Delta V_{OCM} = 2.5 \text{ V} \pm 1 \text{ V}$                              | 0.985 | 1          | 1.015 | V/V                |

| POWER SUPPLY                 |                                                                                                                     |       |            |       |                    |

| Operating Range              |                                                                                                                     | 2.7   |            | 11    | V                  |

| Quiescent Current            | $V_{DIN+} = V_{DIN-} = V_{OCM} = 2.5 \text{ V}$                                                                     | 9.4   | 10.7       | 12    | mA                 |

|                              | T <sub>MIN</sub> to T <sub>MAX</sub> Variation                                                                      |       | 10         |       | μΑ/°C              |

| Power Supply Rejection Ratio | $\Delta V_{OUT, dm}/\Delta V_s$ ; $\Delta V_s = \pm 1 V$                                                            |       | -70        | -60   | dB                 |

| OPERATING TEMPERATURE RANGE  |                                                                                                                     | -40   |            | +125  | °C                 |

### $\pm D_{\text{IN}}$ TO $\pm OUT$ SPECIFICATIONS

At 25°C,  $V_S = 3$  V,  $V_{OCM} = 1.5$  V, G = 1,  $R_{L,dm} = 499$   $\Omega$ ,  $R_F = R_G = 348$   $\Omega$  unless otherwise noted. For G = 2,  $R_{L,dm} = 200$   $\Omega$ ,  $R_F = 1000$   $\Omega$ ,  $R_G = 499$   $\Omega$ . Refer to Figure 56 and Figure 57 for test setup and label descriptions. All specifications refer to single-ended input and differential outputs, unless otherwise noted.

Table 5.

| Parameter                     | Conditions                                                                                           | Min | Тур  | Max | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| DYNAMIC PERFORMANCE           |                                                                                                      |     |      |     |      |

| –3 dB Large Signal Bandwidth  | $V_{OUT} = 1 V p-p$                                                                                  |     | 350  |     | MHz  |

|                               | $V_{OUT} = 1 \text{ V p-p, G} = 2$                                                                   |     | 165  |     | MHz  |

| -3 dB Small Signal Bandwidth  | $V_{OUT} = 0.2 \text{ V p-p}$                                                                        |     | 350  |     | MHz  |

|                               | $V_{OUT} = 0.2 \text{ V p-p, G} = 2$                                                                 |     | 150  |     | MHz  |

| Bandwidth for 0.1 dB Flatness | $V_{OUT} = 0.2 \text{ V p-p}$                                                                        |     | 45   |     | MHz  |

|                               | $V_{OUT} = 0.2 \text{ V p-p, G} = 2$                                                                 |     | 50   |     | MHz  |

| NOISE/HARMONIC PERFORMANCE    |                                                                                                      |     |      |     |      |

| Second Harmonic               | $V_{OUT} = 1 \text{ V p-p, } 1 \text{ MHz, } R_{L,dm} = 800 \Omega$                                  |     | -100 |     | dBc  |

|                               | $V_{OUT} = 1 \text{ V p-p, 5 MHz, R}_{L,dm} = 800 \Omega$                                            |     | -94  |     | dBc  |

|                               | $V_{OUT} = 1 \text{ V p-p, } 20 \text{ MHz, } R_{L,dm} = 800 \Omega$                                 |     | -77  |     | dBc  |

| Third Harmonic                | $V_{OUT} = 1 \text{ V p-p, } 1 \text{ MHz, } R_{L,dm} = 800 \Omega$                                  |     | -90  |     | dBc  |

|                               | $V_{OUT} = 1 \text{ V p-p, 5 MHz, } R_{L,dm} = 800 \Omega$                                           |     | -85  |     | dBc  |

|                               | $V_{OUT} = 1 \text{ V p-p, } 20 \text{ MHz, } R_{L,dm} = 800 \Omega$                                 |     | -66  |     | dBc  |

| INPUT CHARACTERISTICS         |                                                                                                      |     |      |     |      |

| Offset Voltage (RTI)          | $V_{OS, dm} = V_{OUT, dm}/2$ ; $V_{DIN+} = V_{DIN-} = V_{OCM} = 1.5 \text{ V}$                       |     | ±10  |     | mV   |

| Input Bias Current            |                                                                                                      |     | 3    |     | μΑ   |

| CMRR                          | $\Delta V_{OUT, dm}/\Delta V_{IN, cm}$ ; $\Delta V_{IN, cm} = \pm 0.5$ V; Resistors Matched to 0.01% |     | -60  |     | dB   |

### **V<sub>OCM</sub> TO ±OUT SPECIFICATIONS**

At 25°C,  $V_S = 3$  V,  $V_{OCM} = 1.5$  V, G = 1,  $R_{L,dm} = 499$   $\Omega$ ,  $R_F = R_G = 348$   $\Omega$  unless otherwise noted. For G = 2,  $R_{L,dm} = 200$   $\Omega$ ,  $R_F = 1000$   $\Omega$ ,  $R_G = 499$   $\Omega$ . Refer to Figure 56 and Figure 57 for test setup and label descriptions. All specifications refer to single-ended input and differential outputs, unless otherwise noted.

Table 6.

| Parameter                    | Conditions                                                                   | Min | Тур  | Max  | Unit |

|------------------------------|------------------------------------------------------------------------------|-----|------|------|------|

| DC PERFORMANCE               |                                                                              |     |      |      |      |

| Input Offset Voltage         | $V_{OS, cm} = V_{OUT, cm}$ ; $V_{DIN+} = V_{DIN-} = V_{OCM} = 1.5 \text{ V}$ |     | ±7   |      | mV   |

| Gain                         | $\Delta V_{OUT, cm}/\Delta V_{OCM}$ ; $\Delta V_{OCM} = \pm 0.5 \text{ V}$   |     | 1    |      | V/V  |

| POWER SUPPLY                 |                                                                              |     |      |      |      |

| Operating Range              |                                                                              | 2.7 |      | 11   | V    |

| Quiescent Current            | $V_{DIN+} = V_{DIN-} = V_{OCM} = 0 V$                                        |     | 7.25 |      | mA   |

| Power Supply Rejection Ratio | $\Delta V_{OUT, dm}/\Delta V_S$ ; $\Delta V_S = \pm 0.5 \text{ V}$           |     | -70  |      | dB   |

| OPERATING TEMPERATURE RANGE  |                                                                              | -40 |      | +125 | °C   |

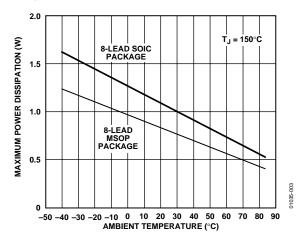

## **ABSOLUTE MAXIMUM RATINGS**

Table 7. 1

| Parameter                           | Ratings                            |

|-------------------------------------|------------------------------------|

| Supply Voltage                      | ±5.5 V                             |

| V <sub>OCM</sub>                    | ±V <sub>S</sub>                    |

| Internal Power Dissipation          | 250 mW                             |

| Operating Temperature Range         | −40°C to +125°C<br>−65°C to +150°C |

| Storage Temperature Range           | −65°C to +150°C                    |

| Lead Temperature (Soldering 10 sec) | 300°C                              |

$<sup>^{1}</sup>$  Thermal resistance measured on SEMI-standard, 4-layer board. 8-Lead SOIC:  $\theta_{JA}$  = 121°C/W 8-Lead MSOP:  $\theta_{JA}$  = 142°C/W

Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational section of this specification is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

Figure 3. Plot of Maximum Power Dissipation vs. Temperature

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin |          |                                                                                                                                                                  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Mnemonic | Description                                                                                                                                                      |

| 1   | -IN      | Negative Input.                                                                                                                                                  |

| 2   | Vосм     | Voltage applied to this pin sets the common-mode output voltage with a ratio of 1:1. For example, 1 V dc on Vocm sets the dc bias level on +OUT and -OUT to 1 V. |

| 3   | V+       | Positive Supply Voltage.                                                                                                                                         |

| 4   | +OUT     | Positive Output. Note that the voltage at $-D_{IN}$ is inverted at $+OUT$ (see Figure 64).                                                                       |

| 5   | -OUT     | Negative Output. Note that the voltage at $+D_{IN}$ is inverted at $-OUT$ (see Figure 64).                                                                       |

| 6   | V-       | Negative Supply Voltage.                                                                                                                                         |

| 7   | NC       | No Connect.                                                                                                                                                      |

| 8   | +IN      | Positive Input.                                                                                                                                                  |

## TYPICAL PERFORMANCE CHARACTERISTICS

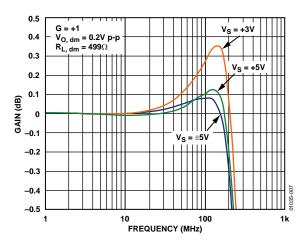

Figure 5. Small Signal Frequency Response (See Figure 56)

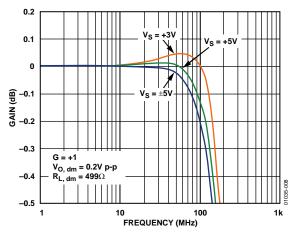

Figure 6. 0.1 dB Flatness vs. Frequency  $C_F = 0$  pF (See Figure 56)

Figure 7. 0.1 dB Flatness vs. Frequency  $C_F = 0.5 pF$  (See Figure 56)

Figure 8. Large Signal Frequency Response;  $C_F = 0$  pF (See Figure 56)

Figure 9. Large Signal Frequency Response;  $C_F = 0.5 pF$  (See Figure 56)

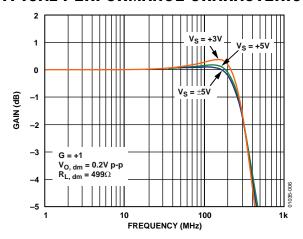

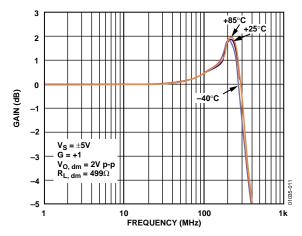

Figure 10. Large Signal Response vs. Temperature (See Figure 56)

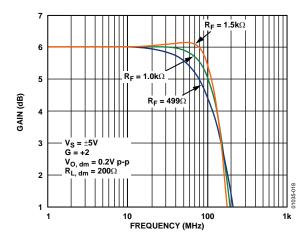

Figure 11. Large Signal Frequency Response vs. R<sub>F</sub> (See Figure 56)

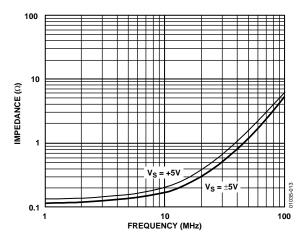

Figure 12. Closed-Loop Single-Ended  $Z_{OUT}$  vs. Frequency; G = 1 (See Figure 56)

Figure 13. Small Signal Frequency Response (See Figure 57)

Figure 14. 0.1 dB Flatness vs. Frequency (See Figure 57)

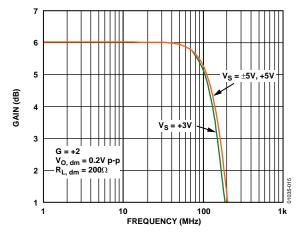

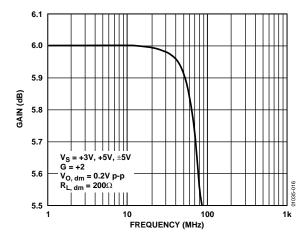

Figure 15. Large Signal Frequency Response (See Figure 57)

Figure 16. Small Signal Frequency Response vs. R<sub>F</sub> (See Figure 57)

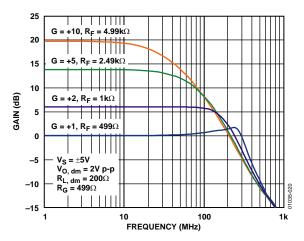

Figure 17. Large Signal Response for Various Gains (See Figure 58)

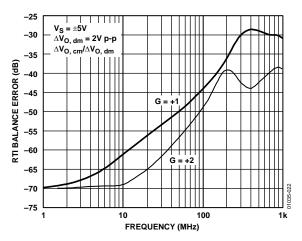

Figure 18. RTI Output Balance Error vs. Frequency (See Figure 59)

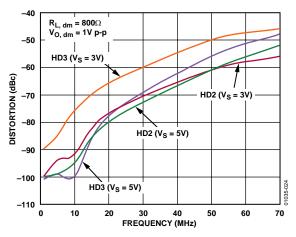

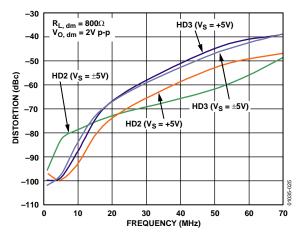

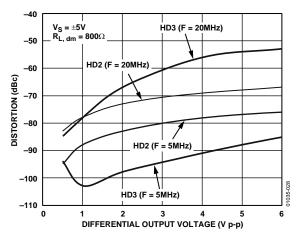

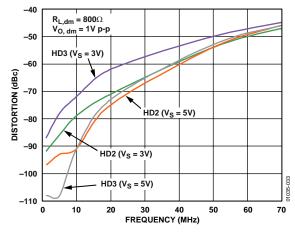

Figure 19. Harmonic Distortion vs. Frequency, G = 1 (See Figure 62)

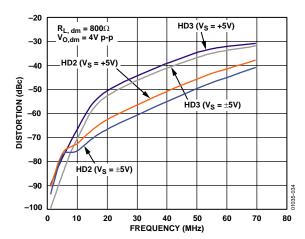

Figure 20. Harmonic Distortion vs. Frequency, G = 1 (See Figure 62)

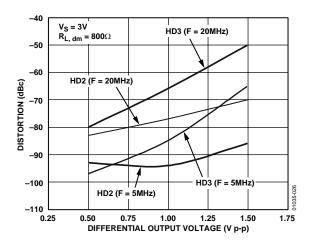

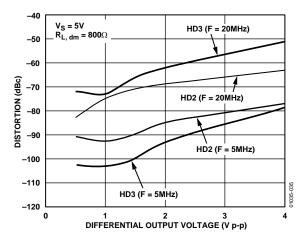

Figure 21. Harmonic Distortion vs.

Differential Output Voltage, G = 1 (See Figure 62)

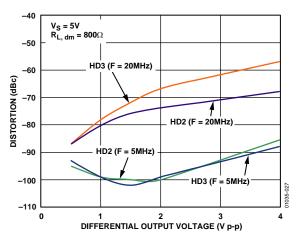

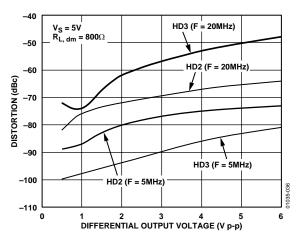

Figure 22. Harmonic Distortion vs.

Differential Output Voltage, G = 1 (See Figure 62)

Figure 23. Harmonic Distortion vs.

Differential Output Voltage, G = 1 (See Figure 62)

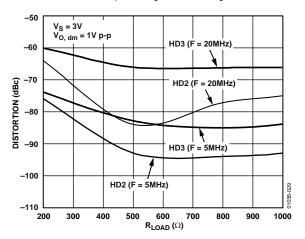

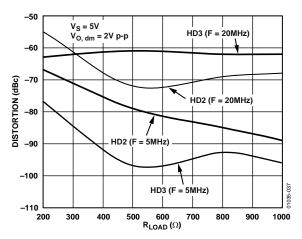

Figure 24. Harmonic Distortion vs.  $R_{LOAD}$ , G = 1 (See Figure 62)

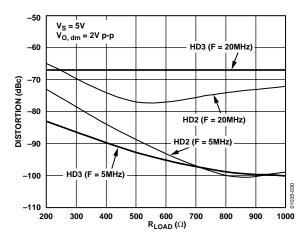

Figure 25. Harmonic Distortion vs.  $R_{LOAD}$ , G = 1 (See Figure 62)

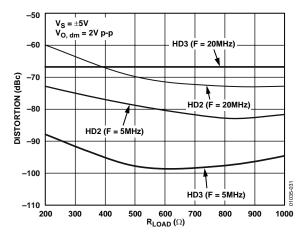

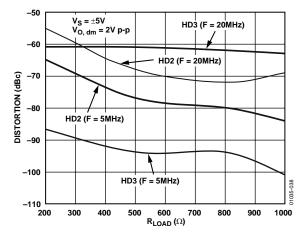

Figure 26. Harmonic Distortion vs.  $R_{LOAD}$ , G = 1 (See Figure 62)

Figure 27. Harmonic Distortion vs. Frequency, G = 2 (See Figure 63)

Figure 28. Harmonic Distortion vs. Frequency, G = 2 (See Figure 63)

Figure 29. Harmonic Distortion vs. Differential Output Voltage, G = 2 (See Figure 63)

Figure 30. Harmonic Distortion vs.

Differential Output Voltage, G = 2 (See Figure 63)

Figure 31. Harmonic Distortion vs.  $R_{LOAD}$ , G = 2 (See Figure 63)

Figure 32. Harmonic Distortion vs.  $R_{LOAD}$ , G = 2 (See Figure 63)

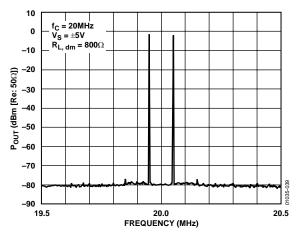

Figure 33. Intermodulation Distortion, G = 1

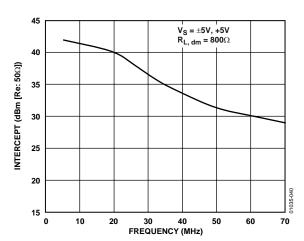

Figure 34. Third-Order Intercept vs. Frequency, G = 1

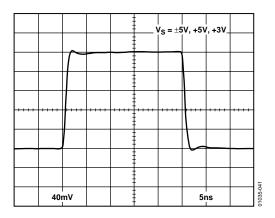

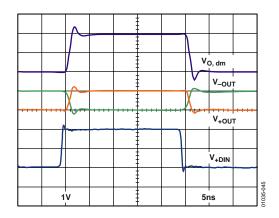

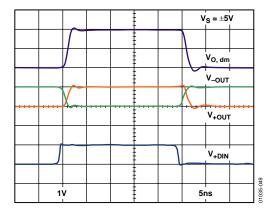

Figure 35. Small Signal Transient Response, G = 1

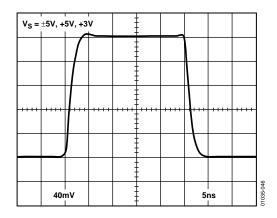

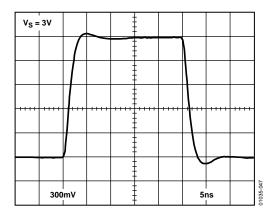

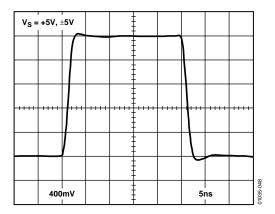

Figure 36. Large Signal Transient Response, G = 1

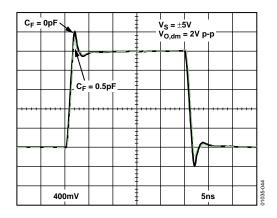

Figure 37. Large Signal Transient Response, G = 1

Figure 38. Large Signal Transient Response, G = 1

Figure 39. Large Signal Transient Response, G = 1

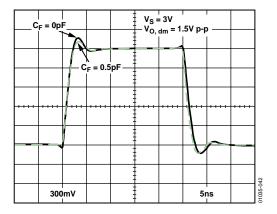

Figure 40. Small Signal Transient Response, G = 2

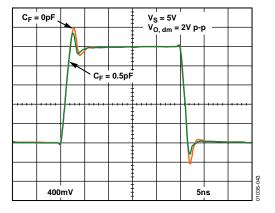

Figure 41. Large Signal Transient Response, G = 2

Figure 42. Large Signal Transient Response, G = 2

Figure 43. Large Signal Transient Response, G = 2

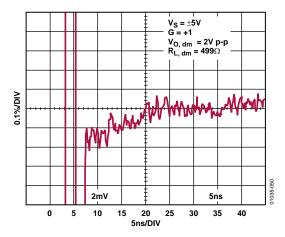

Figure 44. 0.1% Settling Time

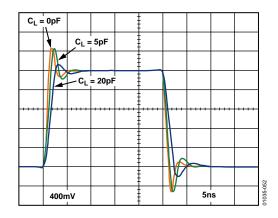

Figure 45. Large Signal Transient Response for Various Capacitor Loads (See Figure 60)

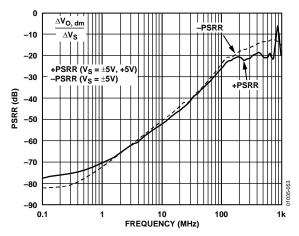

Figure 46. PSRR vs. Frequency

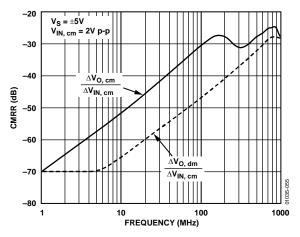

Figure 47. CMRR vs. Frequency (See Figure 61)

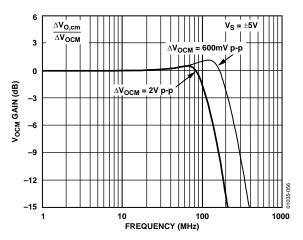

Figure 48. V<sub>OCM</sub> Gain Response

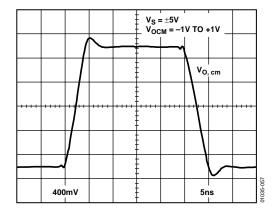

Figure 49. Vocm Transient Response

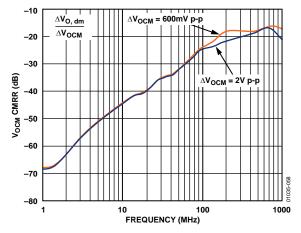

Figure 50. Vocm CMRR vs. Frequency

Figure 51. Input Voltage Noise vs. Frequency

Figure 52. Input Current Noise vs. Frequency

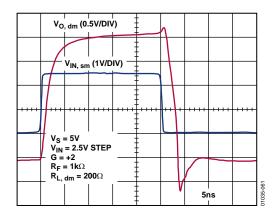

Figure 53. Overdrive Recovery

Figure 54. Quiescent Current vs. Temperature

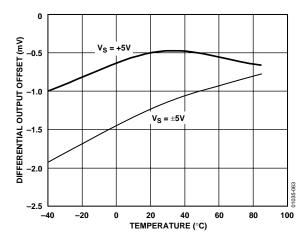

Figure 55. Differential Offset Voltage vs. Temperature

## **TEST CIRCUITS**

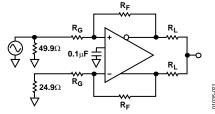

Figure 56. Basic Test Circuit, G = 1

Figure 57. Basic Test Circuit, G = 2

Figure 58. Test Circuit for Various Gains

$\begin{array}{l} G = +1 \colon R_F = R_G = 348 \Omega, \ R_L = 249 \Omega \ (R_{L,\ dm} = 498 \Omega) \\ G = +2 \colon R_F = 1000 \Omega, \ R_G = 499 \Omega, \ R_L = 100 \Omega \ (R_{L,\ dm} = 200 \Omega) \end{array}$

Figure 59. Test Circuit for Output Balance

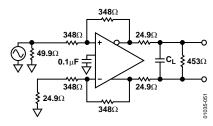

Figure 60. Test Circuit for Capacitor Load Drive

Figure 61. CMRR Test Circuit

Figure 62. Harmonic Distortion Test Circuit, G = 1,  $R_{L,dm}$  = 800  $\Omega$

Figure 63. Harmonic Distortion Test Circuit, G = 2,  $R_{L,dm} = 800 \Omega$

## OPERATIONAL DESCRIPTION

#### **DEFINITION OF TERMS**

#### **Differential Voltage**

The difference between two node voltages. For example, the output differential voltage (or equivalently output differential-mode voltage) is defined as

$$V_{OUT, dm} = (V_{+OUT} - V_{-OUT})$$

where  $V_{+OUT}$  and  $V_{-OUT}$  refer to the voltages at the +OUT and -OUT terminals with respect to a common reference.

#### Common-Mode Voltage

The average of two node voltages. The output common-mode voltage is defined as

$$V_{OUT, cm} = (V_{+OUT} - V_{-OUT})/2$$

Figure 64. Circuit Definitions

#### **BASIC CIRCUIT OPERATION**

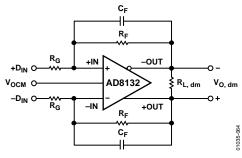

One of the more useful and easy to understand ways to use the AD8132 is to provide two equal-ratio feedback networks. To match the effect of parasitics, these networks should actually be comprised of two equal-value feedback resistors,  $R_{\text{F}}$ , and two equal-value gain resistors,  $R_{\text{G}}$ . This circuit is shown in Figure 64.

Like a conventional op amp, the AD8132 has two differential inputs that can be driven with both a differential-mode input voltage,  $V_{\rm IN,dm}$ , and a common-mode input voltage,  $V_{\rm IN,cm}$ .

There is another input,  $V_{\text{OCM}}$ , that is not present on conventional op amps but provides another input to consider on the AD8132. It is totally separate from the above inputs.

There are two complementary outputs whose response can be defined by a differential-mode output,  $V_{\text{OUT,dm}}$ , and a common-mode output,  $V_{\text{OUT,cm}}$ .

Table 9 indicates the gain from any type of input to either type of output.

Table 9. Differential- and Common-Mode Gains

| Input               | V <sub>OUT, dm</sub>           | V <sub>OUT, cm</sub> |

|---------------------|--------------------------------|----------------------|

| V <sub>IN, dm</sub> | R <sub>F</sub> /R <sub>G</sub> | 0 (By Design)        |

| $V_{IN,cm}$         | 0                              | 0 (By Design)        |

| $V_{OCM}$           | 0                              | 1 (By Design)        |

The differential output  $(V_{\text{OUT,dm}})$  is equal to the differential input voltage  $(V_{\text{IN,dm}})$  times  $R_F/R_G$ . In this case, it does not matter if both differential inputs are driven, or only one output is driven and the other is tied to a reference voltage, such as ground. As is seen from the two zero entries in the first column, neither of the common-mode inputs has any effect on this gain.

The gain from  $V_{\rm IN,dm}$  to  $V_{\rm OUT,cm}$  is 0, and first-order does not depend on the ratio matching of the feedback networks. The common-mode feedback loop within the AD8132 provides a corrective action to keep this gain term minimized. The term balance error describes the degree to which this gain term differs from 0.

The gain from  $V_{\rm IN,\,cm}$  to  $V_{\rm OUT,\,dm}$  directly depends on the matching of the feedback networks. The analogous term for this transfer function, which is used in conventional op amps, is common-mode rejection ratio (CMRR). Therefore, if it has a high CMRR, the feedback ratios must be well matched.

The gain from  $V_{\rm IN,\,cm}$  to  $V_{\rm OUT,\,cm}$  is also ideally 0 and is first-order independent of the feedback ratio matching. As in the case of  $V_{\rm IN,\,dm}$  to  $V_{\rm OUT,\,cm}$ , the common-mode feedback loop keeps this term minimized.

The gain from  $V_{\text{OCM}}$  to  $V_{\text{OUT,dm}}$  is ideally 0 when the feedback ratios are matched only. The amount of differential output signal that is created by varying  $V_{\text{OCM}}$  is related to the degree of mismatch in the feedback networks.

$V_{\rm OCM}$  controls the output common-mode voltage  $V_{\rm OUT,\,cm}$  with a unity-gain transfer function. With equal-ratio feedback networks (as assumed above), its effect on each output is the same, which is another way of saying that the gain from  $V_{\rm OCM}$  to  $V_{\rm OUT,\,dm}$  is 0. If not driven, the output common-mode is at midsupply. It is recommended that a 0.1  $\mu F$  bypass capacitor be connected to  $V_{\rm OCM}$ .

When unequal feedback ratios are used, the two gains associated with  $V_{\text{OUT,dm}}$  become nonzero. This significantly complicates the mathematical analysis along with any intuitive understanding of how the part operates.

## THEORY OF OPERATION

The AD8132 differs from conventional op amps by the external presence of an additional input and output. The additional input,  $V_{\text{OCM}}$ , controls the output common-mode voltage. The additional output is the analog complement of the single output of a conventional op amp. For its operation, the AD8132 uses two feedback loops as compared to the single loop of conventional op amps. While this provides significant freedom to create various novel circuits, basic op amp theory can still be used to analyze the operation.

One of the feedback loops controls the output common-mode voltage,  $V_{\rm OUT,cm}$ . Its input is  $V_{\rm OCM}$  (Pin 2) and the output is the common-mode, or average voltage, of the two differential outputs (+OUT and -OUT). The gain of this circuit is internally set to unity. When the AD8132 is operating in its linear region, this establishes one of the operational constraints:  $V_{\rm OUT,cm} = V_{\rm OCM}$ .

The second feedback loop controls the differential operation. Similar to an op amp, the gain and gain-shaping of the transfer function can be controlled by adding passive feedback networks. However, only one feedback network is required to close the loop and fully constrain the operation, but depending on the function desired, two feedback networks can be used. This is possible as a result of having two outputs that are each inverted with respect to the differential inputs.

#### **GENERAL USAGE OF THE AD8132**

Several assumptions are made here for a first-order analysis; they are the typical assumptions used for the analysis of op amps:

- The input bias currents are sufficiently small so they can be neglected.

- The output impedances are arbitrarily low.

- The open-loop gain is arbitrarily large, which drives the amplifier to a state where the input differential voltage is effectively 0.

- Offset voltages are assumed to be 0.

While it is possible to operate the AD8132 with a purely differential input, many of its applications call for a circuit that has a single-ended input with a differential output.

For a single-ended-to-differential circuit, the  $R_G$  of the undriven input is tied to a reference voltage. This is ground and other conditions are discussed later. Also, the voltage at  $V_{\rm OCM}$ , and therefore  $V_{\rm OUT,\,cm}$ , is assumed to be ground for now. Figure 65 shows a generalized schematic of such a circuit using an AD8132 with two feedback paths.

For each feedback network, a feedback factor can be defined as the fraction of the output signal that is fed back to the opposite sign input. These terms are:

$$\beta 1 = R_{GI} / \left( R_{GI} + R_{FI} \right)$$

$$\beta 2 = R_{G2} / (R_{G2} + R_{F2})$$

The feedback factor  $\beta 1$  is for the side that is driven, while the feedback factor  $\beta 2$  is for the side that is tied to a reference voltage (ground for now). Note also that each feedback factor can vary anywhere between 0 and 1.

A single-ended-to-differential gain equation can be derived, which is true for all values of  $\beta 1$  and  $\beta 2$ .

$$G = 2 \times (1 - \beta 1)/(\beta 1 + \beta 2)$$

This expression is not very intuitive, but some further examples can provide better understanding of its implications. One observation that can be made right away is that a tolerance error in  $\beta 1$  does not have the same effect on gain as the same tolerance error in  $\beta 2$ .

# RESISTORLESS DIFFERENTIAL AMPLIFIER (HIGH INPUT IMPEDANCE INVERTING AMPLIFIER)

The simplest closed-loop circuit that can be made does not require any resistors and is shown in Figure 68. In this circuit,  $\beta 1$  is equal to 0, and  $\beta 2$  is equal to 1. The gain is equal to 2.

A more intuitive means to figure the gain is by simple inspection. +OUT is connected to -IN, whose voltage is equal to the voltage at +IN under equilibrium conditions. Thus, + $V_{\rm OUT}$  is equal to  $V_{\rm IN}$ , and there is unity gain in this path. Because -OUT has to swing in the opposite direction from +OUT due to the common-mode constraint, its effect doubles the output signal and produces a gain of 2.

One useful function that this circuit provides is a high input impedance inverter. If +OUT is ignored, there is a unity-gain, high input impedance amplifier formed from +IN to -OUT. Most traditional op amp inverters have relatively low input impedances, unless they are buffered with another amplifier.

$V_{\rm OCM}$  has been assumed to be at midsupply. Because there is still the constraint from the above discussion that  $+V_{\rm OUT}$  must equal  $V_{\rm IN}$ , changing the  $V_{\rm OCM}$  voltage does not change  $+V_{\rm OUT}$  (=  $V_{\rm IN}$ ). Therefore, the effect of changing  $V_{\rm OCM}$  must show up at -OUT.

For example, if  $V_{\text{OCM}}$  is raised by 1 V, then  $-V_{\text{OUT}}$  must go up by 2 V. This makes  $V_{\text{OUT,cm}}$  also go up by 1 V, since it is defined as the average of the two differential output voltages. This means that the gain from  $V_{\text{OCM}}$  to the differential output is 2.

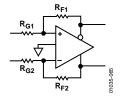

#### OTHER $\beta 2 = 1$ CIRCUITS

The preceding simple configuration with  $\beta 2 = 1$  and its gain of 2 is the highest gain circuit that can be made under this condition. Since  $\beta 1$  was equal to 0, only higher  $\beta 1$  values are possible. The circuits with higher values of  $\beta 1$  have gains lower than 2. However, circuits with  $\beta 1$  equal to 1 are not practical because they have no effective input and result in a gain of 0.

To increase  $\beta 1$  from 0, it is necessary to add two resistors in a feedback network. A generalized circuit that has  $\beta 1$  with a value higher than 0 is shown in Figure 67. A couple of different convenient gains that can be created are a gain of 1, when  $\beta 1$  is equal to 1/3, and a gain of 0.5, when  $\beta 1$  equals 0.6.

With  $\beta 2$  equal to 1 in these circuits,  $V_{\text{OCM}}$  serves as the reference voltage from which to measure the input voltage and the individual output voltages. In general, when  $V_{\text{OCM}}$  is varied in these circuits, a differential output signal generates in addition to  $V_{\text{OUT,cm}}$  changing the same amount as the voltage change of  $V_{\text{OCM}}$ .

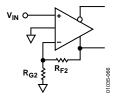

### **VARYING β2**

While the circuit above sets  $\beta 2$  to 1, another class of simple circuits can be made that sets  $\beta 2$  equal to 0. This means that there is no feedback from +OUT to –IN. This class of circuits is very similar to a conventional inverting op amp. However, the AD8132 circuits have an additional output and common-mode input that can be analyzed separately (see Figure 69).

With –IN connected to ground, +IN becomes a virtual ground in the sense that the term is used for conventional op amps. Both inputs must maintain the same voltage for equilibrium operation; therefore, if one is set to ground, the other is driven to ground. The input impedance can also be seen to be equal to R<sub>G</sub>, just as in a conventional op amp.

In this case, however, the positive input and negative output are used for the feedback network. Because a conventional op amp does not have a negative output, only its inverting input can be used for the feedback network. The AD8132 is symmetrical, therefore, the feedback network on either side can be used to produce the same results.

Because +IN is a summing junction, by analog-to-conventional op amps, the gain from  $V_{\rm IN}$  to -OUT is  $-R_{\rm F}/R_{\rm G}$ . This holds true regardless of the voltage on  $V_{\rm OCM}$ , and since +OUT moves the same amount in the opposite direction from –OUT, the overall gain is  $-2(R_{\rm F}/R_{\rm G})$ .

$V_{\rm OCM}$  still governs  $V_{\rm OUT,\,cm},$  so +OUT must be the only output that moves when  $V_{\rm OCM}$  is varied. Because  $V_{\rm OUT,\,cm}$  is the average of the two outputs, +OUT must move twice as far and in the same direction as  $V_{\rm OCM}$  to create the proper  $V_{\rm OUT,\,cm}.$  Therefore, the gain from  $V_{\rm OCM}$  to +OUT must be 2.

With  $\beta 2$  equal to 0 in these circuits, the gain can theoretically be set to any value from close to 0 to infinity, just as it can with a conventional op amp in the inverting mode. However, practical real-world limitations and parasitics limit the range of acceptable gain to more modest values.

### $\beta 1 = 0$

There is yet another class of circuits where there is no feedback from -OUT to +IN. This is the case where  $\beta 1 = 0$ . The resistorless differential amplifier described above meets this condition, but it was presented only with the condition that  $\beta 2 = 1$ . Recall that this circuit had a gain equal to 2.

If  $\beta 2$  decreases in this circuit from unity, a smaller part of +VOUT is fed back to –IN and the gain increases (see Figure 66). This circuit is very similar to a noninverting op amp configuration, except for the presence of the additional complementary output. Therefore, the overall gain is twice that of a noninverting op amp or  $2 \times (1 + R_{F2}/R_{G2})$  or  $2 \times (1/\beta 2)$ .

Once again, varying  $V_{\text{OCM}}$  does not affect both outputs in the same way; therefore, in addition to varying  $V_{\text{OUT, cm}}$  with unity gain, there is also an effect on  $V_{\text{OUT, dm}}$  by changing  $V_{\text{OCM}}$ .

#### **ESTIMATING THE OUTPUT NOISE VOLTAGE**

Similar to the case of a conventional op amp, the differential output errors (noise and offset voltages) can be estimated by multiplying the input referred terms, at +IN and –IN, by the circuit noise gain. The noise gain is defined as

$$G_N = 1 + \left(\frac{R_F}{R_G}\right)$$

To compute the total output referred noise for the circuit of Figure 64, consideration must also be given to the contribution of the resistors R<sub>F</sub> and R<sub>G</sub>. Refer to Table 10 for estimated output noise voltage densities at various closed-loop gains.

Table 10. Recommended Resistor Values and Noise Performance for Specific Gains

| Gain | R <sub>G</sub><br>(Ω) | $R_{F}$ ( $\Omega$ ) | Bandwidth<br>-3 dB<br>(MHz) | Output<br>Noise<br>AD8132<br>Only<br>(nV/√Hz) | Output<br>Noise<br>AD8132 +<br>R <sub>G</sub> , R <sub>F</sub><br>(nV/√Hz) |

|------|-----------------------|----------------------|-----------------------------|-----------------------------------------------|----------------------------------------------------------------------------|

| 1    | 499                   | 499                  | 360                         | 16                                            | 17                                                                         |

| 2    | 499                   | 1.0 k                | 160                         | 24.1                                          | 26.1                                                                       |

| 5    | 499                   | 2.49 k               | 65                          | 48.4                                          | 53.3                                                                       |

| 10   | 499                   | 4.99 k               | 20                          | 88.9                                          | 98.6                                                                       |

When using the AD8132 in gain configurations where  $\beta_1 \neq \beta_2$ , differential output noise appears due to input-referred voltage noise in the  $V_{\text{OCM}}$  circuitry according to the formula

$$V_{OND} = 2 V_{NOCM} \left[ \frac{\beta 1 - \beta 2}{\beta 1 + \beta 2} \right]$$

where  $V_{OND}$  is the output differential noise, and  $V_{NOCM}$  is the input-referred voltage noise on  $V_{OCM}$ .

# CALCULATING AN APPLICATION CIRCUIT'S INPUT IMPEDANCE

The effective input impedance of a circuit, such as that in Figure 64, at  $+D_{IN}$  and  $-D_{IN}$ , depends on whether the amplifier is being driven by a single-ended or differential signal source. For balanced differential input signals, the input impedance  $(R_{IN,dm})$  between the inputs  $(+D_{IN}$  and  $-D_{IN})$  is simply

$$R_{IN,dm} = 2 \times R_G$$

In the case of a single-ended input signal (for example, if  $-D_{\rm IN}$  is grounded and the input signal is applied to  $+D_{\rm IN}$ ), the input impedance becomes

$$R_{IN,dm} = \left(\frac{R_G}{1 - \frac{R_F}{2 \times (R_G + R_F)}}\right)$$

The circuit's input impedance is effectively higher than it would be for a conventional op amp connected as an inverter because a fraction of the differential output voltage appears at the inputs as a common-mode signal, partially bootstrapping the voltage across the input resistor, R<sub>G</sub>.

# INPUT COMMON-MODE VOLTAGE RANGE IN SINGLE-SUPPLY APPLICATIONS

The AD8132 is optimized for level-shifting ground referenced input signals. For a single-ended input this would imply, for example, that the voltage at  $-D_{\rm IN}$  in Figure 64 would be 0 V when the amplifier's negative power supply voltage (at V–) was also set to 0 V.

#### SETTING THE OUTPUT COMMON-MODE VOLTAGE

The AD8132's  $V_{\rm OCM}$  pin is internally biased at a voltage approximately equal to the midsupply point (average value of the voltage on V+ and V−). Relying on this internal bias results in an output common-mode voltage that is within approximately 100 mV of the expected value.

In cases where more accurate control of the output common-mode level is required, it is recommended that an external source or resistor divider (with  $R_{\text{SOURCE}} < 10 \ k\Omega)$  be used. The output common-mode offset values in the Specifications section assume the  $V_{\text{OCM}}$  input is driven by a low impedance voltage source.

#### **DRIVING A CAPACITIVE LOAD**

A purely capacitive load can react with the pin and bond-wire inductance of the AD8132, resulting in high frequency ringing in the pulse response. One way to minimize this effect is to place a small capacitor across each of the feedback resistors. The added capacitance should be small to avoid destabilizing the amplifier. An alternative technique is to place a small resistor in series with the amplifier's outputs, as shown in Figure 60.

## LAYOUT, GROUNDING, AND BYPASSING

As a high speed part, the AD8132 is sensitive to the PCB environment in which it operates. Realizing its superior specifications requires attention to various details of good high speed PCB design.

The first requirement is a good solid ground plane that covers as much of the board area around the AD8132 as possible. The only exception to this is that the two input pins (Pins 1 and 8) should be kept a few millimeters from the ground plane, and ground should be removed from inner layers and the opposite side of the board under the input pins. This minimizes the stray capacitance on these nodes and helps preserve the gain flatness vs. the frequency.

The power supply pins should be bypassed as close as possible to the device to the nearby ground plane. Good high frequency ceramic chip capacitors should be used. This bypassing should be done with a capacitance value of 0.01  $\mu F$  to 0.1  $\mu F$  for each supply. Further away, low frequency bypassing should be provided with 10  $\mu F$  tantalum capacitors from each supply to ground.

The signal routing should be short and direct in order to avoid parasitic effects. Wherever there are complementary signals, a symmetrical layout should be provided to the extent possible to maximize the balance performance. When running differential signals over a long distance, the traces on the PCB should be close together or any differential wiring should be twisted together to minimize the area of the loop that is formed. This reduces the radiated energy and makes the circuit less susceptible to interference.

#### **CIRCUITS**

Figure 65. Typical Four-Resistor Feedback Circuit

Figure 66. Typical Circuit with  $\beta 1 = 0$

Figure 67. Typical Circuit with  $\beta 2 = 1$

Figure 68. Resistorless G = 2 Circuit with  $\beta 1 = 0$

Figure 69. Typical Circuit with  $\beta 2 = 0$

### **APPLICATIONS**

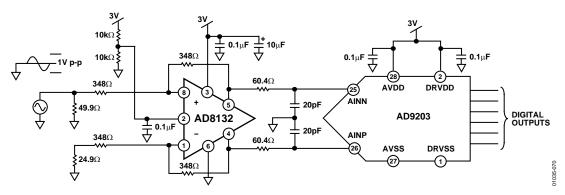

#### A/D DRIVER

Many of the newer high speed ADCs are single-supply and have differential inputs. Thus, the driver for these devices should be able to convert from a single-ended to a differential signal and provide output common-mode level-shifting in addition to having low distortion and noise. The AD8132 conveniently performs these functions when driving the AD9203, a 10-bit, 40 MSPS ADC.

In Figure 71, a 1 V p-p signal drives the input of an AD8132 configured for unity gain. Both the AD8132 and the AD9203 are powered from a single 3 V supply. A voltage divider biases  $V_{\text{OCM}}$  at midsupply, which in turn drives  $V_{\text{OUT,cm}}$  to half of the supply voltage. This is within the common-mode range of the AD9203.

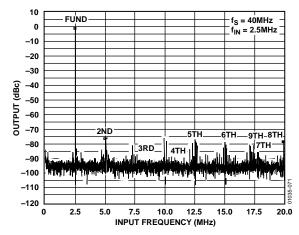

Between the A/D and the driver is a 1-pole, differential filter that helps to filter some of the noise and assists the switched-capacitor inputs of the A/D. Each of the A/D inputs is driven by a 0.5 V p-p signal that ranges from 1.25 V dc to 1.75 V dc. Figure 70 is an FFT plot of the performance of the circuit when running at a clock rate of 40 MSPS and an input frequency of 2.5 MHz.

Figure 70. FTT Response for AD8132 Driving AD9203

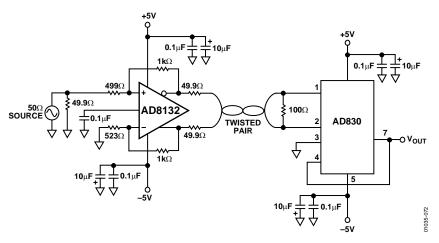

#### **BALANCED CABLE DRIVER**

When driving a twisted pair cable, it is desirable to drive only a pure differential signal onto the line. If the signal is purely differential (i.e., fully balanced), and the transmission line is twisted and balanced, there is a minimum radiation of any signal.

The complementary electrical fields are mostly confined to the space between the two twisted conductors and does not significantly radiate out from the cable. The current in the cable creates magnetic fields that radiate to some degree. However, the amount of radiation is mitigated by the twists, because for each twist, the two adjacent twists have an opposite polarity magnetic field. If the twist pitch is tight enough, these small magnetic field loops contain most of the magnetic flux, and the magnetic far-field strength is negligible.

Figure 71. AD8132 Driving AD9203, a 10-Bit, 40 MSPS ADC

Figure 72. Balanced Line Driver and Receiver Using AD8132 and AD830

Any imbalance in the differential drive signal appears as a common-mode signal on the cable. This is the equivalent of a single wire that is driven with the common-mode signal. In this case, the wire acts as an antenna and radiates. Thus, in order to minimize radiation when driving differential twisted pair cables, the differential drive signal should be very well-balanced.

The common-mode feedback loop in the AD8132 helps to minimize the amount of common-mode voltage at the output, and can therefore be used to create a well-balanced differential line driver. Figure 72 shows an application that uses an AD8132 as a balanced line driver and an AD830 as a differential receiver configured for unity gain. This circuit was operated with 10 m of Category 5 cable.

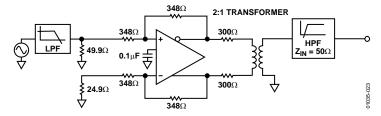

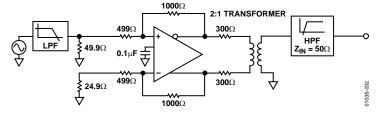

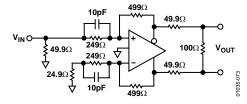

#### TRANSMIT EQUALIZER

Any length of transmission line attenuates the signals it carries. This effect is worse at higher frequencies than at low frequencies. One way to compensate for this is to provide an equalizer circuit that boosts the higher frequencies in the transmitter circuit, so that at the receive end of the cable, the attenuation effects are diminished.

By lowering the impedance of the  $R_G$  component of the feedback network at a higher frequency, the gain can be increased at a high frequency. Figure 73 shows the gain of a two line driver that has its  $R_G$  resistors shunted by 10 pF capacitors. The effect of this is shown in the frequency response plot of Figure 74.

Figure 73. Frequency Boost Circuit

Figure 74. Frequency Response for transmit Boost Circuit

#### **LOW-PASS DIFFERENTIAL FILTER**

Similar to an op amp, various types of active filters can be created with the AD8132. These can have single-ended inputs and differential outputs, which can provide an antialias function when driving a differential ADC.

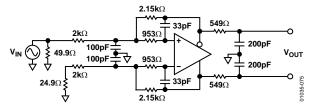

Figure 75 is a schematic of a low-pass, multiple feedback filter. The active section contains two poles, and an additional pole is added at the output. The filter was designed to have a -3 dB frequency of 1 MHz. The actual -3 dB frequency was measured to be 1.12 MHz, as shown in Figure 76.

Figure 75. 1 MHz, 3-Pole Differential Output, Low-Pass, Multiple Feedback Filter

Figure 76. Frequency Response of 1 MHz Low-Pass Filter

# HIGH COMMON-MODE OUTPUT IMPEDANCE AMPLIFIER

Changing the connection to  $V_{\rm OCM}$  (Pin 2) can change the common-mode from low impedance to high impedance. If  $V_{\rm OCM}$  is actively set to a particular voltage, the AD8132 tries to force  $V_{\rm OUT,\,cm}$  to the same voltage with a relatively low output impedance. All the previous analysis assumed that this output impedance is arbitrarily low enough to drive the load condition in the circuit.

However, there are some applications that benefit from a high common-mode output impedance. This can be accomplished with the circuit shown in Figure 77.

Figure 77. High Common-Mode, Output Impedance, Differential Amplifier

$V_{\rm OCM}$  is driven by a resistor divider that measures the output common-mode voltage. Thus, the common-mode output voltage takes on the value that is set by the driven circuit. In this case, it comes from the center point of the termination at the receive end of a 10 m length of Category 5 twisted pair cable.

If the receive end, common-mode voltage is set to ground, it is well-defined at the receive end. Any common-mode signal that is picked up over the cable length due to noise appears at the transmit end and must be absorbed by the transmitter. Thus, it is important that the transmitter have adequate common-mode output range to absorb the full amplitude of the common-mode signal coupled onto the cable and therefore prevent clipping.

Another way to look at this is that the circuit performs what is sometimes called transformer action. One main difference is that the AD8132 passes dc while transformers do not.

A transformer can also be easily configured to have either a high or low common-mode output impedance. If the transformer's center tap is connected to a solid voltage reference, it sets the common-mode voltage on the secondary side of the transformer. In this case, if one of the differential outputs is grounded, the other output will have only half of the differential output signal. This keeps the common-mode voltage at ground, where it is required to be due to the center tap connection. This is analogous to the AD8132 operating with a low output impedance common-mode (see Figure 78).

Figure 78. Transformer Whose Low Output Impedance Secondary Is Set at V<sub>OCM</sub>

If the center tap of the secondary of a transformer is allowed to float as shown in Figure 79 (or if there is no center tap), the transformer will have a high common-mode output impedance. This means that the common mode of the secondary is determined by what it is connected to and not by anything to do with the transformer itself.

If one of the differential ends of the transformer is grounded, the other end swings with the full output voltage. This means that the common-mode of the output voltage is one-half of the differential output voltage. However, this shows that the common-mode is not forced via a low impedance to a given voltage. The common-mode output voltage can be changed easily to any voltage through its other output terminals.

The AD8132 can exhibit the same performance when one of the outputs in Figure 77 is grounded. The other output swings at the full differential output voltage. The common-mode signal is measured by the voltage divider across the outputs and input to  $V_{\rm OCM}$ . This then drives  $V_{\rm OUT,\,cm}$  to the same level. At higher frequencies, it is important to minimize the capacitance on the  $V_{\rm OCM}$  node or else phase shifts can compromise the performance. The voltage divider resistances can also be lowered for better frequency response.

Figure 79. Transformer with High Output Impedance Secondary

#### **FULL-WAVE RECTIFIER**

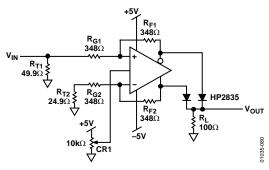

The balanced outputs of the AD8132, along with a couple of Schottky diodes, can create a very high speed, full-wave rectifier. Such circuits are useful for measuring ac voltages and other computational tasks.

Figure 80 shows the configuration of such a circuit. Each of the AD8132 outputs drives the anode of an HP2835 Schottky diode. These Schottky diodes were chosen for their high speed operation. At lower frequencies (approximately lower than 10 MHz), a silicon signal diode, such as a 1N4148, can be used. The cathodes of the two diodes are connected together, and this output node is connected to ground by a 100  $\Omega$  resistor.

Figure 80. Full-Wave Rectifier

The diodes should be operated such that they are slightly forward-biased when the differential output voltage is 0. For the Schottky diodes, this is approximately 400 mV. The forward biasing can be conveniently adjusted by CR1, which, in this circuit, raises and lowers  $V_{\rm OUT,cm}$  without creating a differential output voltage.

One advantage of this circuit is that the feedback loop is never momentarily opened while the diodes reverse their polarity within the loop. This is the scheme that is sometimes used for full-wave rectifiers that use conventional op amps. These conventional circuits do not work well at frequencies above approximately 1 MHz.

If there is not enough forward-bias ( $V_{\rm OUT,cm}$  too low), the lower sharp cusps of the full-wave rectified output waveform will be rounded off. Also, as the frequency increases, there tends to be some rounding of the lower cusps. The forward bias can be increased to yield sharper cusps at higher frequencies.

There is not a reliable, entirely quantifiable means to measure the performance of a full-wave rectifier. Since the ideal waveform has periodic sharp discontinuities, it should have (mostly even) harmonics that have no upper bound on the frequency. However, for a practical circuit, as the frequency increases, the higher harmonics become attenuated and the sharp cusps that are present at low frequencies become significantly rounded.

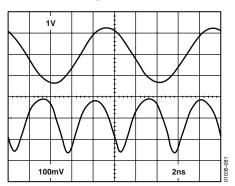

The circuit was run at a frequency up to 300 MHz and, while it was still functional, the major harmonic that remained in the output was the second. This made it look like a sine wave at 600 MHz. Figure 81 is an oscilloscope plot of the output when driven by a 100 MHz, 2.5 V p-p input.

Sometimes a second harmonic generator is actually useful for creating a clock to oversample a DAC by a factor of two. If the output of this circuit is run through a low-pass filter, it can be used as a second harmonic generator.

Figure 81. Full-Wave Rectifier Response with 100 MHz Input

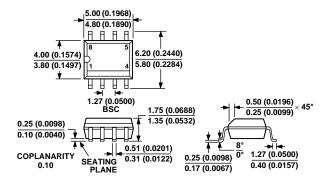

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 82. 8-Lead Standard Small Outline Package [SOIC] Narrow Body (R-8) Dimensions shown in millimeters and (inches)

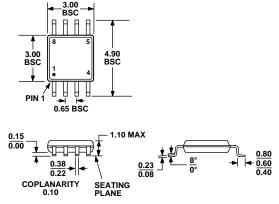

**COMPLIANT TO JEDEC STANDARDS MO-187AA**

Figure 83. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                         | Temperature Range | Package Description                     | Package Option | Branding |

|-------------------------------|-------------------|-----------------------------------------|----------------|----------|

| AD8132AR                      | -40°C to +125°C   | 8-Lead SOIC                             | R-8            |          |

| AD8132AR-REEL                 | −40°C to +125°C   | 8-Lead SOIC, 13" Tape and Reel of 2,500 | R-8            |          |

| AD8132AR-REEL7                | −40°C to +125°C   | 8-Lead SOIC, 7" Tape and Reel of 1,000  | R-8            |          |

| AD8132ARZ <sup>1</sup>        | −40°C to +125°C   | 8-Lead SOIC                             | R-8            |          |

| AD8132ARZ-REEL <sup>1</sup>   | −40°C to +125°C   | 8-Lead SOIC, 13" Tape and Reel of 2,500 | R-8            |          |

| AD8132ARZ-REEL7 <sup>1</sup>  | −40°C to +125°C   | 8-Lead SOIC, 7" Tape and Reel of 1,000  | R-8            |          |

| AD8132ARM                     | −40°C to +125°C   | 8-Lead MSOP                             | RM-8           | НМА      |

| AD8132ARM-REEL                | −40°C to +125°C   | 8-Lead MSOP, 13" Tape and Reel of 3,000 | RM-8           | HMA      |

| AD8132ARM-REEL7               | −40°C to +125°C   | 8-Lead MSOP, 7" Tape and Reel of 1,000  | RM-8           | HMA      |

| AD8132ARMZ <sup>1</sup>       | −40°C to +125°C   | 8-Lead MSOP                             | RM-8           | HMA      |

| AD8132ARMZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead MSOP, 13" Tape and Reel of 3,000 | RM-8           | НМА      |

| AD8132ARMZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 8-Lead MSOP, 7" Tape and Reel of 1,000  | RM-8           | HMA      |

$<sup>^{1}</sup>$  Z = Pb-free part

**NOTES**

# NOTES

| AD8132 |  |  |

|--------|--|--|

|--------|--|--|

NOTES