TPS79301, TPS79318 TPS79325, TPS79328, TPS793285 TPS79330, TPS79333, TPS793475

SLVS348H-JULY 2001-REVISED OCTOBER 2004

# ULTRALOW-NOISE, HIGH PSRR, FAST RF 200-mA LOW-DROPOUT LINEAR REGULATORS IN NanoStar™ WAFER CHIP SCALE AND SOT23

#### **FEATURES**

- 200-mA RF Low-Dropout Regulator With Enable

- Available in 1.8-V, 2.5-V, 2.8-V, 2.85-V, 3-V, 3.3-V, 4.75-V, and Adjustable (1.22-V to 5.5-V)

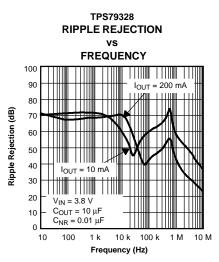

- High PSRR (70 dB at 10 kHz)

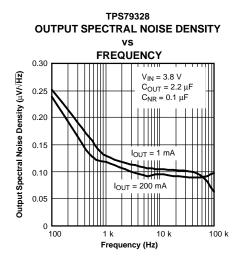

- Ultralow-Noise (32 μV<sub>RMS</sub>, TPS79328)

- Fast Start-Up Time (50 μs)

- Stable With a 2.2-µF Ceramic Capacitor

- Excellent Load/Line Transient Response

- Very Low Dropout Voltage (112 mV at Full Load, TPS79330)

- 5- and 6-Pin SOT23 (DBV) and NanoStar Wafer Chip Scale (YEQ) Packages

#### **APPLICATIONS**

- RF: VCOs, Receivers, ADCs

- Audio

- Cellular and Cordless Telephones

- Bluetooth™, Wireless LAN

- Handheld Organizers, PDAs

#### DESCRIPTION

TPS793xx family of low-dropout low-power linear voltage regulators features high power-supply rejection ratio (PSRR), ultralow-noise, fast start-up, and excellent line and load transient responses in NanoStar wafer chip scale and SOT23 packages. NanoStar packaging gives an ultrasmall footprint as well as an ultralow profile and package weight, making it ideal for portable applications such as handsets and PDAs. Each device in the family is stable, with a small 2.2-µF ceramic capacitor on the output. The TPS793xx family uses an advanced, proprietary BiCMOS fabrication process to yield extremely low dropout voltages (e.g., 112 mV at 200 mA, TPS79330). Each device achieves fast start-up times (approximately 50 µs with a 0.001-µF bypass capacitor) while consuming very low quiescent current (170 µA typical). Moreover, when the device is placed in standby mode, the supply current is reduced to less than 1 µA. The TPS79328 exhibits approximately 32 µV<sub>RMS</sub> of output voltage noise at 2.8-V output with a 0.1-µF bypass capacitor. Applicomponents cations with analog that noise-sensitive, such as portable RF electronics, benefit from the high PSRR and low-noise features as well as the fast response time.

Figure 1.

$\triangle$

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Bluetooth is a trademark of Bluetooth Sig, Inc. NanoStar is a trademark of Texas Instruments.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **AVAILABLE OPTIONS**(1)(2)

| PRODUCT   | VOLTAGE         | PACKAGE     | TJ              | SYMBOL | PART NUMBER   |               |

|-----------|-----------------|-------------|-----------------|--------|---------------|---------------|

| TPS79301  | 1.22 V to 5.5 V | SOT23 (DBV) |                 | PGVI   | TPS79301DBVR  |               |

| TPS79318  | 1.8 V           | SOT23 (DBV) |                 | PHHI   | TPS79318DBVR  |               |

| 173/9316  | 1.0 V           | CSP (YEQ)   |                 | E3     | TPS79318YEQ   |               |

| TPS79325  | 2.5 V           | SOT23 (DBV) |                 | PGWI   | TPS79325DBVR  |               |

| 17379325  | 2.5 V           | CSP (YEQ)   | -40°C to +125°C | E4     | TPS79325YEQ   |               |

| TPS79328  | 2.8 V           | SOT23 (DBV) |                 | PGXI   | TPS79328DBVR  |               |

| 17579326  |                 | CSP (YEQ)   |                 | E2     | TPS79328YEQ   |               |

| TPS793285 | 0.05.1/         | 2.85 V      | SOT23 (DBV)     |        | PHII          | TPS793285DBVR |

| 173/93203 | 2.00 V          | CSP (YEQ)   |                 | E5     | TPS793285YEQ  |               |

| TPS79330  | 2.1/            | SOT23 (DBV) |                 | PGYI   | TPS79330DBVR  |               |

| 17579330  | 3 V             | CSP (YEQ)   |                 | E6     | TPS79330YEQ   |               |

| TPS79333  | 3.3 V           | SOT23 (DBV) |                 | PHUI   | TPS79333DBVR  |               |

| TPS793475 | 4.75 V          | SOT23 (DBV) |                 | PHJI   | TPS793475DBVR |               |

- (1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

- (2) DBVR indicates tape and reel of 3000 parts. YEQR indicates tape and reel of 3000 parts. YEQT indicates tape and reel of 250 parts.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating temperature range (unless otherwise noted)(1)

|                                             | UNIT                              |

|---------------------------------------------|-----------------------------------|

| V <sub>IN</sub> range                       | -0.3 V to 6 V                     |

| V <sub>EN</sub> range                       | -0.3 V to V <sub>IN</sub> + 0.3 V |

| V <sub>OUT</sub> range                      | -0.3 V to 6 V                     |

| Peak output current                         | Internally limited                |

| ESD rating, HBM                             | 2 kV                              |

| ESD rating, CDM                             | 500 V                             |

| Continuous total power dissipation          | See Dissipation Ratings Table     |

| Junction temperature range, DBV package     | -40°C to 150°C                    |

| Junction temperature range, YEQ package     | -40°C to 125°C                    |

| Storage temperature range, T <sub>stg</sub> | -65°C to 150°C                    |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATINGS TABLE**

| BOARD                 | PACKAGE | $R_{	hetaJC}$ | $R_{	heta JA}$ | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> ≤ 25°C<br>POWER<br>RATING | T <sub>A</sub> = 70°C<br>POWER<br>RATING | T <sub>A</sub> = 85°C<br>POWER<br>RATING |

|-----------------------|---------|---------------|----------------|------------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| Low-K <sup>(1)</sup>  | DBV     | 65°C/W        | 255°C/W        | 3.9 mW/°C                                      | 390 mW                                   | 215 mW                                   | 155 mW                                   |

| High-K <sup>(2)</sup> | DBV     | 65°C/W        | 180°C/W        | 5.6 mW/°C                                      | 560 mW                                   | 310 mW                                   | 225 mW                                   |

| Low-K <sup>(1)</sup>  | YEQ     | 27°C/W        | 255°C/W        | 3.9 mW/°C                                      | 390 mW                                   | 215 mW                                   | 155 mW                                   |

| High-K <sup>(2)</sup> | YEQ     | 27°C/W        | 190°C/W        | 5.3 mW/°C                                      | 530 mW                                   | 296 mW                                   | 216 mW                                   |

<sup>(1)</sup> The JEDEC low-K (1s) board design used to derive this data was a 3-inch x 3-inch, two layer board with 2 ounce copper traces on top of the board.

#### **ELECTRICAL CHARACTERISTICS**

over recommended operating temperature range  $T_J$  = -40 to 125°C,  $V_{EN}$  =  $V_{IN}$ ,  $V_{IN}$  =  $V_{OUT(nom)}$  + 1  $V^{(1)}$ ,  $I_{OUT}$  = 1 mA,  $C_{OUT}$  = 10  $\mu$ F,  $C_{NR}$  = 0.01  $\mu$ F (unless otherwise noted). Typical values are at 25°C.

| PARAMETER                                                                          |           | TEST CONDITIONS                                        |                                                        | MIN             | TYP   | MAX                   | UNIT              |  |

|------------------------------------------------------------------------------------|-----------|--------------------------------------------------------|--------------------------------------------------------|-----------------|-------|-----------------------|-------------------|--|

| V <sub>IN</sub> Input voltage <sup>(1)</sup>                                       |           |                                                        |                                                        | 2.7             |       | 5.5                   | V                 |  |

| I <sub>OUT</sub> Continuous output curren                                          | t         |                                                        |                                                        | 0               |       | 200                   | mA                |  |

| V <sub>FB</sub> Internal reference (TPS79                                          | 301)      |                                                        |                                                        | 1.201           | 1.225 | 1.250                 | V                 |  |

| Output voltage range (TPS793                                                       | 301)      |                                                        |                                                        | V <sub>FB</sub> |       | 5.5 - V <sub>DO</sub> | V                 |  |

|                                                                                    | TPS79318  | $0 \mu A < I_{OUT} < 200 mA$ ,                         | $2.8 \text{ V} < \text{V}_{\text{IN}} < 5.5 \text{ V}$ | 1.764           | 1.8   | 1.836                 | V                 |  |

|                                                                                    | TPS79325  | $0 \mu A < I_{OUT} < 200 mA$ ,                         | $3.5 \text{ V} < \text{V}_{\text{IN}} < 5.5 \text{ V}$ | 2.45            | 2.5   | 2.55                  | V                 |  |

|                                                                                    | TPS79328  | 0 μA < I <sub>OUT</sub> < 200 mA,                      | 3.8 V < V <sub>IN</sub> < 5.5 V                        | 2.744           | 2.8   | 2.856                 | V                 |  |

| Output voltage                                                                     | TPS793285 | 0 μA < I <sub>OUT</sub> < 200 mA,                      | 3.85 V < V <sub>IN</sub> < 5.5 V                       | 2.793           | 2.85  | 2.907                 | V                 |  |

|                                                                                    | TPS79330  | 0 μA < I <sub>OUT</sub> < 200 mA,                      | 4 V < V <sub>IN</sub> < 5.5 V                          | 2.94            | 3     | 3.06                  | V                 |  |

|                                                                                    | TPS79333  | $0 \mu A \le I_{OUT} < 200 mA$ ,                       | $4.3 \text{ V} < \text{V}_{\text{IN}} < 5.5 \text{ V}$ | 3.234           | 3.3   | 3.366                 | V                 |  |

|                                                                                    | TPS793475 | $0 \mu A < I_{OUT} < 200 mA$ ,                         | 5.25 V < V <sub>IN</sub> < 5.5 V                       | 4.655           | 4.75  | 4.845                 | V                 |  |

| Line regulation (ΔV <sub>OUT</sub> %/ΔV <sub>IN</sub> )                            | (1)       | V <sub>OUT</sub> + 1 V < V <sub>IN</sub> ≤ 5.5 V       |                                                        |                 | 0.05  | 0.12                  | %/V               |  |

| Load regulation (ΔV <sub>OUT</sub> %/ΔI <sub>OL</sub>                              | IT)       | 0 μA < I <sub>OUT</sub> < 200 mA,                      | T <sub>J</sub> = 25°C                                  |                 | 5     |                       | mV                |  |

|                                                                                    | TPS79328  | I <sub>OUT</sub> = 200 mA                              |                                                        |                 | 120   | 200                   |                   |  |

| - (2)                                                                              | TPS793285 | I <sub>OUT</sub> = 200 mA                              |                                                        |                 | 120   | 200                   |                   |  |

| Dropout voltage <sup>(2)</sup><br>(V <sub>IN</sub> = V <sub>OUT(nom)</sub> - 0.1V) | TPS79330  | I <sub>OUT</sub> = 200 mA                              |                                                        |                 | 112   | 200                   | mV                |  |

| (VIN — VOUT(nom) OIIV)                                                             | TPS79333  | I <sub>OUT</sub> = 200 mA                              |                                                        |                 | 102   | 180                   | -                 |  |

|                                                                                    | TPS793475 | I <sub>OUT</sub> = 200 mA                              |                                                        |                 | 77    | 125                   |                   |  |

| Output current limit                                                               |           | V <sub>OUT</sub> = 0 V                                 |                                                        | 285             |       | 600                   | mA                |  |

| GND pin current                                                                    |           | 0 μA < I <sub>OUT</sub> < 200 mA                       |                                                        |                 | 170   | 220                   | μA                |  |

| Shutdown current <sup>(3)</sup>                                                    |           | V <sub>EN</sub> = 0 V, 2.7 V < V <sub>IN</sub> < 5.5 V |                                                        |                 | 0.07  | 1                     | μA                |  |

| FB pin current                                                                     |           | V <sub>FB</sub> = 1.8 V                                |                                                        |                 |       | 1                     | μA                |  |

|                                                                                    |           | f = 100 Hz, T <sub>J</sub> = 25°C,                     | $I_{OUT} = 10 \text{ mA}$                              |                 | 70    |                       |                   |  |

| Dower cumply ripple rejection                                                      | TPS79328  | $f = 100 \text{ Hz}, T_J = 25^{\circ}\text{C},$        | $I_{OUT} = 200 \text{ mA}$                             |                 | 68    |                       | dB                |  |

| Power-supply ripple rejection                                                      | 17379326  | $f = 10 \text{ kHz}, T_J = 25^{\circ}\text{C},$        | I <sub>OUT</sub> = 200 mA                              |                 | 70    |                       | uБ                |  |

|                                                                                    |           | $f = 100 \text{ kHz}, T_J = 25^{\circ}\text{C},$       | I <sub>OUT</sub> = 200 mA                              | 43              |       |                       |                   |  |

| Output paige valtage (TDS70220)                                                    |           |                                                        | C <sub>NR</sub> = 0.001 μF                             |                 | 55    |                       |                   |  |

|                                                                                    |           | BW = 200 Hz to 100 kHz,                                | $C_{NR} = 0.0047 \ \mu F$                              | 36              |       | /                     |                   |  |

| Output noise voltage (TPS793                                                       | 20)       | $I_{OUT} = 200 \text{ mA}$ $C_{NR} = 0.01 \mu\text{F}$ |                                                        |                 | 33    |                       | μV <sub>RMS</sub> |  |

|                                                                                    |           |                                                        | $C_{NR} = 0.1 \ \mu F$                                 |                 | 32    |                       |                   |  |

The JEDEC high-K (2s2p) board design used to derive this data was a 3-inch x 3-inch, multilayer board with 1 ounce internal power and ground planes and 2 ounce copper traces on top and bottom of the board.

<sup>(2)</sup>

Minimum  $V_{IN}$  is 2.7 V or  $V_{OUT}$  +  $V_{DO}$ , whichever is greater. Dropout is not measured for the TPS79318 and TPS79325 since minimum  $V_{IN}$  = 2.7 V. For adjustable versions, this applies only after  $V_{IN}$  is applied; then  $V_{EN}$  transitions high to low.

#### **ELECTRICAL CHARACTERISTICS (continued)**

over recommended operating temperature range  $T_J$  = -40 to 125°C,  $V_{EN}$  =  $V_{IN}$ ,  $V_{IN}$  =  $V_{OUT(nom)}$  + 1 V,  $I_{OUT}$  = 1 mA,  $C_{OUT}$  = 10  $\mu$ F,  $C_{NR}$  = 0.01  $\mu$ F (unless otherwise noted). Typical values are at 25°C.

| PARAMETER                       | TEST CONDITIONS                             |                                 |  | TYP        | MAX             | UNIT |  |

|---------------------------------|---------------------------------------------|---------------------------------|--|------------|-----------------|------|--|

|                                 |                                             | C <sub>NR</sub> = 0.001 µF      |  | 50         |                 |      |  |

| Time, start-up (TPS79328)       | $R_L$ = 14 $\Omega$ , $C_{OUT}$ = 1 $\mu F$ | $C_{NR} = 0.0047 \ \mu F$       |  | 70         |                 | μs   |  |

|                                 |                                             | $C_{NR} = 0.01 \ \mu F$         |  | 100        |                 |      |  |

| High level enable input voltage | 2.7 V < V <sub>IN</sub> < 5.5 V             | 2.7 V < V <sub>IN</sub> < 5.5 V |  |            | V <sub>IN</sub> | V    |  |

| Low level enable input voltage  | 2.7 V < V <sub>IN</sub> < 5.5 V             | 2.7 V < V <sub>IN</sub> < 5.5 V |  |            | 0.7             | V    |  |

| EN pin current                  | V <sub>EN</sub> = 0                         |                                 |  |            | 1               | μΑ   |  |

| UVLO threshold                  | V <sub>CC</sub> rising                      |                                 |  | <u>!</u> 5 | 2.65            | V    |  |

| UVLO hysteresis                 |                                             |                                 |  | 100        | )               | mV   |  |

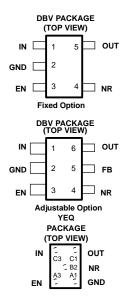

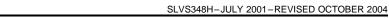

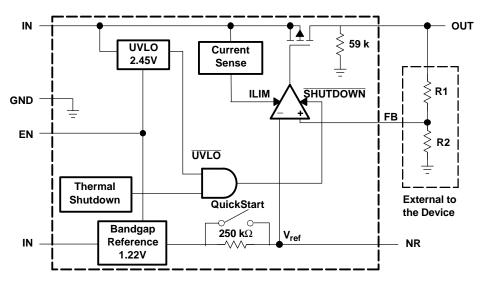

#### **FUNCTIONAL BLOCK DIAGRAMS**

#### **ADJUSTABLE VERSION**

#### **FIXED VERSION**

#### **Terminal Functions**

| TERMINAL |              |                |               |                                                                                                                                                               |  |  |  |

|----------|--------------|----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | SOT23<br>ADJ | SOT23<br>FIXED | WCSP<br>FIXED | DESCRIPTION                                                                                                                                                   |  |  |  |

| NR       | 4            | 4              | B2            | Connecting an external capacitor to this pin bypasses noise generated by the internal bandgap. This improves power-supply rejection and reduces output noise. |  |  |  |

| EN       | 3            | 3              | А3            | Driving the enable pin (EN) high turns on the regulator. Driving this pin low puts the regulator into shutdown mode. EN can be connected to IN if not used.   |  |  |  |

| FB       | 5            | N/A            | N/A           | This terminal is the feedback input voltage for the adjustable device.                                                                                        |  |  |  |

| GND      | 2            | 2              | A1            | Regulator ground                                                                                                                                              |  |  |  |

| IN       | 1            | 1              | C3            | Unregulated input to the device.                                                                                                                              |  |  |  |

| OUT      | 6            | 5              | C1            | Output of the regulator.                                                                                                                                      |  |  |  |

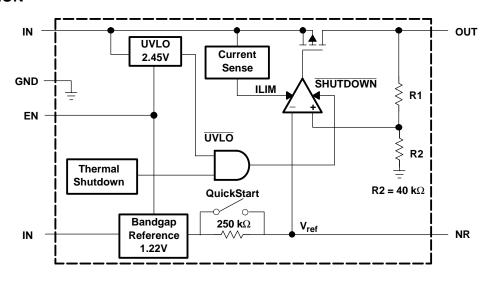

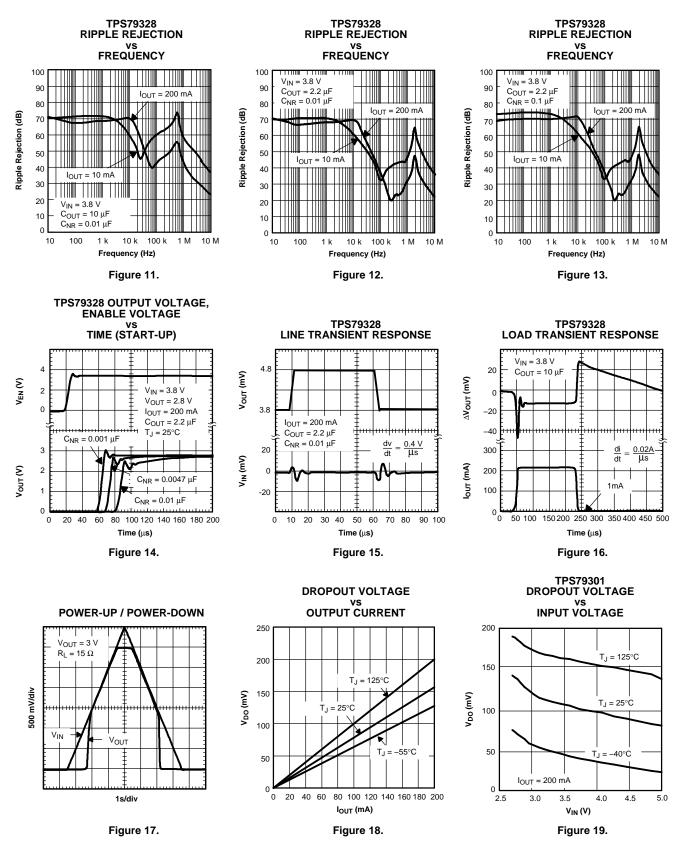

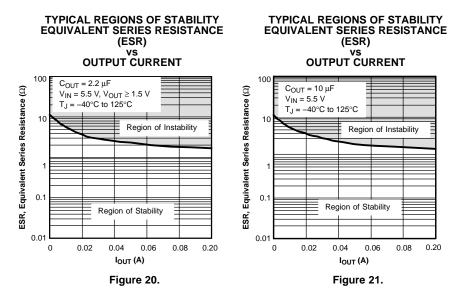

#### **TYPICAL CHARACTERISTICS (SOT23 PACKAGE)**

#### TYPICAL CHARACTERISTICS (SOT23 PACKAGE) (continued)

#### TYPICAL CHARACTERISTICS (SOT23 PACKAGE) (continued)

SLVS348H-JULY 2001-REVISED OCTOBER 2004

TEXAS INSTRUMENTS

The TPS793xx family of low-dropout (LDO) regulators has been optimized for use in noise-sensitive battery-operated equipment. The device features extremely low dropout voltages, high PSRR, ultralow output noise, low quiescent current (170  $\mu$ A typically), and enable-input to reduce supply currents to less than 1  $\mu$ A when the regulator is turned off.

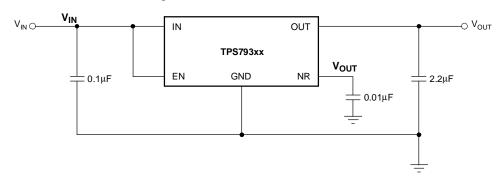

A typical application circuit is shown in Figure 22.

Figure 22. Typical Application Circuit

#### **External Capacitor Requirements**

A 0.1-µF or larger ceramic input bypass capacitor, connected between IN and GND and located close to the TPS793xx, is required for stability and improves transient response, noise rejection, and ripple rejection. A higher-value input capacitor may be necessary if large, fast-rise-time load transients are anticipated or the device is located several inches from the power source.

Like most low dropout regulators, the TPS793xx requires an output capacitor connected between OUT and GND to stabilize the internal control loop. The minimum recommended capacitance is 2.2 μF. Any 2.2-μF or larger ceramic capacitor is suitable, provided the capacitance does not vary significantly over temperature. If load current is not expected to exceed 100 mA, a 1.0-μF ceramic capacitor can be used.

The internal voltage reference is a key source of noise in an LDO regulator. The TPS793xx has an NR pin which is connected to the voltage reference through a 250-k $\Omega$  internal resistor. The 250-k $\Omega$  internal resistor, in conjunction with an external bypass capacitor connected to the NR pin, creates a low pass filter to reduce the voltage reference noise and, therefore, the noise at the regulator output. In order for the regulator to operate properly, the current flow out of the NR pin must be at a minimum, because any leakage current creates an IR drop across the internal resistor thus creating an output error. Therefore, the bypass capacitor must have minimal leakage current. The bypass capacitor should be no more than 0.1- $\mu$ F to ensure that it is fully charged during the quickstart time provided by the internal switch shown in the Functional Block Diagrams

As an example, the TPS79328 exhibits only 32  $\mu V_{RMS}$  of output voltage noise using a 0.1- $\mu F$  ceramic bypass capacitor and a 2.2- $\mu F$  ceramic output capacitor. Note that the output starts up slower as the bypass capacitance increases due to the RC time constant at the NR pin that is created by the internal 250- $k\Omega$  resistor and external capacitor.

#### **Board Layout Recommendation to Improve PSRR and Noise Performance**

To improve ac measurements like PSRR, output noise, and transient response, it is recommended that the board be designed with separate ground planes for  $V_{\text{IN}}$  and  $V_{\text{OUT}}$ , with each ground plane connected only at the GND pin of the device. In addition, the ground connection for the bypass capacitor should connect directly to the GND pin of the device.

#### **APPLICATION INFORMATION (continued)**

#### **Power Dissipation and Junction Temperature**

Specified regulator operation is assured to a junction temperature of  $125^{\circ}$ C; the maximum junction temperature should be restricted to  $125^{\circ}$ C under normal operating conditions. This restriction limits the power dissipation the regulator can handle in any given application. To ensure the junction temperature is within acceptable limits, calculate the maximum allowable dissipation,  $P_{D(max)}$ , and the actual dissipation,  $P_D$ , which must be less than or equal to  $P_{D(max)}$ .

The maximum power dissipation limit is determined using Equation 1:

$$P_{D(max)} = \frac{T_{J} max - T_{A}}{R_{\Theta JA}}$$

(1)

Where:

- T<sub>J</sub>max is the maximum allowable junction temperature.

- R<sub>θJA</sub> is the thermal resistance junction-to-ambient for the package (see the Dissipation Ratings Table).

- T<sub>A</sub> is the ambient temperature.

The regulator dissipation is calculated using Equation 2:

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT}$$

(2)

Power dissipation resulting from quiescent current is negligible. Excessive power dissipation triggers the thermal protection circuit.

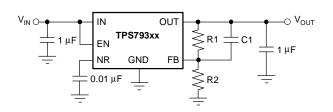

#### Programming the TPS79301 Adjustable LDO Regulator

The output voltage of the TPS79301 adjustable regulator is programmed using an external resistor divider as shown in Figure 23. The output voltage is calculated using Equation 3:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_1}{R_2}\right) \tag{3}$$

Where:

• V<sub>REF</sub> = 1.2246 V typ (the internal reference voltage)

Resistors R1 and R2 should be chosen for approximately 50- $\mu$ A divider current. Lower value resistors can be used for improved noise performance, but the solution consumes more power. Higher resistor values should be avoided as leakage current into/out of FB across R1/R2 creates an offset voltage that artificially increases/decreases the feedback voltage and thus erroneously decreases/increases  $V_{OUT}$ . The recommended design procedure is to choose R2 = 30.1 k $\Omega$  to set the divider current at 50  $\mu$ A, C1 = 15 pF for stability, and then calculate R1 using Equation 4:

$$R_1 = \left(\frac{V_{\text{OUT}}}{V_{\text{ref}} - 1}\right) \times R_2 \tag{4}$$

In order to improve the stability of the adjustable version, it is suggested that a small compensation capacitor be placed between OUT and FB. For voltages <1.8 V, the value of this capacitor should be 100 pF. For voltages >1.8 V, the approximate value of this capacitor can be calculated as shown in Equation 5:

$$C_1 = \frac{(3 \times 10^{-7}) \times (R_1 + R_2)}{(R_1 \times R_2)}$$

(5)

The suggested value of this capacitor for several resistor ratios is shown in the table below. If this capacitor is not used (such as in a unity-gain configuration) or if an output voltage <1.8 V is chosen, then the minimum recommended output capacitor is 4.7  $\mu$ F instead of 2.2  $\mu$ F.

SLVS348H-JULY 2001-REVISED OCTOBER 2004

#### **APPLICATION INFORMATION (continued)**

# OUTPUT VOLTAGE PROGRAMMING GUIDE

| OUTPUT<br>VOLTAGE | R1       | R2      | C1    |

|-------------------|----------|---------|-------|

| 1.22 V            | short    | open    | 0 pF  |

| 2.5 V             | 31.6 k Ω | 30.1 kΩ | 22 pF |

| 3.3 V             | 51 kΩ    | 30.1 kΩ | 15 pF |

| 3.6 V             | 59 kΩ    | 30.1 kΩ | 15 pF |

Figure 23. TPS79301 Adjustable LDO Regulator Programming

#### **Regulator Protection**

The TPS793xx PMOS-pass transistor has a built-in back diode that conducts reverse current when the input voltage drops below the output voltage (e.g., during power-down). Current is conducted from the output to the input and is not internally limited. If extended reverse voltage operation is anticipated, external limiting might be appropriate.

The TPS793xx features internal current limiting and thermal protection. During normal operation, the TPS793xx limits output current to approximately 400 mA. When current limiting engages, the output voltage scales back linearly until the overcurrent condition ends. While current limiting is designed to prevent gross device failure, care should be taken not to exceed the power dissipation ratings of the package or the absolute maximum voltage ratings of the device. If the temperature of the device exceeds approximately 165°C, thermal-protection circuitry shuts it down. Once the device has cooled down to below approximately 140°C, regulator operation resumes.

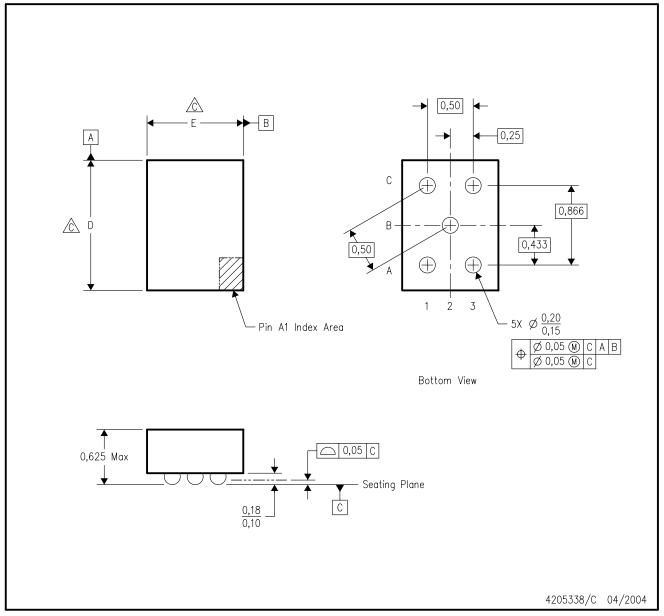

#### TPS793xxYEQ NanoStar™ Wafer Chip Scale Information

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. NanoStar™ package configuration.

- D. This package is tin-lead (SnPb); consult the factory for availability of lead-free material.

NanoStar is a trademark of Texas Instruments.

Figure 24. NanoStar™ Wafer Chip Scale Package

13-Oct-2004

#### **PACKAGING INFORMATION**

| ORDERABLE DEVICE | STATUS(1) | PACKAGE TYPE | PACKAGE DRAWING | PINS | PACKAGE QTY |

|------------------|-----------|--------------|-----------------|------|-------------|

| TPS79301DBVR     | ACTIVE    | SOP          | DBV             | 6    | 3000        |

| TPS79318DBVR     | ACTIVE    | SOP          | DBV             | 5    | 3000        |

| TPS79318DBVT     | ACTIVE    | SOP          | DBV             | 5    | 250         |

| TPS79318YEQR     | ACTIVE    | DSBGA        | YEQ             | 5    | 3000        |

| TPS79318YEQT     | ACTIVE    | DSBGA        | YEQ             | 5    | 250         |

| TPS79325DBVR     | ACTIVE    | SOP          | DBV             | 5    | 3000        |

| TPS79325YEQR     | ACTIVE    | DSBGA        | YEQ             | 5    | 3000        |

| TPS79325YEQT     | ACTIVE    | DSBGA        | YEQ             | 5    | 250         |

| TPS793285DBVR    | ACTIVE    | SOP          | DBV             | 5    | 3000        |

| TPS793285DBVT    | ACTIVE    | SOP          | DBV             | 5    | 250         |

| TPS793285YEQR    | ACTIVE    | DSBGA        | YEQ             | 5    | 3000        |

| TPS793285YEQT    | ACTIVE    | DSBGA        | YEQ             | 5    | 250         |

| TPS79328DBVR     | ACTIVE    | SOP          | DBV             | 5    | 3000        |

| TPS79328YEQR     | ACTIVE    | DSBGA        | YEQ             | 5    | 3000        |

| TPS79328YEQT     | ACTIVE    | DSBGA        | YEQ             | 5    | 250         |

| TPS79330DBVR     | ACTIVE    | SOP          | DBV             | 5    | 3000        |

| TPS79330YEQR     | ACTIVE    | DSBGA        | YEQ             | 5    | 3000        |

| TPS79330YEQT     | ACTIVE    | DSBGA        | YEQ             | 5    | 250         |

| TPS79333DBVR     | ACTIVE    | SOP          | DBV             | 5    | 3000        |

| TPS793475DBVR    | ACTIVE    | SOP          | DBV             | 5    | 3000        |

(1) The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available. **OBSOLETE:** TI has discontinued the production of the device.

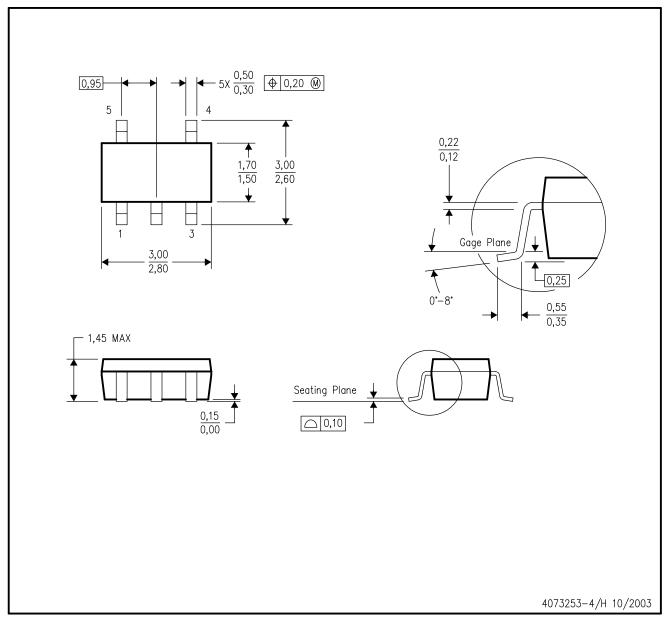

# DBV (R-PDSO-G5)

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- C. Body dimensions do not include mold fla D. Falls within JEDEC MO—178 Variation AA. Body dimensions do not include mold flash or protrusion.

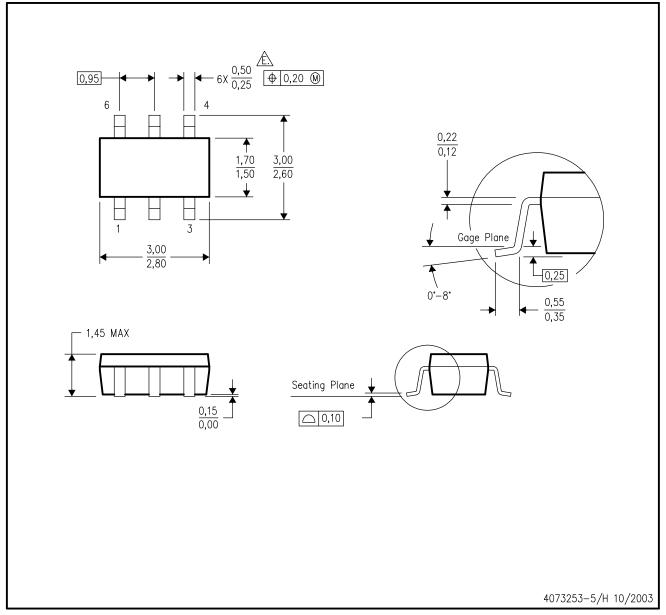

# DBV (R-PDSO-G6)

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation.

- Falls within JEDEC MO-178 Variation AB, except minimum lead width.

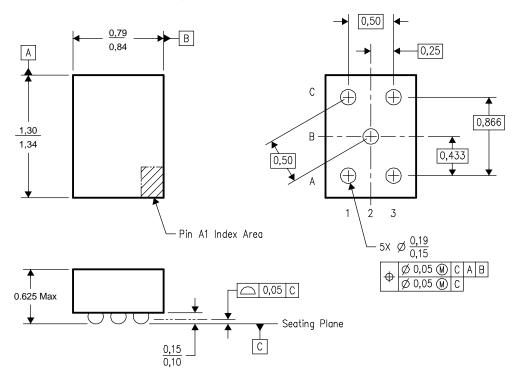

## YEQ (R-XBGA-N5)

### DIE-SIZE BALL GRID ARRAY

Notes:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Devices in this YEQ package can have dimension D ranging from 1.17 to 1.67 and dimension E ranging from 0.80 to 1.30.

To determine the exact package size of a particular device, refer to the device datasheet or contact a local TI representative.

- D. NanoStar  $\mathbf{M}$  package configuration.

- E. This package contains tin-lead (SnPb) balls. Refer to the 5 YZQ package (drawing 4205677) for lead-free balls.

NanoStar is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated