# **DUAL FULL-BRIDGE DRIVER**

- OPERATING SUPPLY VOLTAGE UP TO 46 V

- TOTAL DC CURRENT UP TD) 4 A

- LOW SATURATION VOLTA

- OVERTEMPERATURE PROTECTION

- LOGICAL "0" INPUT VOLT GE UP TO 1.5 V (HIGH NOISE IMMUNITY)

### **DESCRIPTION**

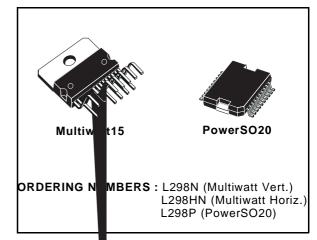

The L298 is an integrated mond thic circuit in a 15-lead Multiwatt and PowerSO2 packages. It is a high voltage, high current dual teleprise levels and drive inductive loads such as relays, solenoids, DC and stepping motors. Two enable in uts are provided to enable or disable the device independently of the input signals. The emitters of the ower transistors of each bridge are connected together and the corresponding external terminal can be used for the con-

nection of an external sensing resistor. An additional supply input is provided so that the logic works at a lower voltage.

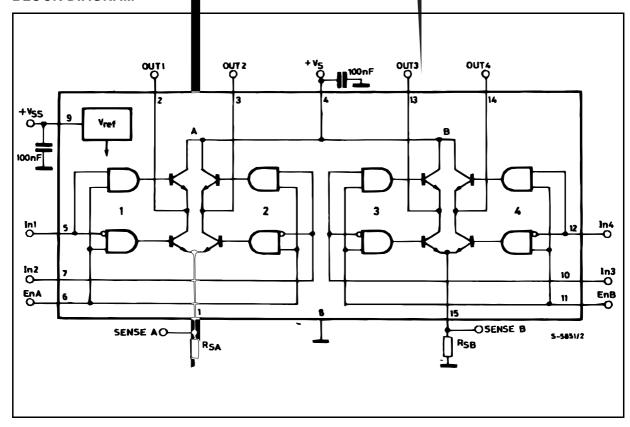

#### **BLOCK DIAGRAM**

Jenuary 2000 1/13

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                          | Parameter                                                                                                                  | Value         | Unit        |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------|-------------|

| Vs                              | Power Supply                                                                                                               | 50            | V           |

| $V_{SS}$                        | Logic Supply Voltage                                                                                                       | 7             | V           |

| V <sub>I</sub> ,V <sub>en</sub> | Input and Enable Voltage                                                                                                   | -0.3 to 7     | V           |

| Ю                               | Peak Output Current (each Channel)  – Non Repetitive (t = 100μs)  –Repetitive (80% on –20% off; ton = 10ms)  –DC Operation | 3<br>2.5<br>2 | A<br>A<br>A |

| V <sub>sens</sub>               | Sensing Voltage                                                                                                            | -1 to 2.3     | V           |

| P <sub>tot</sub>                | Total Power Dissipation (T <sub>case</sub> = 75°C)                                                                         | 25            | W           |

| T <sub>op</sub>                 | Junction Operating Temperature                                                                                             | -25 to 130    | °C          |

| $T_{stg}$ , $T_j$               | Storage and Junction Temperature                                                                                           | -40 to 150    | °C          |

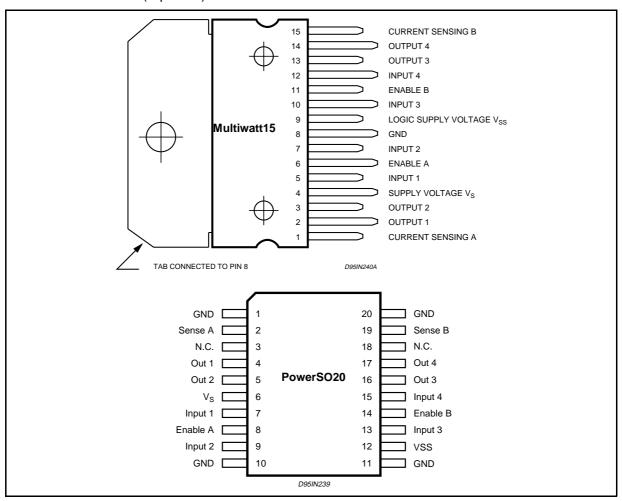

## PIN CONNECTIONS (top view)

### **THERMAL DATA**

| Symbol                 | Parameter                           |      | PowerSO20 | Multiwatt15 | Unit |

|------------------------|-------------------------------------|------|-----------|-------------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case    | Max. | _         | 3           | °C/W |

| R <sub>th j-amb</sub>  | Thermal Resistance Junction-ambient | Max. | 13 (*)    | 35          | °C/W |

<sup>(\*)</sup> Mounted on aluminum substrate

## **PIN FUNCTIONS** (refer to the block diagram)

| MW.15  | PowerSO    | Name               | Function                                                                                                                   |

|--------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1;15   | 2;19       | Sense A; Sense B   | Between this pin and ground is connected the sense resistor to control the current of the load.                            |

| 2;3    | 4;5        | Out 1; Out 2       | Outputs of the Bridge A; the current that flows through the load connected between these two pins is monitored at pin 1.   |

| 4      | 6          | Vs                 | Supply Voltage for the Power Output Stages. A non-inductive 100nF capacitor must be connected between this pin and ground. |

| 5;7    | 7;9        | Input 1; Input 2   | TTL Compatible Inputs of the Bridge A.                                                                                     |

| 6;11   | 8;14       | Enable A; Enable B | TTL Compatible Enable Input: the L state disables the bridge A (enable A) and/or the bridge B (enable B).                  |

| 8      | 1,10,11,20 | GND                | Ground.                                                                                                                    |

| 9      | 12         | VSS                | Supply Voltage for the Logic Blocks. A100nF capacitor must be connected between this pin and ground.                       |

| 10; 12 | 13;15      | Input 3; Input 4   | TTL Compatible Inputs of the Bridge B.                                                                                     |

| 13; 14 | 16;17      | Out 3; Out 4       | Outputs of the Bridge B. The current that flows through the load connected between these two pins is monitored at pin 15.  |

| _      | 3;18       | N.C.               | Not Connected                                                                                                              |

# **ELECTRICAL CHARACTERISTICS** ( $V_S = 42V$ ; $V_{SS} = 5V$ , $T_j = 25^{\circ}C$ ; unless otherwise specified)

| Symbol                 | Parameter                                      | Test Conditions                                    |                        | Min.                 | Тур.       | Max.            | Unit     |

|------------------------|------------------------------------------------|----------------------------------------------------|------------------------|----------------------|------------|-----------------|----------|

| Vs                     | Supply Voltage (pin 4)                         | Operative Condition                                |                        | V <sub>IH</sub> +2.5 |            | 46              | V        |

| $V_{SS}$               | Logic Supply Voltage (pin 9)                   |                                                    |                        | 4.5                  | 5          | 7               | V        |

| Is                     | Quiescent Supply Current (pin 4)               | $V_{en} = H; I_L = 0$                              | $V_i = L$<br>$V_i = H$ |                      | 13<br>50   | 22<br>70        | mA<br>mA |

|                        |                                                | $V_{en} = L$                                       | $V_i = X$              |                      |            | 4               | mA       |

| I <sub>SS</sub>        | Quiescent Current from V <sub>SS</sub> (pin 9) | $V_{en} = H; I_L = 0$                              | $V_i = L$<br>$V_i = H$ |                      | 24<br>7    | 36<br>12        | mA<br>mA |

|                        |                                                | $V_{en} = L$                                       | $V_i = X$              |                      |            | 6               | mA       |

| $V_{iL}$               | Input Low Voltage (pins 5, 7, 10, 12)          |                                                    |                        | -0.3                 |            | 1.5             | V        |

| V <sub>iH</sub>        | Input High Voltage (pins 5, 7, 10, 12)         |                                                    |                        | 2.3                  |            | VSS             | V        |

| l <sub>iL</sub>        | Low Voltage Input Current (pins 5, 7, 10, 12)  | $V_i = L$                                          |                        |                      |            | -10             | μΑ       |

| I <sub>iH</sub>        | High Voltage Input Current (pins 5, 7, 10, 12) | $Vi = H \le V_{SS} -0.6V$                          |                        |                      | 30         | 100             | μΑ       |

| V <sub>en</sub> = L    | Enable Low Voltage (pins 6, 11)                |                                                    |                        | -0.3                 |            | 1.5             | V        |

| V <sub>en</sub> = H    | Enable High Voltage (pins 6, 11)               |                                                    |                        | 2.3                  |            | V <sub>SS</sub> | V        |

| I <sub>en</sub> = L    | Low Voltage Enable Current (pins 6, 11)        | V <sub>en</sub> = L                                |                        |                      |            | -10             | μΑ       |

| I <sub>en</sub> = H    | High Voltage Enable Current (pins 6, 11)       | $V_{en} = H \le V_{SS} - 0.6V$                     |                        |                      | 30         | 100             | μΑ       |

| V <sub>CEsat (H)</sub> | Source Saturation Voltage                      | I <sub>L</sub> = 1A<br>I <sub>L</sub> = 2A         |                        | 0.95                 | 1.35<br>2  | 1.7<br>2.7      | V<br>V   |

| V <sub>CEsat (L)</sub> | Sink Saturation Voltage                        | I <sub>L</sub> = 1A (5)<br>I <sub>L</sub> = 2A (5) |                        | 0.85                 | 1.2<br>1.7 | 1.6<br>2.3      | V<br>V   |

| V <sub>CEsat</sub>     | Total Drop                                     | I <sub>L</sub> = 1A (5)<br>I <sub>L</sub> = 2A (5) |                        | 1.80                 |            | 3.2<br>4.9      | V<br>V   |

| V <sub>sens</sub>      | Sensing Voltage (pins 1, 15)                   |                                                    |                        | -1 (1)               |            | 2               | V        |

Figure 1 : Typical Saturation Voltage vs. Output Current.

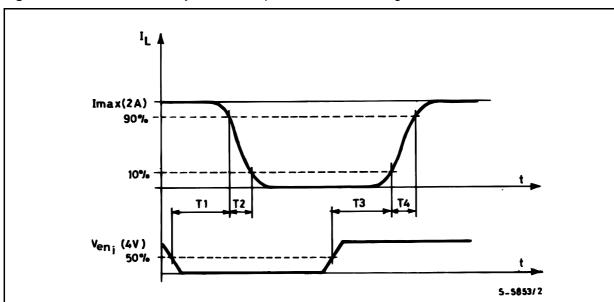

Figure 3: Source Current Delay Times vs. Input or Enable Switching.

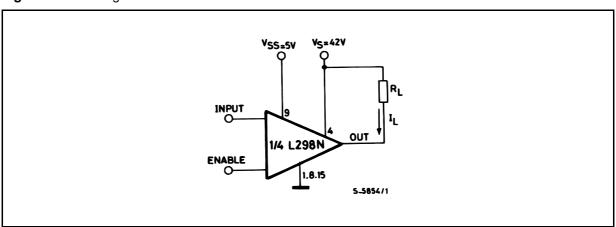

Figure 4 : Switching Times Test Circuits.

Note: For INPUT Switching, set EN = H For ENABLE Switching, set IN = L

Figure 5 : Sink Current Delay Times vs. Input 0 V Enable Switching.

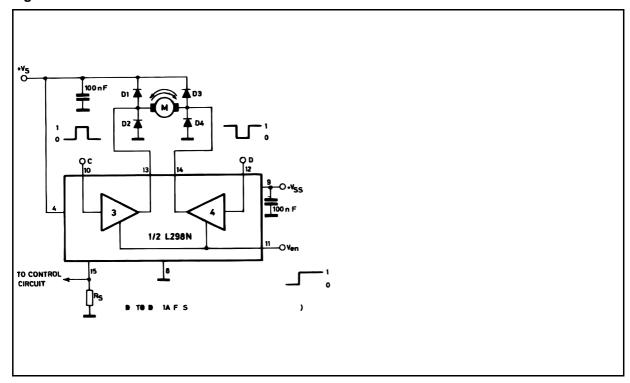

Figure 6 : Bidirectional DC Motor Control.

**Figure 7 :** For higher currents, outputs can be paralleled. Take care to parallel channel 1 with channel 4 and channel 2 with channel 3.

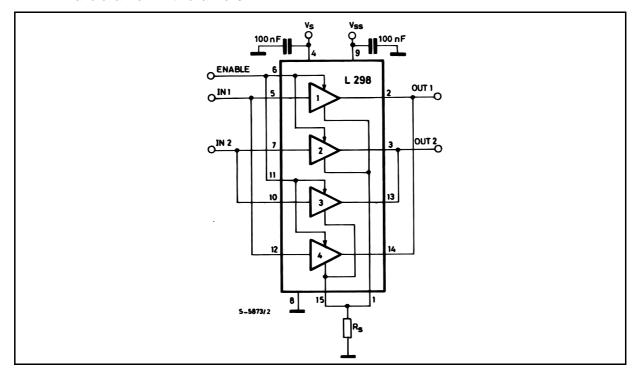

### **APPLICATION INFORMATION (Refer to the block diagram)**

### 1.1. POWER OUTPUT STAGE

The L298 integrates two power output stages (A; B). The power output stage is a bridge configuration and its outputs can drive an inductive load in common or differenzial mode, depending on the state of the inputs. The current that flows through the load comes out from the bridge at the sense output: an external resistor ( $R_{SA}$ ;  $R_{SB}$ .) allows to detect the intensity of this current.

### 1.2. INPUT STAGE

Each bridge is driven by means of four gates the input of which are In1; In2; EnA and In3; In4; EnB. The In inputs set the bridge state when The En input is high; a low state of the En input inhibits the bridge. All the inputs are TTL compatible.

### 2. SUGGESTIONS

A non inductive capacitor, usually of 100 nF, must be foreseen between both Vs and Vss, to ground, as near as possible to GND pin. When the large capacitor of the power supply is too far from the IC, a second smaller one must be foreseen near the L298.

The sense resistor, not of a wire wound type, must be grounded near the negative pole of Vs that must be near the GND pin of the I.C.

Each input must be connected to the source of the driving signals by means of a very short path.

Turn-On and Turn-Off: Before to Turn-ON the Supply Voltage and before to Turn it OFF, the Enable input must be driven to the Low state.

#### 3. APPLICATIONS

Fig 6 shows a bidirectional DC motor control Schematic Diagram for which only one bridge is needed. The external bridge of diodes D1 to D4 is made by four fast recovery elements (trr  $\leq$  200 nsec) that must be chosen of a VF as low as possible at the worst case of the load current.

The sense output voltage can be used to control the current amplitude by chopping the inputs, or to provide overcurrent protection by switching low the enable input.

The brake function (Fast motor stop) requires that the Absolute Maximum Rating of 2 Amps must never be overcome.

When the repetitive peak current needed from the load is higher than 2 Amps, a paralleled configuration can be chosen (See Fig.7).

An external bridge of diodes are required when inductive loads are driven and when the inputs of the IC are chopped; Shottky diodes would be preferred.

This solution can drive until 3 Amps In DC operation and until 3.5 Amps of a repetitive peak current.

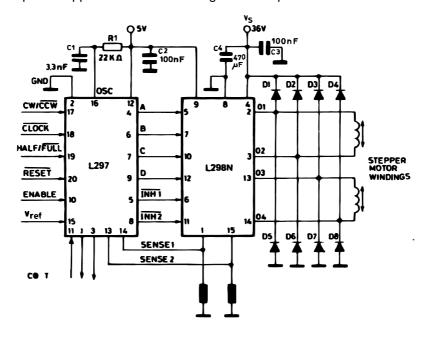

On Fig 8 it is shown the driving of a two phase bipolar stepper motor; the needed signals to drive the inputs of the L298 are generated, in this example, from the IC L297.

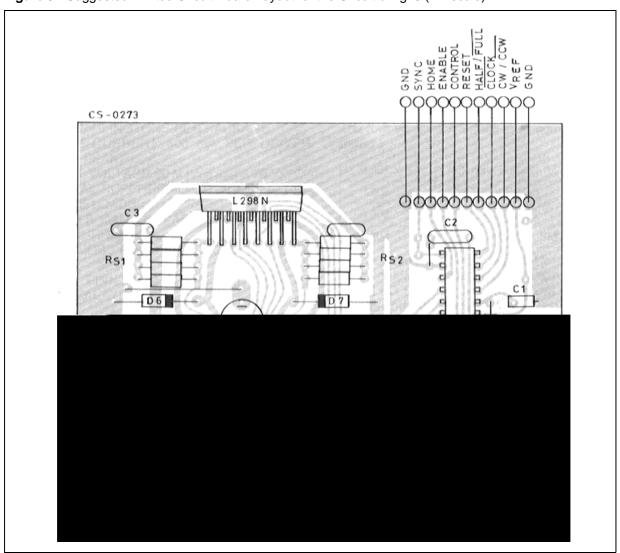

Fig 9 shows an example of P.C.B. designed for the application of Fig 8.

Figure 8: Two Phase Bipolar Stepper Motor Circuit.

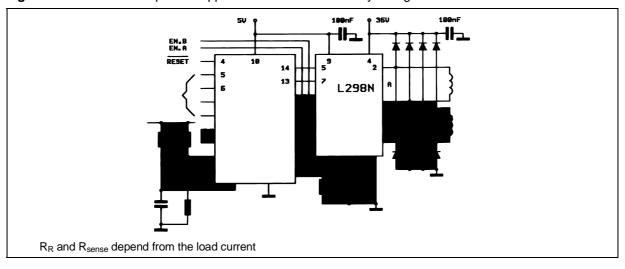

Fig 10 shows a second two phase bipolar stepper motor control circuit where the current is controlled by the I.C. L6506.

This circuit drives bipolar stepper motors with winding currents up to 2 A. The diodes are fast 2 A types.

Figure 9: Suggested Printed Circuit Board Layout for the Circuit of fig. 8 (1:1 scale).

Figure 10: Two Phase Bipolar Stepper Motor Control Circuit by Using the Current Controller L6506.

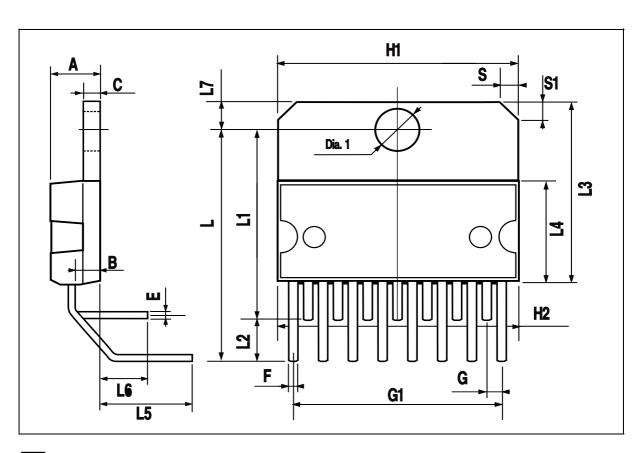

| DIM.   | mm    |       |       | inch  |       |       |  |

|--------|-------|-------|-------|-------|-------|-------|--|

| DIIVI. | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |  |

| Α      |       |       | 5     |       |       | 0.197 |  |

| В      |       |       | 2.65  |       |       | 0.104 |  |

| С      |       |       | 1.6   |       |       | 0.063 |  |

| Е      | 0.49  |       | 0.55  | 0.019 |       | 0.022 |  |

| F      | 0.66  |       | 0.75  | 0.026 |       | 0.030 |  |

| G      | 1.14  | 1.27  | 1.4   | 0.045 | 0.050 | 0.055 |  |

| G1     | 17.57 | 17.78 | 17.91 | 0.692 | 0.700 | 0.705 |  |

| H1     | 19.6  |       |       | 0.772 |       |       |  |

| H2     |       |       | 20.2  |       |       | 0.795 |  |

| L      |       | 20.57 |       |       | 0.810 |       |  |

| L1     |       | 18.03 |       |       | 0.710 |       |  |

| L2     |       | 2.54  |       |       | 0.100 |       |  |

| L3     | 17.25 | 17.5  | 17.75 | 0.679 | 0.689 | 0.699 |  |

| L4     | 10.3  | 10.7  | 10.9  | 0.406 | 0.421 | 0.429 |  |

| L5     |       | 5.28  |       |       | 0.208 |       |  |

| L6     |       | 2.38  |       |       | 0.094 |       |  |

| L7     | 2.65  |       | 2.9   | 0.104 |       | 0.114 |  |

| S      | 1.9   |       | 2.6   | 0.075 |       | 0.102 |  |

| S1     | 1.9   |       | 2.6   | 0.075 |       | 0.102 |  |

| Dia1   | 3.65  |       | 3.85  | 0.144 |       | 0.152 |  |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2000 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com