## LMH6678 Low Power 2-Channel Central-Office xDSL Driver **General Description**

The LMH6678 is a low power 2-channel differential output driver utilizing dual current feedback op amps with a fixed gain of  $A_V = +5.4$ .

The LMH6678 utilizes high integration with low power consumption to provide 580 mW at 19.8 dBm line output. The LMH6678 can also be put into a listen mode to maintain the termination for receive signals with 100 mW/Ch power dissipation.

The LMH6678 has two separate 2-bit power control inputs compatible with 3.3V CMOS for each channel that enable independent control of line status. When the drivers for both channels are shut off, power consumption drops to only 6 mW.

Thermal Shutdown function protects the IC from a shorted line fault or system over temperature.

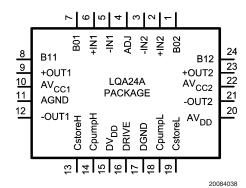

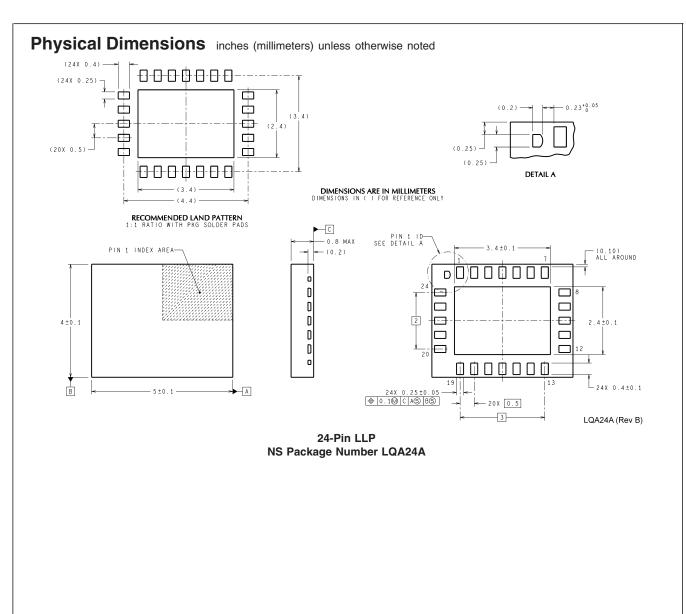

The LMH6678 is available in a 5mm x 4mm 24-lead LLP package.

### **Features**

$AV_{CC1} = AV_{CC2} = +12V, AV_{DD} = DV_{DD} = +3.3V, T_A = 25^{\circ}C,$ 2/3 Power Mode, Typical values unless specified.

Low power consumption

| — Line power P <sub>LINE</sub> = 100 mW           | 580 mW/Ch                 |

|---------------------------------------------------|---------------------------|

| — No signal                                       | 185 mW/Ch                 |

| — Listen mode                                     | 100 mW/Ch                 |

| <ul> <li>— Shutdown mode</li> </ul>               | 3 mW/Ch                   |

| Power Supply                                      |                           |

| — Analog (AV <sub>CC1</sub> , AV <sub>CC2</sub> ) | +12V                      |

| — Digital (DV <sub>DD</sub> , AV <sub>DD</sub> )  | +3.3V                     |

| ■ Output voltage swing @ R <sub>L</sub> = 31Ω     |                           |

| — Single ended                                    | 11.5 V <sub>PP</sub>      |

| — Differential                                    | 23 V <sub>PP</sub>        |

| Multi tone power ratio, f = 500 kHz               | 72 dB                     |

| Output current                                    | 580 mA                    |

| Thermal shutdown protection                       |                           |

| 5mm x 4mm LLP package                             |                           |

| Low thermal resistance                            | 36°C/W (θ <sub>JA</sub> ) |

| Small PCB footprint                               |                           |

### Application

- Full rate ADSL, ADSL+, ADSL++ or G. Lite linecard

- Remote DSLAMs

+12V / +3.3V

N:1

DAC2-

OUT TELEPHONE LINE TELEPHONE LINE CHARGE PUMP +12\ 20084037

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance                     |                               |

|-----------------------------------|-------------------------------|

| Human Body Model                  | 2KV (Note 2)                  |

| Machine Model                     | 200V (Note 8)                 |

| V <sub>IN</sub> Differential      | ±3V                           |

| Supply Voltages                   |                               |

| $AV_{CC1} - AGND$ or $AV_{CC2}$ - |                               |

| AGND                              | +13.2V                        |

| DV <sub>DD</sub> – DGND           | +3.6V                         |

| AV <sub>DD</sub> – AGND           | +3.6V                         |

| DGND – AGND                       | ±0.2V                         |

| $AV_{CC1} - AV_{CC2}$             | ±0.2V                         |

| $AV_{DD} - DV_{DD}$               | ±0.2V                         |

| Voltage at Input Pin              |                               |

| Analog Input                      | $AV_{CC1} (AV_{CC2}) + 0.8V,$ |

|                                   | AGND -0.8V                    |

| Digital Control Input            | DV <sub>DD</sub> +0.8V, |

|----------------------------------|-------------------------|

|                                  | DGND -0.8V              |

| Soldering Information            |                         |

| Infrared or Convection (20 sec.) | 235°C                   |

| Storage Temperature Range        | –65°C to +150°C         |

| Junction Temperature (Note 4)    | +150°C                  |

### Operating Ratings (Note 1)

| Supply Voltage                             |                |

|--------------------------------------------|----------------|

| AV <sub>CC1</sub> to AGND                  | +12V ±10%      |

| AV <sub>CC2</sub> to AGND                  | +12V ±10%      |

| DV <sub>DD</sub> to DGND                   | +3.3V ±10%     |

| AV <sub>DD</sub> to AGND                   | +3.3V ±10%     |

| Operating Temperature Range                | –40°C to +85°C |

| (Note 3), (Note 4)                         |                |

| Package Thermal Resistance $(\theta_{JA})$ | 36°C/W         |

| (Note 4)                                   |                |

**Electrical Characteristics** Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $AV_{CC1} = AV_{CC2} = +12V$ ,  $DV_{DD} = AV_{DD} = +3.3V$ . DGND = AGND = 0V, 2/3 Power Mode. See (Note 9).

| Symbol          | Parameter                           | Conditions                                                               | Min                                    | Тур      | Max      | Units  |  |

|-----------------|-------------------------------------|--------------------------------------------------------------------------|----------------------------------------|----------|----------|--------|--|

|                 |                                     |                                                                          | (Note 6)                               | (Note 5) | (Note 6) |        |  |

| Dynamic         | Performance                         | ·                                                                        |                                        |          |          |        |  |

| f <sub>CL</sub> | –3 dB BW                            | $R_{L} = 100\Omega$                                                      |                                        | 50       |          | MHZ    |  |

| SR              | Slew Rate (Note 7)                  | $V_{IN\_DIFF} = \pm 2.4V, R_L = 100\Omega$                               |                                        | 700      |          | V/µs   |  |

| Distortion      | and Noise Response                  |                                                                          |                                        |          |          |        |  |

| HD2             | 2nd Harmonic Distortion             | fc = 1 MHz, $V_O$ = 2 $V_{PP}$ , $R_L$ = 31 $\Omega$                     | $/_{\rm PP}, R_{\rm L} = 31\Omega$ –91 |          |          | dDa    |  |

|                 |                                     | fc = 200 kHz, $V_0 = 2 V_{PP}$ , $R_L = 31\Omega$                        |                                        | -98      |          | - dBc  |  |

| HD3             | 3 <sup>rd</sup> Harmonic Distortion | fc = 1 MHz, $V_O$ = 2 $V_{PP}$ , $R_L$ = 31 $\Omega$                     |                                        | -57      |          | -10 -  |  |

|                 |                                     | fc = 200 kHz, $V_0 = 2 V_{PP}$ , $R_L = 31\Omega$                        |                                        | -71      |          | dBc    |  |

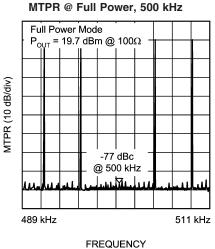

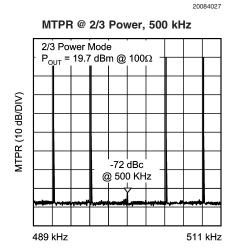

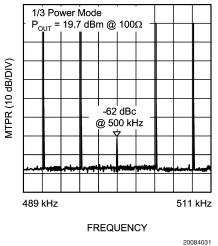

| MTPR            | Multi-Tone Power Ratio              | f = 500 kHz                                                              |                                        | 72       |          | dBc    |  |

| V <sub>IN</sub> | Differential Output Noise           | 100 kHz to 10 MHz                                                        |                                        | 57       |          | nV/√Hz |  |

| Input Cha       | iracteristics                       | •                                                                        |                                        |          |          |        |  |

| V <sub>IN</sub> | Input DC Voltage                    | Common Mode                                                              | 6.04                                   | 6.1      | 6.16     | V      |  |

| R <sub>IN</sub> | Input Resistance                    | Differential                                                             | 14.4                                   | 20       | 28.4     | kΩ     |  |

|                 |                                     | $I_{DIFF} = 10 \ \mu A \text{ from } +IN \text{ to } -IN$                |                                        |          |          |        |  |

| Transfer        | Characteristics                     | · ·                                                                      |                                        | •        | •        |        |  |

| A <sub>V</sub>  | Voltage Gain                        | $V_{IN_{DIFF}} = -1$ to 1V, No Load                                      | +5.37                                  | +5.40    | +5.48    | V/V    |  |

| PSRR            | Power Supply Rejection Ratio        |                                                                          |                                        | -108     |          | dB     |  |

| Xt              | Cross Talk                          | $f = 1 \text{ MHz}, R_L = 100\Omega$                                     |                                        | -95      |          |        |  |

| Vo              | Output Voltage Swing High           | $V_{IN_{DIFF}} = \pm 2.4V$ , No Load                                     |                                        | 11.85    |          |        |  |

|                 |                                     | $V_{IN_{DIFF}} = \pm 2.4 V, R_{L} = 31 \Omega$                           | 11.68                                  | 11.75    |          | V      |  |

|                 |                                     | $V_{IN_{DIFF}} = \pm 2.4V, I_{OUT} = 580 \text{ mA}$                     | 11.64                                  | 11.74    |          |        |  |

|                 | Output Voltage Swing Low            | $V_{IN_{DIFF}} = \pm 2.4V$ , No Load                                     |                                        | 0.15     |          |        |  |

|                 |                                     | $V_{\text{IN DIFF}} = \pm 2.4 \text{V}, \text{R}_{\text{L}} = 31 \Omega$ |                                        | 0.25     | 0.36     | V      |  |

|                 |                                     | $V_{IN DIFF} = \pm 2.4V, I_{OUT} = 580 \text{ mA}$                       |                                        | 0.31     | 0.39     |        |  |

| I <sub>sc</sub> | Output Short Circuit Current        | Sourcing to Ground                                                       |                                        | +800     |          |        |  |

|                 |                                     | Sinking to Ground                                                        |                                        | -800     |          | — mA   |  |

LMH6678

| <b>Electrical Characteristics</b> Unless otherwise specified, all limits guaranteed for $T_J = 25$ °C, $AV_{CC1} = AV_{CC2} =$ |

|--------------------------------------------------------------------------------------------------------------------------------|

| +12V, DV <sub>DD</sub> = AV <sub>DD</sub> = +3.3V. DGND = AGND = 0V, 2/3 Power Mode. See (Note 9). (Continued)                 |

| Symbol            | Parameter                                 | Conditions                                                                           |     |     | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units |    |

|-------------------|-------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|-----------------|-----------------|-----------------|-------|----|

| I <sub>OUT</sub>  | Output Current                            | $V_{IN\_DIFF} = \pm 2.4V$<br>Sourcing, $R_L = 20\Omega$<br>Sinking, $R_L = 20\Omega$ |     |     |                 |                 | ±580            |       | mA |

| V <sub>oc</sub>   | Output Common Mode Voltage                |                                                                                      |     |     |                 | 5.89            | 6               | 6.05  | V  |

| V <sub>os</sub>   | Output Offset Voltage                     |                                                                                      |     |     |                 | -40             | 0               | +40   | mV |

| Power Su          | pply (Note 10), (Note 11)                 | •                                                                                    |     |     |                 | •               |                 |       |    |

| I <sub>cc</sub>   | AV <sub>CC</sub> Quiescent Supply Current | B01                                                                                  | B11 | B02 | B12             |                 |                 |       |    |

|                   | Full Power                                | L                                                                                    | L   | L   | L               | 28.6            | 33              | 36.9  |    |

|                   | 2/3 Power                                 | н                                                                                    | L   | Н   | L               | 18.6            | 22              | 25.4  | mA |

|                   | 1/3 Power                                 | L                                                                                    | Н   | L   | Н               | 9.2             | 12              | 14.3  | mA |

|                   | Shutdown                                  | н                                                                                    | Н   | Н   | Н               |                 | 0.2             | .95   |    |

| I <sub>DV</sub>   | DV <sub>DD</sub> Quiescent Supply Current | B01                                                                                  | B11 | B02 | B12             |                 |                 |       | mA |

|                   | Full Power                                | L                                                                                    | L   | L   | L               | 11              | 16              | 19    |    |

|                   | 2/3 Power                                 | н                                                                                    | L   | Н   | L               | 7               | 12              | 15    |    |

|                   | 1/3 Power                                 | L                                                                                    | Н   | L   | Н               | 3               | 7               | 10.3  |    |

|                   | Shutdown                                  | н                                                                                    | Н   | Н   | Н               |                 | 0.05            | .14   |    |

| I <sub>AV</sub>   | AV <sub>DD</sub> Quiescent Supply Current | All Power Modes                                                                      |     |     | .8              | 1.1             | 1.4             | mA    |    |

| Logic Inp         | uts                                       |                                                                                      |     |     |                 | •               |                 |       |    |

| V <sub>IH</sub>   | Input High Voltage                        |                                                                                      |     |     |                 | 2.7             | 3.3             |       | V  |

| V <sub>IL</sub>   | Input Low Voltage                         |                                                                                      |     |     |                 | 0               | 0.5             | V     |    |

| I <sub>IH</sub>   | Input High Current                        | @ V <sub>IH</sub> = 3.3V                                                             |     |     | -0.5            | 0.02            | +0.5            | μA    |    |

| I <sub>IL</sub>   | Input Low Current                         | @ V <sub>IH</sub> = 0V                                                               |     |     | -0.5            | 0.02            | +0.5            | μA    |    |

| Charge P          | ımp                                       |                                                                                      |     |     |                 | •               |                 |       |    |

| f <sub>CP</sub>   | Charge Pump Frequency                     | Measure at DRIVE at Full Power                                                       |     |     | 2.43            | 2.75            |                 | MHz   |    |

| V <sub>HIGH</sub> | Charge Pump High Average<br>Voltage       | Measure at CstoreH at Full Power                                                     |     |     |                 |                 | +14.6           |       | V  |

| V <sub>LOW</sub>  | Charge Pump Low Average<br>Voltage        | Measure at CstoreL at Full Power                                                     |     |     |                 | –2.7V           |                 | V     |    |

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics. Note 2: Human body model, 1.5kΩ in series with 100pF.

Note 3: Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150° C.

Note 4: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board. Die attach pad is electrically connected to AGND.

Note 5: Typical Values represent the most likely parametric norm.

Note 6: All limits are guaranteed by testing or statistical analysis.

Note 7: Slew rate is the slowest of the rising and falling slew rates.

Note 8: Machine Model,  $0\Omega$  in series with 200 pF.

**Note 9:** Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self heating where  $T_J > T_A$ . Absolute maximum ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically. **Note 10:** Quiescent supply current specification apply for the condition of no input signal. See application section for information on power consumption as a function of output power, power control bit settings and external resistor  $R_{ADJ}$ .

Note 11: "L" is  $V_{IL}$  and "H" is  $V_{IH}$ .

LMH6678

### **Connection Diagram**

Note: Die attach pad is electrically connected to AGND

### **Ordering Information**

| Package | Part Number             | Package Marking | Transport Media          | NSC Drawin |

|---------|-------------------------|-----------------|--------------------------|------------|

|         | LMH6678LQ<br>LMH6678LQX |                 | 1k Units Tape and Reel   |            |

| LLP -   |                         | L6678LQ         | 4.5k Units Tape and Reel | LQA24A     |

|         |                         |                 | 4.5k Units Tape and Reel |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

|         |                         |                 |                          |            |

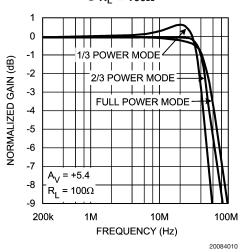

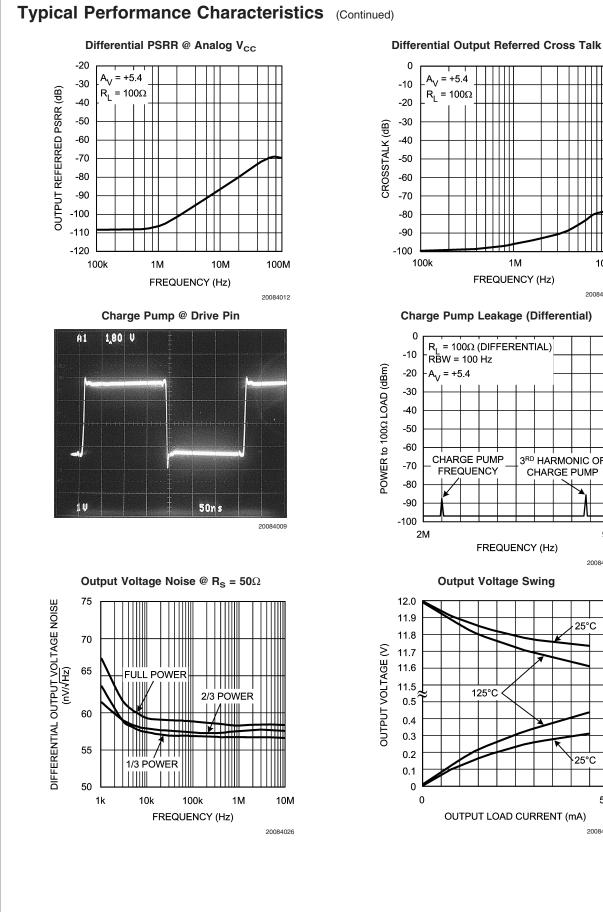

### **Typical Performance Characteristics**

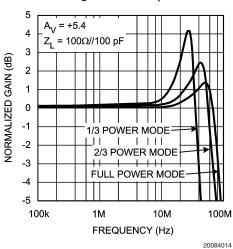

Single-Ended Small Signal Frequency Response @  $R_L = 100\Omega$

20084005

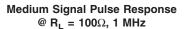

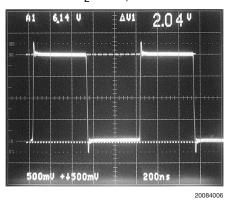

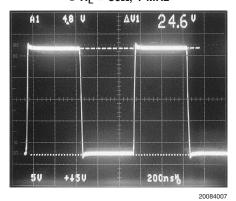

Large Signal Pulse Response @  $R_L = 100\Omega$ , 1 MHz

20084008

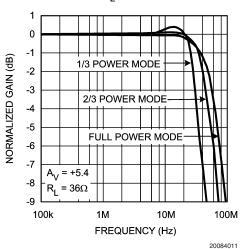

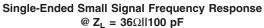

Single-Ended Small Signal Frequency Response @ R\_ = 36  $\Omega$

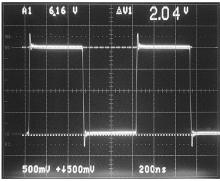

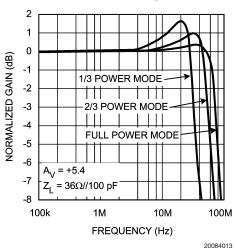

Medium Signal Pulse Response @  $R_L$  = 36 $\Omega$ , 1 MHz

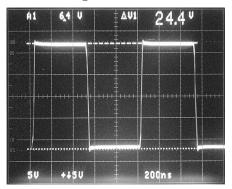

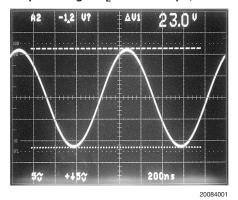

Large Signal Pulse Response @  $R_L = 36\Omega$ , 1 MHz

LMH6678

### Typical Performance Characteristics (Continued)

Single-Ended Small Signal Frequency Response @  $Z_L = 100\Omega ||100 \text{ pF}$

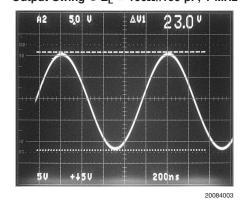

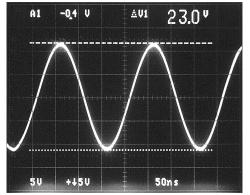

Output Swing @  $Z_L$  = 100 $\Omega$ ||100 pF, 1 MHz

Output Swing @  $Z_L = 100\Omega$ ||100 pF, 5 MHz

20084004

Output Swing @  $Z_{L} = 36\Omega$ ||100 pF, 1 MHz

Output Swing @  $Z_L = 36\Omega$ ||100 pF, 5 MHz

20084002

LMH6678

1M

10M

20084015

9M

20084016

25°C

25°C

500

20084039

3RD HARMONIC OF

CHARGE PUMP

# Typical Performance Characteristics (Continued)

LMH6678

FREQUENCY

20084032

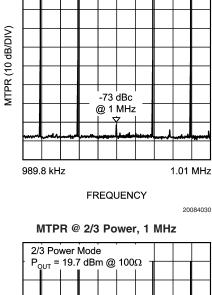

MTPR @ Full Power, 1 MHz

Full Power Mode  $P_{OUT}$  = 19.7 dBm @ 100 $\Omega$

20084029

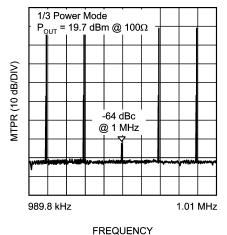

#### MTPR @ 1/3 Power, 1 MHz

20084028

### Typical Performance Characteristics (Continued)

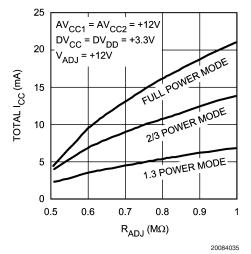

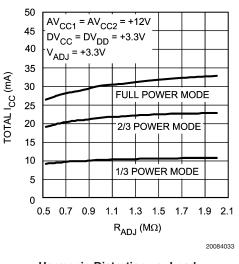

Detail View of Total I<sub>CC</sub> vs. R<sub>ADJ</sub> @ V<sub>ADJ</sub> = +12V

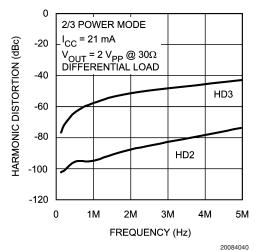

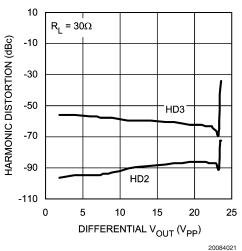

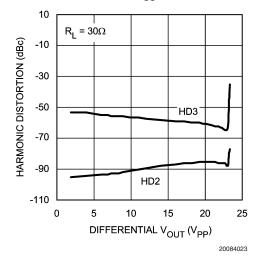

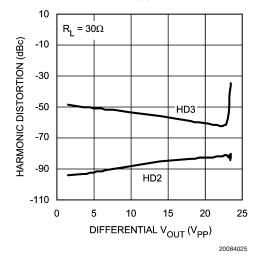

Harmonic Distortion vs. Frequency

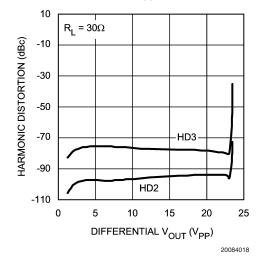

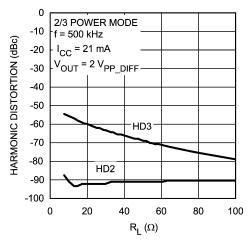

Harmonic Distortion vs. Load

20084017

LMH6678

LMH6678

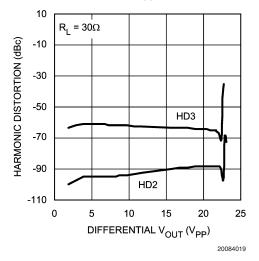

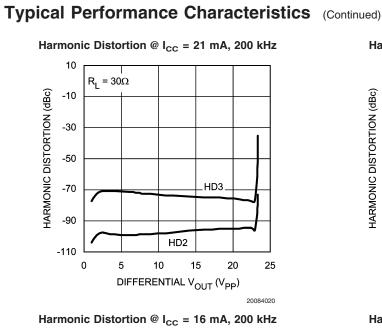

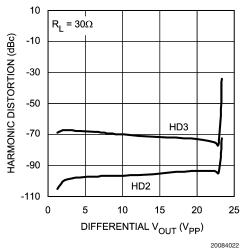

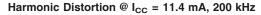

Harmonic Distortion @ I<sub>CC</sub> = 16 mA, 1 MHz

Harmonic Distortion @  $I_{CC}$  = 11.4 mA, 1 MHz

### **Application Notes**

#### FUNCTIONAL DESCRIPTION

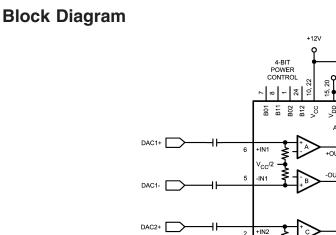

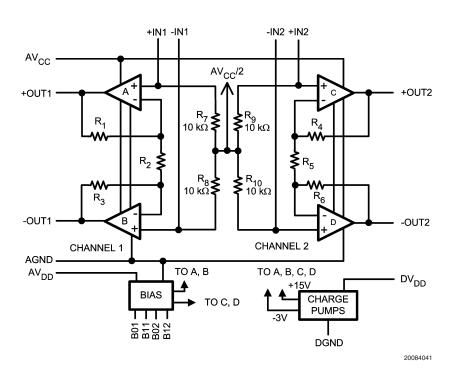

The LMH6678 contains two pairs of high speed/high output current operational amplifiers configured as two amplifiers differential inputs and outputs, as shown in *Figure 1*. Quies-

cent current can be set independently for each channel via two control bits as depicted in table 1. Also, quiescent current can be continuously varied by selection of an external resistor between the ADJ pin and a supply voltage of either +12V or +3.3V. LMH6678

FIGURE 1. Functional Block Diagram

# TABLE 1. Power Mode LogicControl

|            | Channel A (B)       |   |  |

|------------|---------------------|---|--|

| Power Mode | B01 (B02) B11 (B12) |   |  |

| Full Power | L                   | L |  |

| 2/3 Power  | Н                   | L |  |

| 1/3 Power  | L                   | Н |  |

| Shutdown   | Н                   | Н |  |

Channel A and B are set independently.

Two supply voltages are required, +12V ±10% and +3.3V ±10%. Current for the driver amplifiers, including their output current, flows from the 12V analog V<sub>CC</sub> (AV<sub>CC</sub>) supply and Analog Ground (AGND.) For proper output swing and distortion performance, both AV<sub>CC</sub> pins must be connected to +12V and the exposed metal pad must be soldered to ground potential as described in the layout section. Both AV<sub>DD</sub> and DV<sub>DD</sub> pins must be connected to +3.3V. The internal bias circuitry is powered from AV<sub>DD</sub> and AGND while the digital circuitry and charge pump are powered from DV<sub>DD</sub> and DGND. This allows separate bypassing and decoupling for AV<sub>DD</sub> and DV<sub>DD</sub>.

All supply voltage pins need a 0.1  $\mu F$  ceramic capacitor in parallel with a 4.7  $\mu F$  capacitor as bypass capacitors. The 0.1  $\mu F$  capacitor should be as close as possible to the supply voltage pin and the larger capacitor placed next to it.

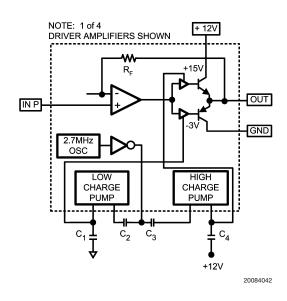

The LMH6678 delivers very low power consumption at a single +12V analog supply voltage by a combination of its circuit architecture and the on-chip dual charge pump. The output stage is an emitter-follower type, which can provide low distortion, low quiescent current and high peak output currents.

The charge pumps generate two internal dc voltages, V<sub>HIGH</sub> = +15V and V<sub>LOW</sub> = -3V. As shown in *Figure 2*, V<sub>HIGH</sub> and V<sub>LOW</sub> supply base currents for the output stages. This enables the drivers to swing within a V<sub>CE</sub>(sat) of V<sub>CC</sub> and ground, giving the LMH6678 its high swing of +11.5 V<sub>PP</sub> into a 31 $\Omega$  load.

FIGURE 2. Internal Connections of Integrated Charge Pumps

#### CHARGE PUMPS

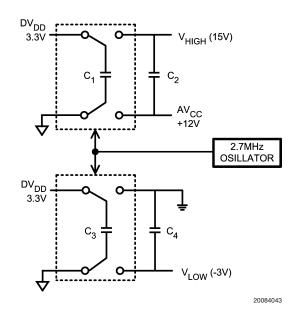

*Figure 3* is a simplified schematic of the internal charge pumps. Each pump consists of a transfer capacitor and a reservoir capacitor and switches. The states of switches are driven by an internal 2.75 MHz clock oscillator. The transfer capacitor of the high charge pump, C1, is connected across DV<sub>DD</sub> and DGND during one phase of the clock and between V<sub>HIGH</sub> and AV<sub>CC</sub> during the opposite phase. This causes its reservoir capacitor, C<sub>2</sub>, to charge up to DV<sub>DD</sub> (3.3Volts) potential less a small drop due to finite switch resistance. V<sub>HIGH</sub> therefore is pumped to nearly V<sub>CC</sub> + V<sub>DD</sub> potential or approximately +15V.

Similarly, the transfer capacitor of the low charge pump,  $C_3$ , is connected across  $DV_{DD}$  and DGND during one phase of the clock and between AGND and  $V_{LOW}$  during the opposite phase. This causes its reservoir capacitor,  $C_4$ , to charge up to  $V_{DD}$  potential less a small drop due to finite switch resistance.  $V_{LOW}$  therefore is pumped to nearly  $-V_{DD}$  potential or approximately -3V.

The charge pumps outputs provide both dc bias currents and the base current of the output transistors. These base currents are small compared to the dc bias currents. Typical and maximum quiescent  $V_{DD}$  supply currents are given in the electrical characteristics. Thus, for the charge pump capacitors  $C_1$ - $C_4$ , the suggested values are 0.022 µF 20% X7R type. With theses values, the ripple on  $V_{HIGH}$  and  $V_{LOW}$  will be approximately 40 m $V_{PP}$ . This results in a small spurious output on the line of typically –120 dBm/Hz at 2.75 MHz. Spurs produced at harmonics of the clock frequency are at least 20 dB lower and further attenuated by the transformer. This is shown in the typical performance characteristics section. Ripple and spurious outputs can be further attenuated by increasing the size of the reservoir capacitors  $C_2$  and  $C_4$ .

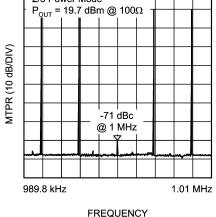

#### MULTI-TONE POWER RATIO AND NOISE

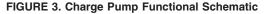

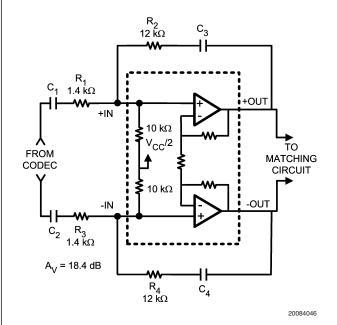

The Multi-Tone Power Ratio of the LMH6678 is shown in the typical performance characteristics section. MTPR is the best representation of non-linearity for ADSL modems. The measurement is accomplished with all ADSL bins transmitting full power except one. The delta between the peak amplitude of the transmitting carriers and energy left in the single bin defines the maximum available SNR for that bin. The test circuit is described in *Figure 4*. Here R<sub>2</sub>, C<sub>3</sub>, R<sub>4</sub> and C<sub>4</sub> were added for increase gain.

FIGURE 4. MTPR Measurement Test Circuit

## R-C TERMINATION CIRCUIT AND TRANSFORMER TURNS RATIO

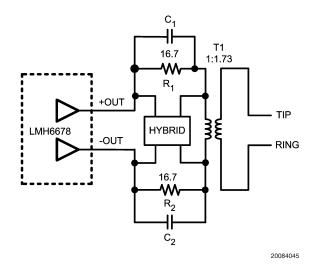

The LMH6678 was designed to operate in the circuit of *Figure 5.* In this circuit, resistor  $R_1$  and  $R_2$  provide a line termination in the upstream band. At higher frequencies in the downstream band, capacitors  $C_1$  and  $C_2$  bypass  $R_1$  and  $R_2$  for higher efficiency.

To calculate the transformer turns ratio required, we assume a peak-to-rms ratio of 5.8 must be supported and the V<sub>CC</sub> supply tolerance is 5%. At a 30 $\Omega$  load, the driver outputs can swing to 350 mV of each rail with low distortion. This gives a peak swing of 12(.95) –0.7 = 10.7V. A typical selection for C<sub>1</sub>, C<sub>2</sub>, R<sub>1</sub> and R<sub>2</sub> results in approximately 0.1 dB loss and the transformer loss is typically 0.25 dB, so total voltage loss is about 0.35 dB.

For 19.8 dBm output, line rms voltage is 3.09 and peak voltage is 17.9. The optimum turns ratio is calculated at 1.035 x 17.9/10.7 = 1.73. This gives a reflected line impedance of  $100\Omega/(1.73)^2 = 33.4$  at the primary side. R<sub>1</sub> and R<sub>2</sub> are usually chosen to be 33.4/2 = 16.7 to terminate the line at lower frequencies.

FIGURE 5. Typical R-C Termination

#### INPUT POWER LEVEL AND GAIN

With losses included, output power from the LMH6678 should be 19.8 dBm + 0.35 dB = 20.15 dBm or 103.5 mW. At 33.4 $\Omega$ , the rms differential output voltage is  $\sqrt{(PxR)}$  = 1.86 Vrms. The driver amplifiers have a voltage gain of 5.4V/V, so the input level should be 1.86/5.4 = 344 mV\_{RMS} to deliver 19.8 dBm to the line.

The driver input equivalent circuit is shown in *Figure 1*. The inputs should be capacitively coupled to maintain the input and output common-mode voltage at  $V_{\rm CC}/2$ .

If additional gain is required, the gain can be increased with positive feedback using the circuit of *Figure 6*. In this case the voltage gain  $A_V$  will be

$$A_{V} = 5.4^{*}(1-K)/(1-5.4^{*}K)$$

Where

$$\begin{split} \mathsf{K} &= (\mathsf{R}_1||10\mathsf{K})/(\mathsf{R}_1||10\mathsf{K}+\mathsf{R}_2) = 10\mathsf{K}^*\mathsf{R}_1(10\mathsf{K}^*\mathsf{R}_1+\mathsf{R}_1\mathsf{R}_2+\\ 10\mathsf{K}^*\mathsf{R}_2) \text{ and } \mathsf{R}_1 = \mathsf{R}_3, \, \mathsf{R}_2 = \mathsf{R}_4 \end{split}$$

It is suggested to choose  $\mathsf{R_1} < \mathsf{3K}$  so that the 15% tolerance of the input resistance will not greatly affect the gain. Furthermore, this circuit will have a differential input resistance of

$$R_{IN, DIFF} = 2^{R_1} - 2^{R_2}/(4.4)$$

which may be negative in band. Usually no stability problems are seen if this  $|R_{\rm IN}|$  is chosen larger than 500 $\Omega$ . To minimize distortion caused by loading on the Codec outputs,  $|R_{\rm IN}|$  is usually chosen to be 1k $\Omega$  or more. Additional blocking capacitors C\_3 and C\_4 must be inserted in series with R\_2 and R\_4 to prevent the circuit from latching. C\_3 and C\_4 should be chosen to be less than 1/5 of C\_1 to avoid large signal oscillation.

FIGURE 6. Increasing Gain

#### **ACTIVE TERMINATION CIRCUIT**

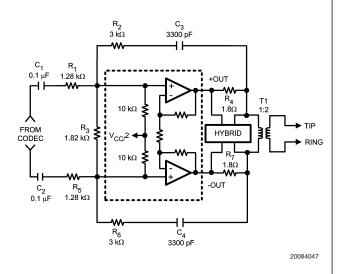

The LMH6678 can be used to synthesize the output impedance by using positive feedback to increase the output resistance. In ADSL this technique is often used to lower the total power consumption of the line driver by reducing the voltage across the series termination resistors. This approach gives slightly higher power consumption but better return loss in the downstream band compared to the R-C termination of Figure 5. The equations that follow and Figure 7 describe how to implement this technique with the LMH6678.

- Pick positive feedback factor (also called the resistance gain), A<sub>z</sub>.

- 2. Pick desired output resistance,  ${\rm R}_{\rm OUT},$  seen by the line.

- 3. Calculate transformer turns ratio based on  $A_Z$ , line driver voltage swing, and transformer insertion loss (TIL).  $R_L$  is the line impedance, 100 $\Omega$  for ADSL.

- $N = [(V_{LINEPP} / (2 * 11.2)]^* [(1 + R_{OUT} / (R_L * A_Z)] * 10^{(TIL/20)}$

$$R_4 = R_{OUT} / (2 * A_Z * N^2)$$

5. Calculate the resistance looking into the transformer secondary (chip side).

$$R_{SEC} = R_L / N^2$$

$K_1 = (A_Z - 1)/(5.4 * A_Z)$

6. Calculate K<sub>1</sub>.

4.

7. Calculate K<sub>2</sub>.

$$K_2 = R_{SEC} / (R_{SEC} + 2 * R_4)$$

8. Pick a value for  $R_2$ . Typically  $3k\Omega$  is a good value.

$R_{EQ} = R_2/(1-5.4^* K_2)$  (Note  $R_{EQ}$  is usually negative.) 10. Calculate  $R_{IN}$

$R_{IN} = [(K_1 * R_2)/(1 - K_1) * 10k]/[10k - (K_1 * R_2)/(1 - K_1)]$

- 11. Calculate the gain without the input voltage divider.

- $A_{V1} = N*5.4*K_2 * [(R_{EQ}//10k)/(R_{IN} + R_{EQ}//10k)] /(10^{TIL/20})$

- 12. . Calculate  $A_{\text{VTOTAL}}$  the final required gain from input to the line.

$A_{VTOTAL} = V_{LINERMS} / V_{INRMS}$

13. . Calculate the voltage divider network of R1 and R3 using  $A_{V1},\, transformer$  insertion loss (TIL),

$$R_1 = R_{IN} * [A_{V1}/(A_{VTOTAL} * 10^{TIL/20})]$$

$$R_3 = (2 * R_{IN})/[1 - (A_{VTOTAL}*10^{TIL/20})/A_{V1}]$$

The example shown in Figure 7 is designed to the following parameters:

$V_{\text{LINERMS}} = 3.13V$  (19.8 dBm output power)  $A_7 = 4.5$

$R_{OUT} = 65\Omega$  (13.5dB return loss)

Crest Factor = 5.8 @ nominal 12V supply

Transformer Insertion Loss = 0.4dB

V<sub>INRMS</sub> = 350mV (AFE output level)

FIGURE 7. Active Termination Application

#### POWER CONSUMPTION

Power consumption is a function of line power and dynamic bias current of the line driver. After the transformer turns ratio has been selected as described above, power consumption per channel for the typical R-C termination application can be estimated as follows:

$$I_{CC} = IdB + I_{LOAD}$$

IdB = 0.25 \* Iq

This is because 25% of the total dc current flows in the output transistors. This term effectively vanishes when the class AB stage is drives a heavy load.

Where  ${\rm I}_{\rm LOAD}$  = average load current driven by output transistors

$\text{IdB} = \text{dynamic V}_{\text{CC}}$  bias current while driving full load power

$I_{CC}$  = average  $V_{CC}$  current

When losses included, 103.5 mW is delivered by the driver, therefore

I<sub>RMS</sub> = TR\* √(.1035/100) = 32.2 mA

Since the ADSL signal is DMT and is effectively guassian, the average value of the supply current due to driving the load is given by

$$\rm I_{LOAD}$$

= averageII  $_{\rm RMS}$  I =  $\sqrt{(2/\pi)^{\star}} \rm I_{\rm RMS}$  = 0.8 \* I  $_{\rm RMS}$  = 44.6 mA for TR = 1.73

Assuming 2/3 power mode, lfixed = 0.25 \* 11 mA = 2.75 mA

$$I_{CC} = 2.75 \text{ mA} + 44.6 \text{ mA} = 47.4 \text{ mA}$$

$$P_{CC} = I_{CC} \times V_{CC} = 569 \text{ mW}$$

To get the  $I_{\rm DD}$  full current, simply add 0.75 mA to the quiescent current per channel:

$$I_{DD} = 0.75 + 5.5 + 0.6 = 6.8 \text{ mA}$$

$P_{DD} = V_{DD} * I_{DD} = 23 \text{ mW}$

For the total power consumption per channel,

$P_{\rm CON} = P_{\rm DD} + P_{\rm CC} = 592 \text{ mW}$

For power dissipation of the LMH6678, subtract the power into the load plus external losses:

P<sub>DISS</sub> = 592-103 = 489 mW per channel

$P_{DISS}$  total = 2 x 489 = 978 mW for both channels

Proper selection of the external resistor between the ADJ pin can optimize the trade-off between power consumption and distortion. This external resistor will reduce the supply current for the 1/3, 2/3 and full bias settings for both channels. The approximately equation is

$$I_{S} = I_{S} * (1 - (V_{CC} - 0.8)/(30\mu A^{*}R_{ADJ}))$$

Curves of  $V_{\rm CC}$  and  $V_{\rm DD}$  supply currents per channel vs.  $R_{\rm ADJ}$  for the various power settings are shown in typical performance characteristics section.

#### PACKAGE AND LAYOUT CONSIDERATION

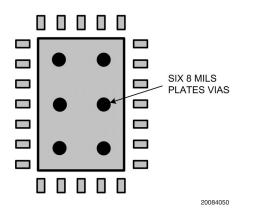

The LMH6678 uses the 24-pin Leadless Leadframe Package, a thermally enhanced, standard size IC package designed to eliminate the use of bulky heatsinks traditionally used in thermal packages. This package can be easily mounted using standard PCB surface mount assembly techniques.

The LLP is designed so that the thermal pad is exposed on the bottom of the IC, as shown in the package drawing. This provides an extremely low thermal resistance ( $\theta_{JC}$ ) path between the die and the exterior of the package. The thermal pad on the bottom of the IC can then be soldered directly to

the PCB, using the PCB as a heatsink. In addition, platedthrough holes (vias) on the PCB provide a low thermal resistance heat flow path to the backside of the circuit board.

## LAND PATTERN AND ASSEMBLY GUIDELINE FOR LMH6678

- 1. The thermal pad must be connected to analog ground AGND in LMH6678.

- 2. Prepare the PCB with a top-side land pattern, as shown in figure 8.

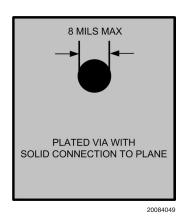

- 3. Place the recommended number of plated-through holes in the area of the thermal pad. These holes should be 8 mils max. in diameter. They are kept small so that solder wicking through the holes is not a problem during reflow. The minimum recommended number of holes for the 24-pin LLP is six, as shown in *Figure 8*.

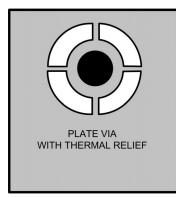

- 4. Connect all holes to the internal and bottom analog ground plane.

- 5. When laying out these holes to the ground plane, do not use the typical web or spoke via connection methodology, as shown in *Figure 9*. Web connections have a high thermal resistance connection that is useful for slowing the heat transfer during soldering operations. This makes soldering the vias that have ground plane connections easier. However, in this application, low thermal resistance is desired for the most efficient heat transfer. Therefore, the holes under the thermal pad should make their connection to the internal ground plane with a complete connection around the entire circumference of the plated-through hole. Use plated via with solid connection to plane as shown in *Figure 10*.

- The top-side solder mask should leave the terminals of the pad connections and the thermal pad area exposed. The thermal pad area should leave the 8 mils holes exposed.

- 7. Apply solder paste to the exposed thermal pad area and all of the package terminals.

- 8. With these preparatory steps in place, the LLP is simply placed in position and run through the solder reflow operation as any standard surface-mount component. This results in a part that is properly installed.

FIGURE 8. Recommended Land Pattern

20084048

#### FIGURE 9. Via Connection Not Recommended Under the Thermal Pad

FIGURE 10. Via Connection Recommended For Use in Thermal Pad

#### HIGH SPEED DRIVER LAYOUT GUIDELINES

The LMH6678 is a high performance differential line amplifier that requires proper layout for best performance.

- Keep power-supply leads as short as possible. This will keep inductance low and resistive losses at a minimum.

- Proper power-supply bypassing with low ESR capacitors is essential to achieve good performance. A parallel combination of small (around 0.1 µF) ceramic and bigger (6.8 µF) tantalum bypass capacitors will provide low and impedance over a wide frequency rage.

- Bypass capacitor should be placed as close as possible, limited by pick and place machine requirement, to the power-supply pins of the LMH6678 (ceramic cap first and then tantalum cap).

- PCB traces conducting high currents, such as from output to load or from power-supply connector to the power-supply pins of the LMH6678 should be kept as wide and short as possible to minimize inductance and resistive loss.

- The six holes in the landing pattern for the LMH6678 are for the thermal vias that connect the thermal pad of LLP package to the internal/external ground plane on the PCB.

For detail information on the LLP package including thermal modeling considerations and prepared procedures, please see National Semiconductor.

"Applications Note 1187: Leadless Leadframe Package (LLP)" located at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +44 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.