SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

- **Excellent-Price/Performance Floating-Point Digital Signal Processor (DSP):** TMS320C6711D

- Eight 32-Bit Instructions/Cycle

- 167-, 200-, 250-MHz Clock Rates

- 6-, 5-, 4-ns Instruction Cycle Time

- 1000, 1200, 1500 MFLOPS

- Advanced Very Long Instruction Word (VLIW) C67x<sup>™</sup> DSP Core

- Eight Highly Independent Functional Units:

- Four ALUs (Floating- and Fixed-Point)

- Two ALUs (Fixed-Point)

- Two Multipliers (Floating- and Fixed-Point)

- Load-Store Architecture With 32 32-Bit **General-Purpose Registers**

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- **Instruction Set Features**

- Hardware Support for IEEE **Single-Precision and Double-Precision** Instructions

- Byte-Addressable (8-, 16-, 32-Bit Data)

- 8-Bit Overflow Protection

- Saturation

- Bit-Field Extract, Set, Clear

- Bit-Counting

- Normalization

- L1/L2 Memory Architecture

- 32K-Bit (4K-Byte) L1P Program Cache (Direct Mapped)

- 32K-Bit (4K-Byte) L1D Data Cache (2-Way Set-Associative)

- 512K-Bit (64K-Byte) L2 Unified Mapped RAM/Cache (Flexible Data/Program Allocation)

- **Device Configuration**

- Boot Mode: HPI, 8-, 16-, 32-Bit ROM Boot

- Endianness: Little Endian, Big Endian

- Enhanced Direct-Memory-Access (EDMA) **Controller (16 Independent Channels)**

- 32-Bit External Memory Interface (EMIF) **Glueless Interface to Asynchronous**

- Memories: SRAM and EPROM - Glueless Interface to Synchronous Memories: SDRAM and SBSRAM

- 256M-Byte Total Addressable External **Memory Space**

- **16-Bit Host-Port Interface (HPI)**

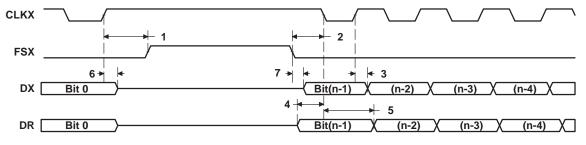

- **Two Multichannel Buffered Serial Ports** (McBSPs)

- Direct Interface to T1/E1, MVIP, SCSA Framers

- ST-Bus-Switching Compatible

- Up to 256 Channels Each

- AC97-Compatible

- Serial-Peripheral-Interface (SPI) Compatible (Motorola<sup>™</sup>)

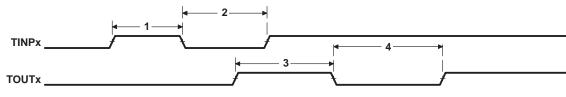

- **Two 32-Bit General-Purpose Timers**

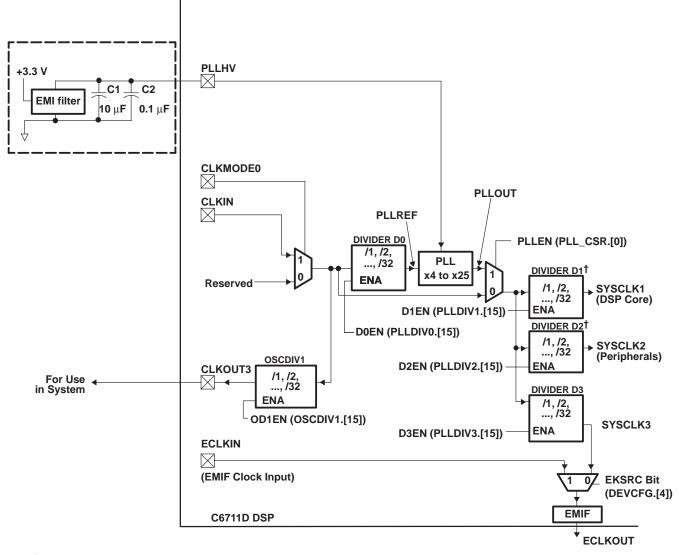

- Flexible Software Configurable PLL-Based **Clock Generator Module**

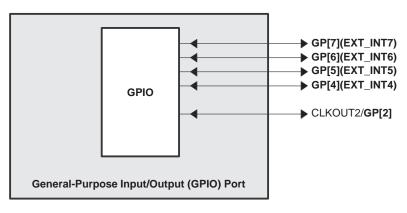

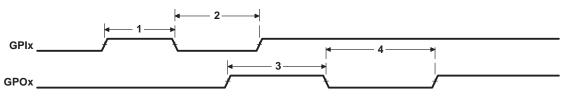

- A Dedicated General-Purpose Input/Output (GPIO) Module With 5 Pins

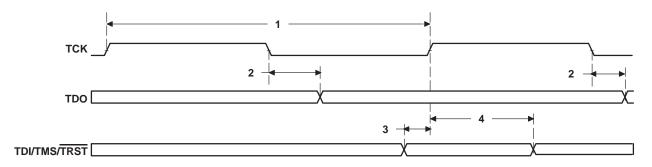

- IEEE-1149.1 (JTAG<sup>†</sup>) **Boundary-Scan-Compatible**

- 272-Pin Ball Grid Array (BGA) Package (GDP and ZDP Suffixes)

- CMOS Technology - 0.13-µm/6-Level Copper Metal Process

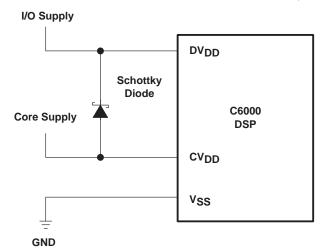

- 3.3-V I/O, 1.4-V Internal (-250)

- 3.3-V I/O. 1.20-V Internal <sup>‡</sup>

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TMS320C67x and C67x are trademarks of Texas Instruments. Motorola is a trademark of Motorola, Inc.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

All trademarks are the property of their respective owners.

IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture. These values are compatible with existing 1.26V designs.

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

#### **Table of Contents**

| revision history                                | . 3 |

|-------------------------------------------------|-----|

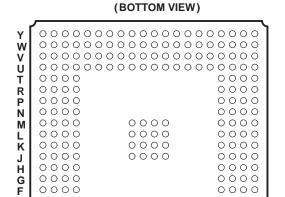

| GDP and ZDP BGA packages (bottom view)          | 5   |

| description                                     | 6   |

| device characteristics                          | . 7 |

| device compatibility                            | . 8 |

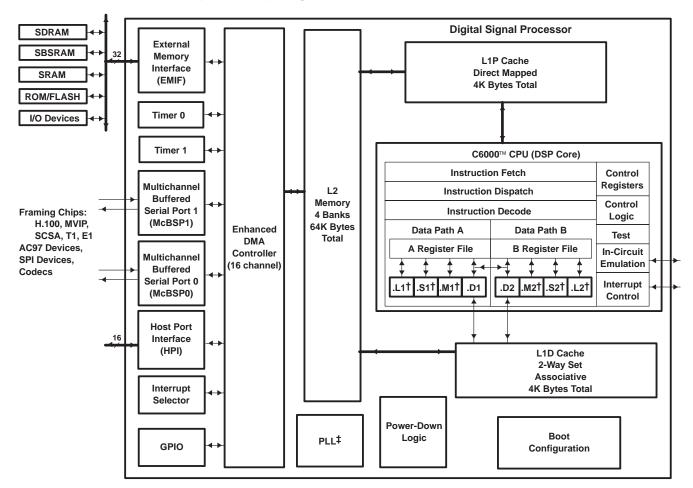

| functional block and CPU (DSP core) diagram     | . 9 |

| CPU (DSP core) description                      | 10  |

| memory map summary                              | 12  |

| peripheral register descriptions                |     |

| signal groups description                       | 18  |

| device configurations                           | 21  |

| terminal functions                              | 24  |

| development support                             | 37  |

| device support                                  | 38  |

| CPU CSR register description                    | 41  |

| cache configuration (CCFG) register description | 43  |

| interrupt sources and interrupt selector        | 44  |

| EDMA module and EDMA selector                   | 45  |

| PLL and PLL controller                          | 47  |

| general-purpose input/output (GPIO)             | 54  |

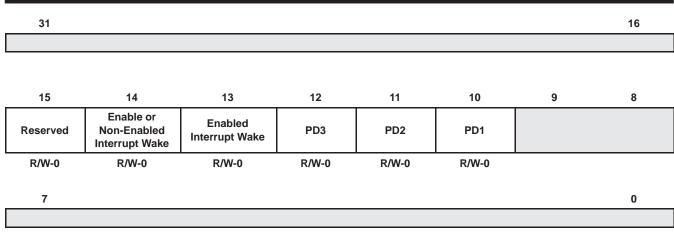

| power-down mode logic                           |     |

| power-supply sequencing                         |     |

| power-supply decoupling                         |     |

| IEEE 1149.1 JTAG compatibility statement        |     |

| EMIF device speed                               |     |

|                                                 |     |

| EMIF big endian mode correctness                                                                      | 61  |

|-------------------------------------------------------------------------------------------------------|-----|

| bootmode                                                                                              | 62  |

| reset                                                                                                 | 62  |

| absolute maximum ratings over operating case temperature range                                        | 63  |

| recommended operating conditions                                                                      | 63  |

| electrical characteristics over recommended ranges of supply voltage and operating case temperature . | 64  |

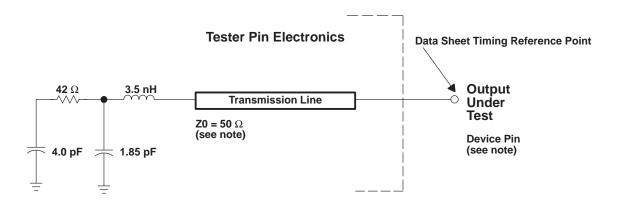

| parameter measurement information                                                                     | 65  |

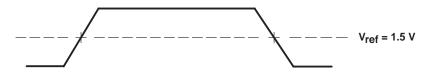

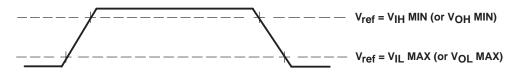

| signal transition levels                                                                              | 65  |

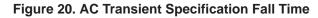

| timing parameters and board routing analysis                                                          | 67  |

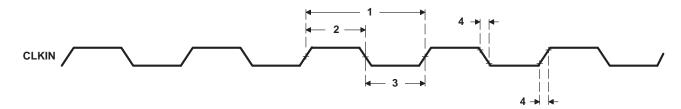

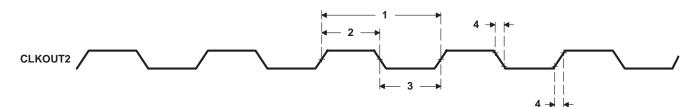

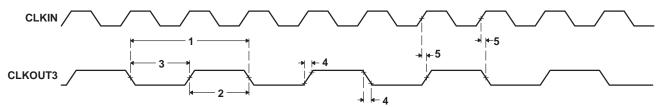

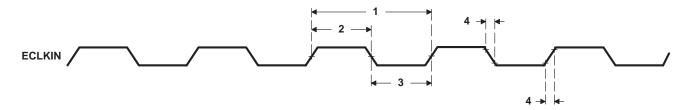

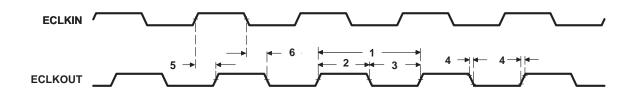

| input and output clocks                                                                               | 69  |

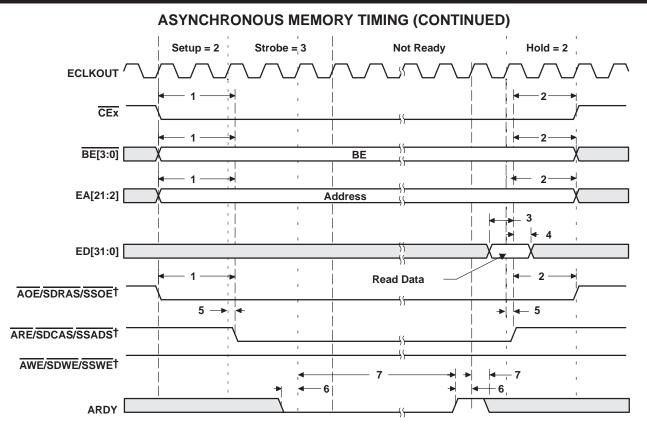

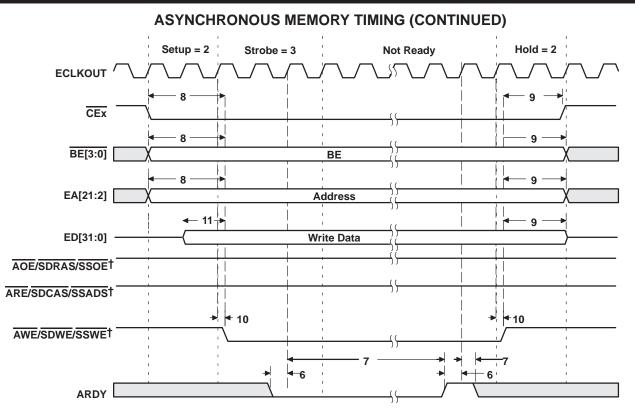

| asynchronous memory timing                                                                            | 72  |

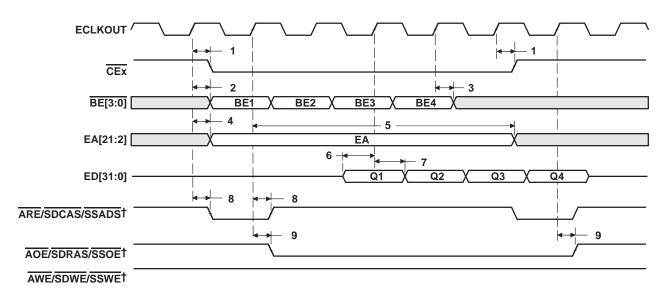

| synchronous-burst memory timing                                                                       | 75  |

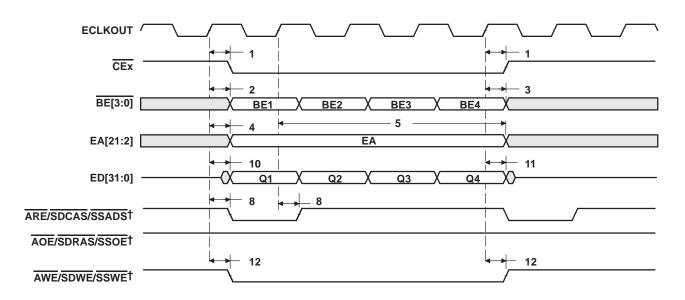

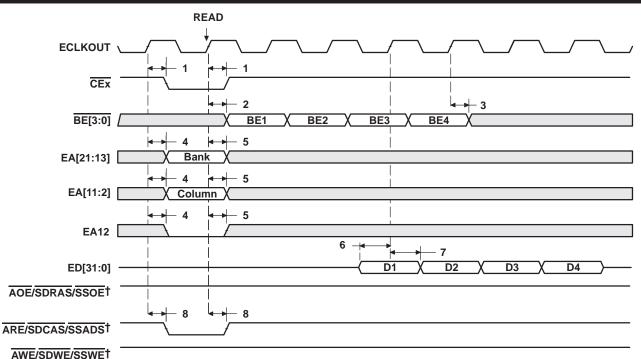

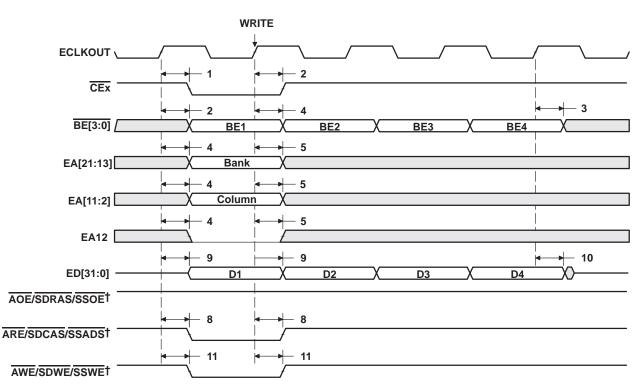

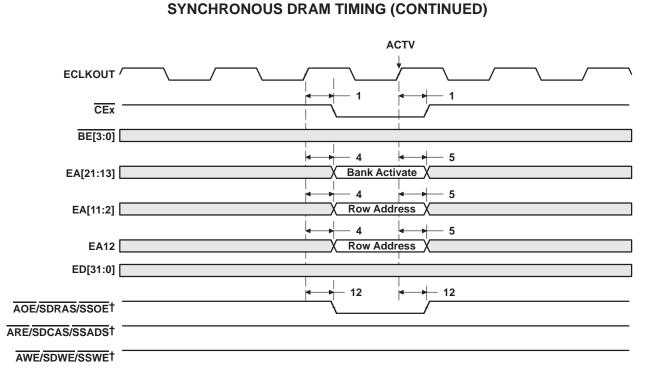

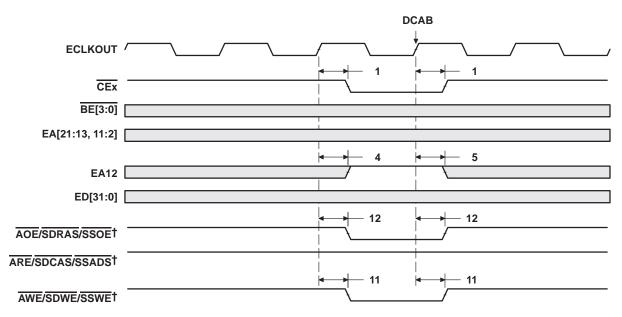

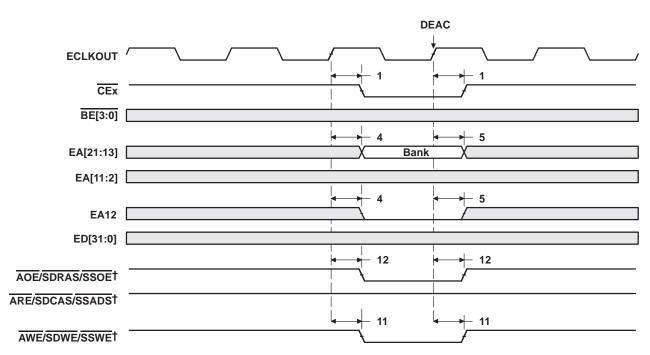

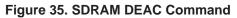

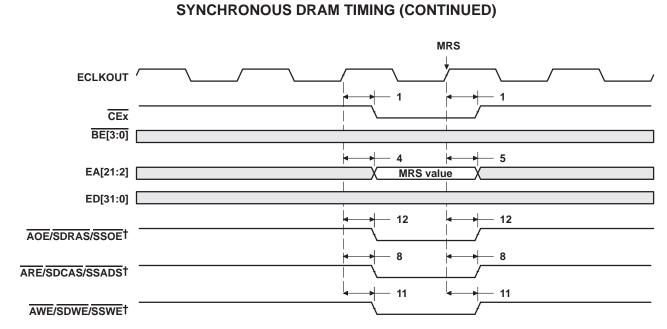

| synchronous DRAM timing                                                                               | 77  |

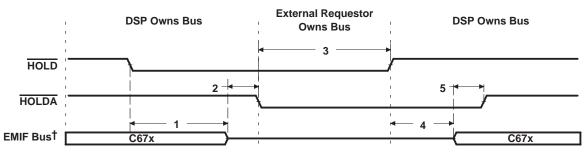

| HOLD/HOLDA timing                                                                                     | 83  |

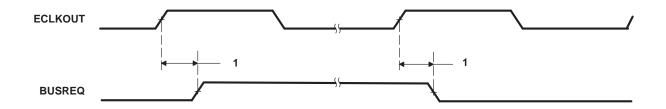

| BUSREQ timing                                                                                         | 84  |

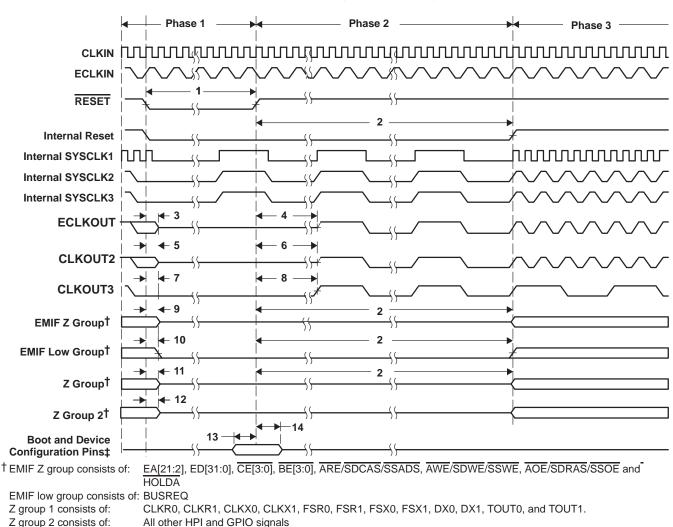

| reset timing                                                                                          | 85  |

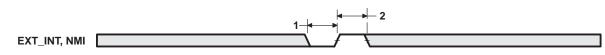

| external interrupt timing                                                                             | 87  |

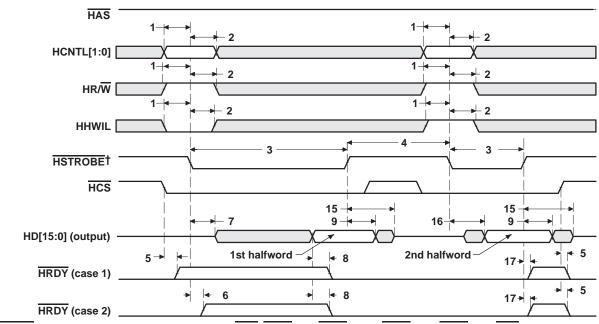

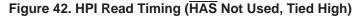

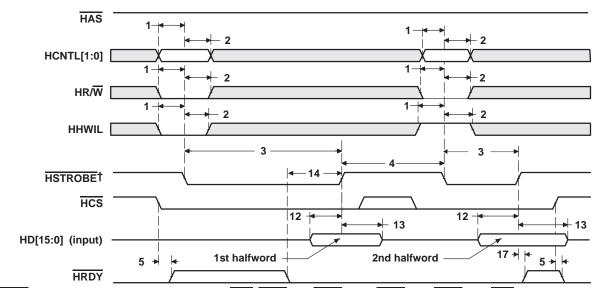

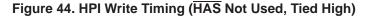

| host-port interface timing                                                                            | 88  |

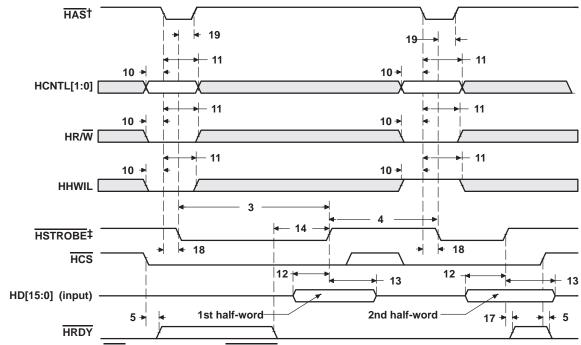

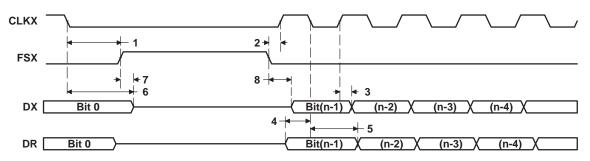

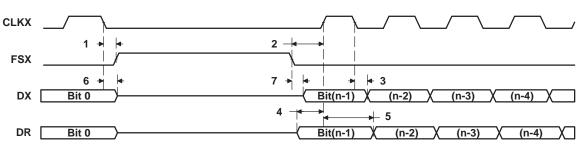

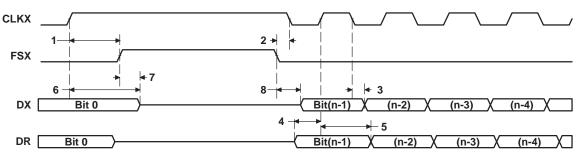

| multichannel buffered serial port timing                                                              | 92  |

| timer timing                                                                                          | 101 |

| general-purpose input/output (GPIO) port timing                                                       | 102 |

| JTAG test-port timing                                                                                 | 103 |

| mechanical data                                                                                       | 104 |

### **REVISION HISTORY**

The TMS320C6711D device-specific documentation has been split from *TMS320C6711, TMS320C6711B*, *TMS320C6711D Floating–Point Digital Signal Processors*, literature number SPRS088N, into a separate Data Sheet, literature number SPRS292. It also highlights technical changes made to SPRS292 to generate SPRS292A. These changes are marked by "**[Revision A]**." Additionally, made changes to SPRS292A to generate SPRS292B. These changes are marked by "**[Revision B]**." Both Revision A and B changes are noted in the Revision History table below.

**Scope:** Updated information on McBSP and JTAG for clarification. Changed Pin Description for A12 and B11 (Revisions SPRS292 and SPRS292A). Updated Nomenclature figure by adding device–specific information for the ZDP package. Updated Characteristics of the Processor table with device–specific information (footnote) for the ZDP package

TI Recommends for *new designs* that the following pins be configured as such:

- Pin A12 connected directly to CV<sub>DD</sub> (core power)

- Pin B11 connected directly to V<sub>ss</sub> (ground)

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21             | Device Configurations, device configurations at device reset:<br>Updated "For proper device operation" paragraph <b>[Revision B]</b>                                                                                                                                                            |

| 22             | Device Configurations, Device Configurations Pins at Device Reset (HD[4:3], HD8, HD12, and CLKMODE0) section: Removed "CE1 width 32-bit" from Functional Description for " <b>00</b> " in HD[4:3](BOOTMODE) Configuration Pin                                                                   |

| 22             | Device Configurations, Device Configurations Pins at Device Reset (HD[4:3], HD8, HD12, and CLKMODE0) section: Updated "All other HD pins" footnote <b>[Revision B]</b>                                                                                                                          |

| 26             | Terminal Functions, <u>Resets and Interrupts section</u> :<br>Updated IPU/IPD for RESET Signal Name <i>from</i> "IPU" <i>to</i> ""                                                                                                                                                              |

| 27             | Terminal Functions, Host Port Interface, Description section:<br>Updated "Other HD pins" paragraph <b>[Revision B]</b>                                                                                                                                                                          |

| 27             | Terminal Functions, Host Port Interface section:<br>Removed "CE1 width 32–bit" from Description for " <b>00</b> " in Bootmode HD[4:3]                                                                                                                                                           |

| 32             | Terminal Functions, Reserved for Test section:<br>Updated Description for RSV Signal Name, A12 GDP/ZDP<br>Updated Description for RSV Signal Name, B11 GDP/ZDP                                                                                                                                  |

| 32             | Terminal Functions, Reserved for Test section:<br>Updated/changed Description for RSV Signal Name, A12 GDP (to <i>"recommended"</i> ) – <b>[Revision A]</b><br>Updated/changed Description for RSV Signal Name, B11 GDP (to <i>"recommended"</i> ) – <b>[Revision A]</b>                        |

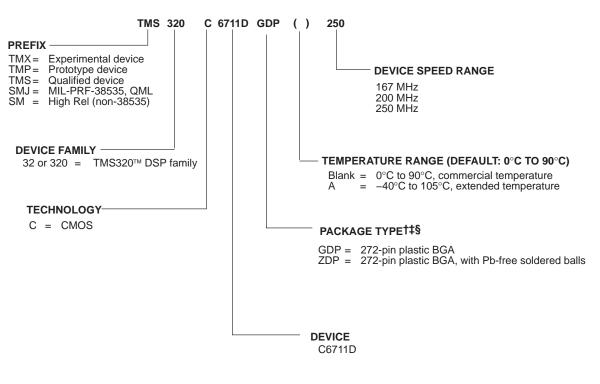

| 39             | Device Support, device and development-support tool nomenclature:<br>Updated figure for clarity                                                                                                                                                                                                 |

| 40             | Device Support, documentation support section:<br>Updated paragraphs for clarity                                                                                                                                                                                                                |

| 55             | Power–Down Mode Logic – Triggering, Wake–up and Effects section:<br>Updated paragraphs <b>[Revision B]</b>                                                                                                                                                                                      |

| 57             | Power–Down Mode Logic – Triggering, Wake–up and Effects section, Characteristics of the Power-Down Modes table:<br>Added "It is recommended to use the PLLPWDN bit (PLLCSR.1) as an alternative to PD3" to PRWD Field (BITS 15–10) –<br>011100 – Effect on Chip's Operation <b>[Revision B]</b> |

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                                     |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 57             | Power–Down Mode Logic – Triggering, Wake–up and Effects section, Characteristics of the Power-Down Modes table: Deleted three paragraphs following table [Revision B]                                                           |

| 59             | IEEE 1149.1 JTAG Compatibility Statement section:<br>Updated/added paragraphs for clarity                                                                                                                                       |

| 60             | EMIF Device Speed section, Example Boards and Maximum EMIF Speed table:<br>Type – 3–Loads Short Traces, EMIF Interface Components section:<br>Updated <i>from</i> "32–Bit SDRAMs" <i>to</i> "16–Bit SDRAMs" <b>[Revision B]</b> |

| 63             | Recommended Operating Conditions:<br>Added $V_{OS}$ , Maximum voltage during overshoot row and associated footnote<br>Added $V_{US}$ , Maximum voltage during undershoot row and associated footnote                            |

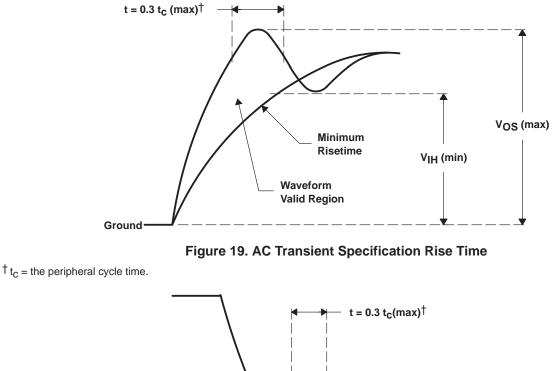

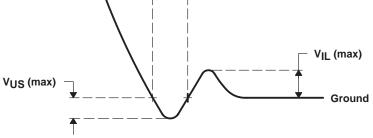

| 66             | Parameter Measurement Information:<br>AC transient rise/fall time specifications section:<br>Added AC Transient Specification Rise Time figure<br>Added AC Transient Specification Fall Time figure                             |

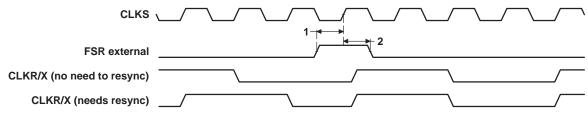

| 94             | MULTICHANNEL BUFFERED SERIAL PORT TIMING:<br>switching characteristics over recommended operating conditions for McBSP section:<br>Updated McBSP Timings figure for clarification                                               |

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

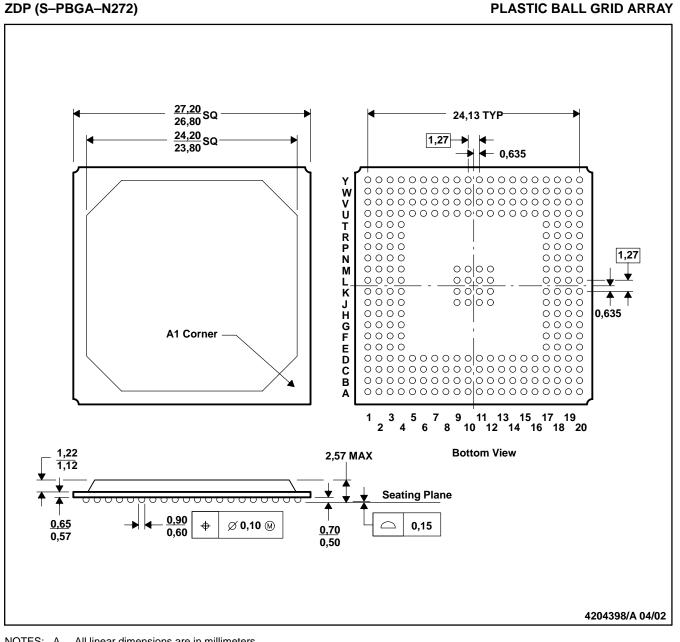

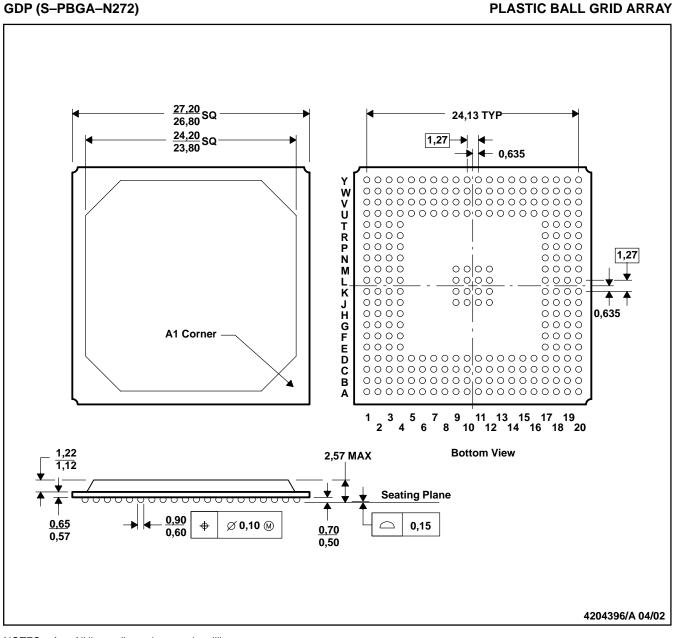

### GDP and ZDP BGA packages (bottom view)

0000 0000

GDP and ZDP 272-PIN BALL GRID ARRAY (BGA) PACKAGES<sup>†</sup> (BOTTOM VIEW)

| e ZDP mechanical package designator repre |                                         | 9 11 13 15 17 19<br>10 12 14 16 18 20<br>f the GDP package with lead-f | ree balls. For more detailed infr | orm |

|-------------------------------------------|-----------------------------------------|------------------------------------------------------------------------|-----------------------------------|-----|

| L<br>D<br>C<br>B<br>A                     | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000                                |                                   |     |

| E E                                       | 0000                                    | 0000                                                                   |                                   |     |

0000

0000

† The mation, see ıg ŀ the Mechanical Data section of this document.

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

#### description

The TMS320C67x<sup>™</sup> DSPs (including the TMS320C6711, TMS320C6711B, TMS320C6711C, TMS320C6711D devices<sup>†</sup>) compose the floating-point DSP family in the TMS320C6000<sup>™</sup> DSP platform. The C6711, C6711B, C6711C, and C6711D devices are based on the high-performance, advanced very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for multichannel and multifunction applications.

With performance of up to 1200 million floating-point operations per second (MFLOPS) at a clock rate of 200 MHz or up to 1500 MFLOPS at a clock rate of 250 MHz, the C6711D device also offers cost-effective solutions to high-performance DSP programming challenges. The C6711D DSP possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. This processor has 32 general-purpose registers of 32-bit word length and eight highly independent functional units. The eight functional units provide four floating-/fixed-point ALUs, two fixed-point ALUs, and two floating-/fixed-point multipliers. The C6711D can produce two MACs per cycle for a total of 400 MMACS.

The C6711D DSP also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals.

The C6711D device uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache (L1P) is a 32-Kbit direct mapped cache and the Level 1 data cache (L1D) is a 32-Kbit 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 512-Kbit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two. The peripheral set includes two multichannel buffered serial ports (McBSPs), two general-purpose timers, a host-port interface (HPI), and a glueless external memory interface (EMIF) capable of interfacing to SDRAM, SBSRAM and asynchronous peripherals.

The C6711D has a complete set of development tools which includes: a new C compiler, an assembly optimizer to simplify programming and scheduling, and a Windows<sup>™</sup> debugger interface for visibility into source code execution.

TMS320C6000 is a trademark of Texas Instruments.

Windows is a registered trademark of the Microsoft Corporation.

<sup>†</sup> Throughout the remainder of this document, the TMS320C6711D shall be referred to as its individual full device part number or abbreviated as C6711D or 11D.

#### device characteristics

Table 1 provides an overview of the C6711D DSP. The table shows significant features of the device, including the capacity of on-chip RAM, the peripherals, the execution time, and the package type with pin count. For more details on the C6000<sup>™</sup> DSP device part numbers and part numbering, see Figure 5.

| HARDWARE FEATU                                                                             | INTERNAL CLOCK<br>SOURCE              | C6711D<br>FLOATING-POINT DSP |                                                                                                                                    |

|--------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                            |                                       | ECLKIN                       |                                                                                                                                    |

|                                                                                            | EMIF                                  | SYSCLK3 or ECLKIN            | 1                                                                                                                                  |

|                                                                                            | EDMA                                  | CPU clock frequency          | 1                                                                                                                                  |

|                                                                                            |                                       | CPU/2 clock frequency        |                                                                                                                                    |

|                                                                                            | HPI                                   | SYSCLK2                      | 1                                                                                                                                  |

| Peripherals                                                                                |                                       | CPU/2 clock frequency        |                                                                                                                                    |

|                                                                                            | McBSPs                                | SYSCLK2                      | 2                                                                                                                                  |

|                                                                                            |                                       | CPU/4 clock frequency        | _                                                                                                                                  |

|                                                                                            | 32-Bit Timers                         | 1/2 of SYSCLK2               | 2                                                                                                                                  |

|                                                                                            | GPIO Module                           | SYSCLK2                      | 1                                                                                                                                  |

|                                                                                            | Size (Bytes)                          | •                            | 72K                                                                                                                                |

| On-Chip Memory                                                                             | Organization                          |                              | 4K-Byte (4KB) L1 Program<br>(L1P) Cache<br>4KB L1 Data (L1D) Cache<br>64KB Unified Mapped<br>RAM/Cache (L2)                        |

| CPU ID+<br>CPU Rev ID                                                                      | Control Status R                      | egister (CSR.[31:16])        | 0x0203                                                                                                                             |

| Frequency                                                                                  | MHz                                   |                              | 167, 200, 250                                                                                                                      |

| Cycle Time                                                                                 | ns                                    |                              | 4 ns (C6711DGDP-250)<br>5 ns (C6711DGDP-200<br>and C6711DZDP-200)<br>6 ns (C6711DGDP <b>A</b> -167<br>and C6711DZDP <b>A</b> -167) |

| Voltage                                                                                    | Core (V)                              |                              | 1.20 <sup>†</sup><br>1.4 (–250)                                                                                                    |

| -                                                                                          | I/O (V)                               | I/O (V)                      |                                                                                                                                    |

| PLL Options                                                                                | CLKIN frequency                       | / multiplier                 | -                                                                                                                                  |

| Clock Generator Options                                                                    | Prescaler<br>Multiplier<br>Postscaler |                              | /1, /2, /3,, /32<br>x4, x5, x6,, x25<br>/1, /2, /3,, /32                                                                           |

| BGA Package                                                                                | 27 x 27 mm                            |                              | 272-Pin BGA<br>(GDP and ZDP)§                                                                                                      |

| Process Technology                                                                         | μm                                    |                              | 0.13 μm                                                                                                                            |

| Product Status<br>Product Preview (PP)<br>Advance Information (AI)<br>Production Data (PD) |                                       |                              | PD‡                                                                                                                                |

#### Table 1. Characteristics of the C6711D Processor

<sup>†</sup>These values are compatible with existing 1.26–V designs.

<sup>‡</sup> PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

§ The ZDP package devices are supported in the same speed grades as the GDP package devices (available upon request).

C6000 is a trademark of Texas Instruments.

#### SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

#### device compatibility

The TMS320C6211/C6211B and C6711/C6711B devices are pin-compatible and have the same peripheral set; thus, making new system designs easier and providing faster time to market. The following list summarizes the device characteristic differences among the C6211, C6211B, C6711, C6711B, C6711C, and C6711D devices:

- The C6211 and C6211B devices have a fixed-point C62x CPU, while the C6711, C6711B, C6711C, and C6711D devices have a floating-point C67x CPU.

- The C6211/C6211B device runs at -167 and -150 MHz clock speeds (with a C6211BGFNA extended temperature device that also runs at -150 MHz), while the C6711/C6711B device runs at -150 and -100 MHz (with a C6711BGFNA extended temperature device that also runs at -100 MHz) and the C6711C and C6711D devices run at -200 clock speed (with a C6711CGDPA and C6711DGDPA extended temperature devices that also run at -167 MHz).

- The C6211/C6211B, C6711-100, and C6711B devices have a core voltage of 1.8 V, the C6711-150 device core voltage is 1.9 V, and the C6711C and C6711D devices operate with a core voltage of 1.20<sup>+</sup> V.

- There are several enhancements and features that are only available on the C6711C and C6711D devices, such as: the CLKOUT3 signal, a software programmable PLL and PLL Controller, and a GPIO peripheral module. The C6711D device also has additional enhancements such as: EMIF Big Endian mode correctness EMIFBE and the L1D requestor priority to L2 bit ["P" bit] in the cache configuration (CCFG) register.

For more detailed discussion on the migration of a C6211, C6211B, C6711, C6711B device to a TMS320C6711C device, see the *Migrating from TMS320C6211B/6711B to TMS320C6711C* application report (literature number SPRA837).

For a more detailed discussion on the similarities/differences between the C6211 and C6711 devices, see the *How to Begin Development Today with the TMS320C6211 DSP* and *How to Begin Development with the TMS320C6711 DSP* application reports (literature number SPRA474 and SPRA522, respectively).

<sup>†</sup>This value is compatible with existing 1.26V designs.

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

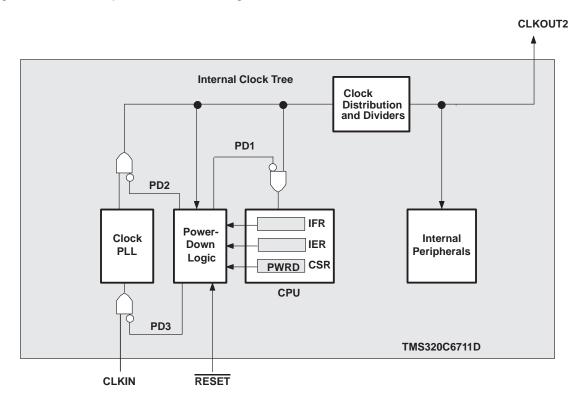

functional block and CPU (DSP core) diagram

<sup>†</sup> In addition to fixed-point instructions, these functional units execute floating-point instructions.

<sup>‡</sup> The device has a software-configurable PLL (with x4 through x25 multiplier and /1 through /32 divider).

#### SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

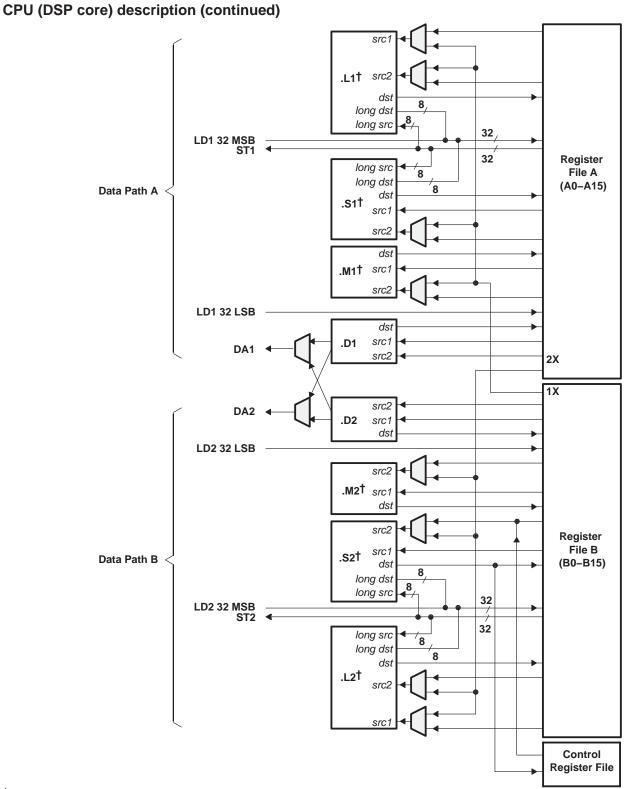

#### CPU (DSP core) description

The CPU fetches advanced very-long instruction words (VLIW) (256 bits wide) to supply up to eight 32-bit instructions to the eight functional units during every clock cycle. The VLIW architecture features controls by which all eight units do not have to be supplied with instructions if they are not ready to execute. The first bit of every 32-bit instruction determines if the next instruction belongs to the same execute packet as the previous instruction, or whether it should be executed in the following clock as a part of the next execute packet. Fetch packets are always 256 bits wide; however, the execute packets can vary in size. The variable-length execute packets are a key memory-saving feature, distinguishing the C67x CPU from other VLIW architectures.

The CPU features two sets of functional units. Each set contains four units and a register file. One set contains functional units .L1, .S1, .M1, and .D1; the other set contains units .D2, .M2, .S2, and .L2. The two register files each contain 16 32-bit registers for a total of 32 general-purpose registers. The two sets of functional units, along with two register files, compose sides A and B of the CPU (see the functional block and CPU diagram and Figure 1). The four functional units on each side of the CPU can freely share the 16 registers belonging to that side. Additionally, each side features a single data bus connected to all the registers on the other side, by which the two sets of functional units can access data from the register files on the opposite side. While register access by functional units on the same side of the CPU as the register file can service all the units in a single clock cycle, register access using the register file across the CPU supports one read and one write per cycle.

The C67x CPU executes all C62x instructions. In addition to C62x fixed-point instructions, the six out of eight functional units (.L1, .S1, .M1, .M2, .S2, and .L2) also execute floating-point instructions. The remaining two functional units (.D1 and .D2) also execute the new LDDW instruction which loads 64 bits per CPU side for a total of 128 bits per cycle.

Another key feature of the C67x CPU is the load/store architecture, where all instructions operate on registers (as opposed to data in memory). Two sets of data-addressing units (.D1 and .D2) are responsible for all data transfers between the register files and the memory. The data address driven by the .D units allows data addresses generated from one register file to be used to load or store data to or from the other register file. The C67x CPU supports a variety of indirect addressing modes using either linear- or circular-addressing modes with 5- or 15-bit offsets. All instructions are conditional, and most can access any one of the 32 registers. Some registers, however, are singled out to support specific addressing or to hold the condition for conditional instructions (if the condition is not automatically "true"). The two .M functional units are dedicated for multiplies. The two .S and .L functional units perform a general set of arithmetic, logical, and branch functions with results available every clock cycle.

The processing flow begins when a 256-bit-wide instruction fetch packet is fetched from a program memory. The 32-bit instructions destined for the individual functional units are "linked" together by "1" bits in the least significant bit (LSB) position of the instructions. The instructions that are "chained" together for simultaneous execution (up to eight in total) compose an execute packet. A "0" in the LSB of an instruction breaks the chain, effectively placing the instructions that follow it in the next execute packet. If an execute packet crosses the fetch-packet boundary (256 bits wide), the assembler places it in the next fetch packet, while the remainder of the current fetch packet is padded with NOP instructions. The number of execute packets within a fetch packet can vary from one to eight. Execute packets are dispatched to their respective functional units at the rate of one per clock cycle and the next 256-bit fetch packet is not fetched until all the execute packets from the current fetch packet have been dispatched. After decoding, the instructions simultaneously drive all active functional units for a maximum execution rate of eight instructions every clock cycle. While most results are stored in 32-bit registers, they can be subsequently moved to memory as bytes or half-words as well. All load and store instructions are byte-, half-word, or word-addressable.

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

<sup>†</sup> In addition to fixed-point instructions, these functional units execute floating-point instructions.

Figure 1. TMS320C67x<sup>™</sup> CPU (DSP Core) Data Paths

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

#### memory map summary

Table 2 shows the memory map address ranges of the device. Internal memory is always located at address 0 and can be used as both program and data memory. The configuration registers for the common peripherals are located at the same hex address ranges. The external memory address ranges in the device begin at the address location 0x8000 0000.

| MEMORY BLOCK DESCRIPTION                   | BLOCK SIZE (BYTES) | HEX ADDRESS RANGE     |

|--------------------------------------------|--------------------|-----------------------|

| Internal RAM (L2)                          | 64K                | 0000 0000 – 0000 FFFF |

| Reserved                                   | 24M – 64K          | 0001 0000 – 017F FFFF |

| External Memory Interface (EMIF) Registers | 256K               | 0180 0000 – 0183 FFFF |

| L2 Registers                               | 256K               | 0184 0000 – 0187 FFFF |

| HPI Registers                              | 256K               | 0188 0000 – 018B FFFF |

| McBSP 0 Registers                          | 256K               | 018C 0000 – 018F FFFF |

| McBSP 1 Registers                          | 256K               | 0190 0000 – 0193 FFFF |

| Timer 0 Registers                          | 256K               | 0194 0000 – 0197 FFFF |

| Timer 1 Registers                          | 256K               | 0198 0000 – 019B FFFF |

| Interrupt Selector Registers               | 512                | 019C 0000 - 019C 01FF |

| Device Configuration Registers             | 4                  | 019C 0200 - 019C 0203 |

| Reserved                                   | 256K – 516         | 019C 0204 – 019F FFFF |

| EDMA RAM and EDMA Registers                | 256K               | 01A0 0000 – 01A3 FFFF |

| Reserved                                   | 768K               | 01A4 0000 – 01AF FFFF |

| GPIO Registers                             | 16K                | 01B0 0000 – 01B0 3FFF |

| Reserved                                   | 480K               | 01B0 4000 – 01B7 BFFF |

| PLL Controller Registers                   | 8K                 | 01B7 C000 – 01B7 DFFF |

| Reserved                                   | 4M + 520K          | 01B7 E000 – 01FF FFFF |

| QDMA Registers                             | 52                 | 0200 0000 - 0200 0033 |

| Reserved                                   | 736M – 52          | 0200 0034 – 2FFF FFFF |

| McBSP 0 Data/Peripheral Data Bus           | 64M                | 3000 0000 – 33FF FFFF |

| McBSP 1 Data/Peripheral Data Bus           | 64M                | 3400 0000 – 37FF FFFF |

| Reserved                                   | 64M                | 3800 0000 – 3BFF FFFF |

| Reserved                                   | 1G + 64M           | 3C00 0000 – 7FFF FFFF |

| EMIF CE0 <sup>†</sup>                      | 256M               | 8000 0000 – 8FFF FFFF |

| EMIF CE1 <sup>†</sup>                      | 256M               | 9000 0000 – 9FFF FFFF |

| EMIF CE2 <sup>†</sup>                      | 256M               | A000 0000 – AFFF FFFF |

| EMIF CE3 <sup>†</sup>                      | 256M               | B000 0000 – BFFF FFFF |

| Reserved                                   | 1G                 | C000 0000 – FFFF FFFF |

#### Table 2. TMS320C6711D Memory Map Summary

<sup>†</sup> The number of EMIF address pins (EA[21:2]) limits the maximum addressable memory (SDRAM) to 128MB per CE space. To get 256MB of addressable memory, additional general-purpose output pin or external logic is required.

#### peripheral register descriptions

Table 3 through Table 14 identify the peripheral registers for the device by their register names, acronyms, and hex address or hex address range. For more detailed information on the register contents, bit names, and their descriptions, see the specific peripheral reference guide listed in the *TMS320C6000 DSP Peripherals Overview Reference Guide* (literature number SPRU190).

| HEX ADDRESS RANGE     | ACRONYM | REGISTER NAME              |

|-----------------------|---------|----------------------------|

| 0180 0000             | GBLCTL  | EMIF global control        |

| 0180 0004             | CECTL1  | EMIF CE1 space control     |

| 0180 0008             | CECTL0  | EMIF CE0 space control     |

| 0180 000C             | -       | Reserved                   |

| 0180 0010             | CECTL2  | EMIF CE2 space control     |

| 0180 0014             | CECTL3  | EMIF CE3 space control     |

| 0180 0018             | SDCTL   | EMIF SDRAM control         |

| 0180 001C             | SDTIM   | EMIF SDRAM refresh control |

| 0180 0020             | SDEXT   | EMIF SDRAM extension       |

| 0180 0024 – 0183 FFFF | -       | Reserved                   |

### Table 3. EMIF Registers

#### Table 4. L2 Cache Registers

| HEX ADDRESS RANGE     | ACRONYM  | REGISTER NAME                                  |  |

|-----------------------|----------|------------------------------------------------|--|

| 0184 0000             | CCFG     | Cache configuration register                   |  |

| 0184 4000             | L2WBAR   | L2 writeback base address register             |  |

| 0184 4004             | L2WWC    | L2 writeback word count register               |  |

| 0184 4010             | L2WIBAR  | L2 writeback-invalidate base address register  |  |

| 0184 4014             | L2WIWC   | L2 writeback-invalidate word count register    |  |

| 0184 4020             | L1PIBAR  | L1P invalidate base address register           |  |

| 0184 4024             | L1PIWC   | L1P invalidate word count register             |  |

| 0184 4030             | L1DWIBAR | L1D writeback-invalidate base address register |  |

| 0184 4034             | L1DWIWC  | L1D writeback-invalidate word count register   |  |

| 0184 5000             | L2WB     | L2 writeback all register                      |  |

| 0184 5004             | L2WBINV  | L2 writeback-invalidate all register           |  |

| 0184 8200             | MAR0     | Controls CE0 range 8000 0000 – 80FF FFFF       |  |

| 0184 8204             | MAR1     | Controls CE0 range 8100 0000 – 81FF FFFF       |  |

| 0184 8208             | MAR2     | Controls CE0 range 8200 0000 – 82FF FFFF       |  |

| 0184 820C             | MAR3     | Controls CE0 range 8300 0000 – 83FF FFFF       |  |

| 0184 8240             | MAR4     | Controls CE1 range 9000 0000 – 90FF FFFF       |  |

| 0184 8244             | MAR5     | Controls CE1 range 9100 0000 – 91FF FFFF       |  |

| 0184 8248             | MAR6     | Controls CE1 range 9200 0000 – 92FF FFFF       |  |

| 0184 824C             | MAR7     | Controls CE1 range 9300 0000 – 93FF FFFF       |  |

| 0184 8280             | MAR8     | Controls CE2 range A000 0000 – A0FF FFFF       |  |

| 0184 8284             | MAR9     | Controls CE2 range A100 0000 – A1FF FFFF       |  |

| 0184 8288             | MAR10    | Controls CE2 range A200 0000 – A2FF FFFF       |  |

| 0184 828C             | MAR11    | Controls CE2 range A300 0000 – A3FF FFFF       |  |

| 0184 82C0             | MAR12    | Controls CE3 range B000 0000 – B0FF FFFF       |  |

| 0184 82C4             | MAR13    | Controls CE3 range B100 0000 – B1FF FFFF       |  |

| 0184 82C8             | MAR14    | Controls CE3 range B200 0000 – B2FF FFFF       |  |

| 0184 82CC             | MAR15    | Controls CE3 range B300 0000 – B3FF FFFF       |  |

| 0184 82D0 – 0187 FFFF | -        | Reserved                                       |  |

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

### peripheral register descriptions (continued)

### Table 5. Interrupt Selector Registers

| HEX ADDRESS RANGE     | ACRONYM | REGISTER NAME               | COMMENTS                                                          |

|-----------------------|---------|-----------------------------|-------------------------------------------------------------------|

| 019C 0000             | MUXH    | Interrupt multiplexer high  | Selects which interrupts drive CPU interrupts 10–15 (INT10–INT15) |

| 019C 0004             | MUXL    | Interrupt multiplexer low   | Selects which interrupts drive CPU interrupts 4–9 (INT04–INT09)   |

| 019C 0008             | EXTPOL  | External interrupt polarity | Sets the polarity of the external interrupts (EXT_INT4-EXT_INT7)  |

| 019C 000C - 019F FFFF | -       | Reserved                    |                                                                   |

#### Table 6. Device Registers

| HEX ADDRESS RANGE     | ACRONYM | REGISTER DESCRIPTION        |                                                                                                                                                                                                                                                                                     |

|-----------------------|---------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 019C 0200             | DEVCFG  | Device Configuration        | This register allows the user control of the EMIF input clock source. For more detailed information on the device configuration register, see the Device Configurations section of this data sheet.                                                                                 |

| 019C 0204 – 019F FFFF | -       | Reserved                    |                                                                                                                                                                                                                                                                                     |

| N/A                   | CSR     | CPU Control Status Register | Identifies which CPU and defines the silicon revision of<br>the CPU. This register also offers the user control of<br>device operation.<br>For more detailed information on the CPU Control<br>Status Register, see the CPU CSR Register<br>Description section of this data sheet. |

#### Table 7. EDMA Parameter RAM<sup>†</sup>

| HEX ADDRESS RANGE      | ACRONYM | REGISTER NAME                                                               |

|------------------------|---------|-----------------------------------------------------------------------------|

| 01A0 0000 – 01A0 0017  | -       | Parameters for Event 0 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 0018 – 01A0 002F  | -       | Parameters for Event 1 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 0030 - 01A0 0047  | -       | Parameters for Event 2 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 0048 – 01A0 005F  | -       | Parameters for Event 3 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 0060 - 01A0 0077  | -       | Parameters for Event 4 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 0078 – 01A0 008F  | -       | Parameters for Event 5 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 0090 - 01A0 00A7  | -       | Parameters for Event 6 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 00A8 – 01A0 00BF  | -       | Parameters for Event 7 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 00C0 - 01A0 00D7  | -       | Parameters for Event 8 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 00D8 - 01A0 00EF  | -       | Parameters for Event 9 (6 words) or Reload/Link Parameters for other Event  |

| 01A0 00F0 - 01A0 00107 | _       | Parameters for Event 10 (6 words) or Reload/Link Parameters for other Event |

| 01A0 0108 – 01A0 011F  | -       | Parameters for Event 11 (6 words) or Reload/Link Parameters for other Event |

| 01A0 0120 - 01A0 0137  | -       | Parameters for Event 12 (6 words) or Reload/Link Parameters for other Event |

| 01A0 0138 – 01A0 014F  | -       | Parameters for Event 13 (6 words) or Reload/Link Parameters for other Event |

| 01A0 0150 – 01A0 0167  | -       | Parameters for Event 14 (6 words) or Reload/Link Parameters for other Event |

| 01A0 0168 – 01A0 017F  | -       | Parameters for Event 15 (6 words) or Reload/Link Parameters for other Event |

| 01A0 0180 – 01A0 0197  | _       | Reload/link parameters for Event 0–15                                       |

| 01A0 0198 – 01A0 01AF  | -       | Reload/link parameters for Event 0–15                                       |

|                        |         |                                                                             |

| 01A0 07E0 – 01A0 07F7  | -       | Reload/link parameters for Event 0–15                                       |

| 01A0 07F8 – 01A0 07FF  | _       | Scratch pad area (2 words)                                                  |

<sup>†</sup> The device has 85 EDMA parameters total: 16 Event/Reload parameters and 69 Reload-only parameters.

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

### peripheral register descriptions (continued)

For more details on the EDMA parameter RAM 6-word parameter entry structure, see Figure 2.

|        | 31                            |                        | 0   | EDMA Parameter |

|--------|-------------------------------|------------------------|-----|----------------|

| Word 0 | EDMA Channel Optic            |                        | OPT |                |

| Word 1 | EDMA Channel Sou              | Irce Address (SRC)     |     | SRC            |

| Word 2 | Array/Frame Count (FRMCNT)    |                        | CNT |                |

| Word 3 | EDMA Channel Desti            |                        | DST |                |

| Word 4 | Array/Frame Index (FRMIDX)    | Element Index (ELEIDX) |     | IDX            |

| Word 5 | Element Count Reload (ELERLD) | Link Address (LINK)    |     | RLD            |

### Figure 2. EDMA Channel Parameter Entries (6 Words) for Each EDMA Event

### Table 8. EDMA Registers

| HEX ADDRESS RANGE     | ACRONYM | REGISTER NAME                      |  |

|-----------------------|---------|------------------------------------|--|

| 01A0 0800 – 01A0 FEFC | -       | Reserved                           |  |

| 01A0 FF00             | ESEL0   | EDMA event selector 0              |  |

| 01A0 FF04             | ESEL1   | EDMA event selector 1              |  |

| 01A0 FF08 – 01A0 FF0B | -       | Reserved                           |  |

| 01A0 FF0C             | ESEL3   | EDMA event selector 3              |  |

| 01A0 FF1F - 01A0 FFDC | -       | Reserved                           |  |

| 01A0 FFE0             | PQSR    | Priority queue status register     |  |

| 01A0 FFE4             | CIPR    | Channel interrupt pending register |  |

| 01A0 FFE8             | CIER    | Channel interrupt enable register  |  |

| 01A0 FFEC             | CCER    | Channel chain enable register      |  |

| 01A0 FFF0             | ER      | Event register                     |  |

| 01A0 FFF4             | EER     | Event enable register              |  |

| 01A0 FFF8             | ECR     | Event clear register               |  |

| 01A0 FFFC             | ESR     | Event set register                 |  |

| 01A1 0000 – 01A3 FFFF | -       | Reserved                           |  |

#### Table 9. Quick DMA (QDMA) and Pseudo Registers<sup>†</sup>

| HEX ADDRESS RANGE     | ACRONYM | REGISTER NAME                            |  |

|-----------------------|---------|------------------------------------------|--|

| 0200 0000             | QOPT    | QDMA options parameter register          |  |

| 0200 0004             | QSRC    | QDMA source address register             |  |

| 0200 0008             | QCNT    | QDMA frame count register                |  |

| 0200 000C             | QDST    | QDMA destination address register        |  |

| 0200 0010             | QIDX    | QDMA index register                      |  |

| 0200 0014 - 0200 001C | -       | Reserved                                 |  |

| 0200 0020             | QSOPT   | QDMA pseudo options register             |  |

| 0200 0024             | QSSRC   | QDMA pseudo source address register      |  |

| 0200 0028             | QSCNT   | QDMA pseudo frame count register         |  |

| 0200 002C             | QSDST   | QDMA pseudo destination address register |  |

| 0200 0030             | QSIDX   | QDMA pseudo index register               |  |

<sup>†</sup> All the QDMA and Pseudo registers are write-accessible only

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

### peripheral register descriptions (continued)

### Table 10. PLL Controller Registers

| HEX ADDRESS RANGE     | ACRONYM | REGISTER NAME                                                            |

|-----------------------|---------|--------------------------------------------------------------------------|

| 01B7 C000             | PLLPID  | Peripheral identification register (PID) [0x00010801 for PLL Controller] |

| 01B7 C004 – 01B7 C0FF | -       | Reserved                                                                 |

| 01B7 C100             | PLLCSR  | PLL control/status register                                              |

| 01B7 C104 – 01B7 C10F | -       | Reserved                                                                 |

| 01B7 C110             | PLLM    | PLL multiplier control register                                          |

| 01B7 C114             | PLLDIV0 | PLL controller divider 0 register                                        |

| 01B7 C118             | PLLDIV1 | PLL controller divider 1 register                                        |

| 01B7 C11C             | PLLDIV2 | PLL controller divider 2 register                                        |

| 01B7 C120             | PLLDIV3 | PLL controller divider 3 register                                        |

| 01B7 C124             | OSCDIV1 | Oscillator divider 1 register                                            |

| 01B7 C128 – 01B7 DFFF | -       | Reserved                                                                 |

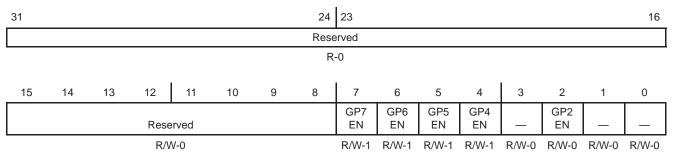

### Table 11. GPIO Registers

| HEX ADDRESS RANGE     | ACRONYM | REGISTER NAME                    |

|-----------------------|---------|----------------------------------|

| 01B0 0000             | GPEN    | GPIO enable register             |

| 01B0 0004             | GPDIR   | GPIO direction register          |

| 01B0 0008             | GPVAL   | GPIO value register              |

| 01B0 000C             | -       | Reserved                         |

| 01B0 0010             | GPDH    | GPIO delta high register         |

| 01B0 0014             | GPHM    | GPIO high mask register          |

| 01B0 0018             | GPDL    | GPIO delta low register          |

| 01B0 001C             | GPLM    | GPIO low mask register           |

| 01B0 0020             | GPGC    | GPIO global control register     |

| 01B0 0024             | GPPOL   | GPIO interrupt polarity register |

| 01B0 0028 – 01B0 3FFF | _       | Reserved                         |

#### Table 12. HPI Registers

| HEX ADDRESS RANGE                             | ACRONYM                   | REGISTER NAME        | COMMENTS                        |

|-----------------------------------------------|---------------------------|----------------------|---------------------------------|

| -                                             | HPID HPI data register He |                      | Host read/write access only     |

| <ul> <li>HPIA</li> <li>HPI address</li> </ul> |                           | HPI address register | Host read/write access only     |

| 0188 0000                                     | HPIC                      | HPI control register | Both Host/CPU read/write access |

| 0188 0001 – 018B FFFF                         | -                         | Reserved             |                                 |

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

# peripheral register descriptions (continued)

| HEX ADDRE             | ESS RANGE             | ACRONYM | REGISTER NAME            | COMMENTS                                                                                                                   |  |

|-----------------------|-----------------------|---------|--------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| TIMER 0               | TIMER 1               | ACRONTM | REGISTER NAME            | COMMENTS                                                                                                                   |  |

| 0194 0000 0198 0000   |                       | CTLx    | Timer x control register | Determines the operating<br>mode of the timer, monitors the<br>timer status, and controls the<br>function of the TOUT pin. |  |

| 0194 0004             | 0194 0004 0198 0004   |         | Timer x period register  | Contains the number of timer<br>input clock cycles to count.<br>This number controls the<br>TSTAT signal frequency.        |  |

| 0194 0008 0198 0008   |                       | CNTx    | Timer x counter register | Contains the current value of the incrementing counter.                                                                    |  |

| 0194 000C – 0197 FFFF | 0198 000C – 019B FFFF | -       | Reserved                 | -                                                                                                                          |  |

### Table 13. Timer 0 and Timer 1 Registers

### Table 14. McBSP0 and McBSP1 Registers

| HEX ADDR              | ESS RANGE             |         |                                                                                                                                            |  |

|-----------------------|-----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| McBSP0                | McBSP1                | ACRONYM | REGISTER DESCRIPTION                                                                                                                       |  |

| 018C 0000             | 0190 0000             | DRRx    | McBSPx data receive register via Configuration Bus<br>The CPU and EDMA controller can only read this register;<br>they cannot write to it. |  |

| 3000 0000 – 33FF FFFF | 3400 0000 – 37FF FFFF | DRRx    | McBSPx data receive register via Peripheral Data Bus                                                                                       |  |

| 018C 0004             | 0190 0004             | DXRx    | McBSPx data transmit register via Configuration Bus                                                                                        |  |

| 3000 0000 – 33FF FFFF | 3400 0000 – 37FF FFFF | DXRx    | McBSPx data transmit register via Peripheral Data Bus                                                                                      |  |

| 018C 0008             | 0190 0008             | SPCRx   | McBSPx serial port control register                                                                                                        |  |

| 018C 000C             | 0190 000C             | RCRx    | McBSPx receive control register                                                                                                            |  |

| 018C 0010             | 0190 0010             | XCRx    | McBSPx transmit control register                                                                                                           |  |

| 018C 0014             | 0190 0014             | SRGRx   | McBSPx sample rate generator register                                                                                                      |  |

| 018C 0018             | 0190 0018             | MCRx    | McBSPx multichannel control register                                                                                                       |  |

| 018C 001C             | 0190 001C             | RCERx   | McBSPx receive channel enable register                                                                                                     |  |

| 018C 0020             | 0190 0020             | XCERx   | McBSPx transmit channel enable register                                                                                                    |  |

| 018C 0024             | 0190 0024             | PCRx    | McBSPx pin control register                                                                                                                |  |

| 018C 0028 – 018F FFFF | 0190 0028 – 0193 FFFF | -       | Reserved                                                                                                                                   |  |

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

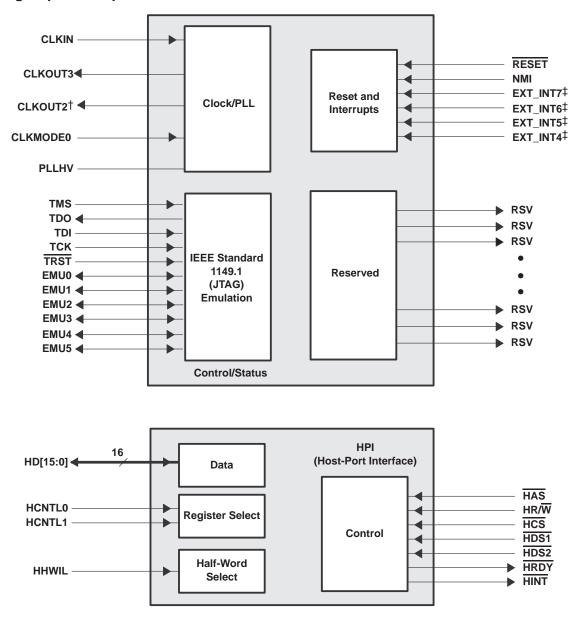

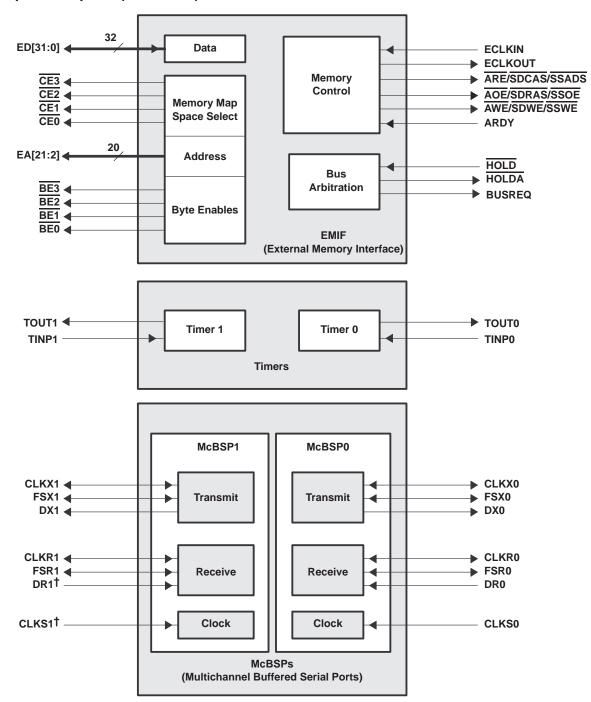

### signal groups description

<sup>†</sup> For this device, the CLKOUT2 pin is multiplexed with the GP[2] pin. Default function is CLKOUT2. To use this pin as GPIO, the GP2EN bit in the GPEN register and the GP2DIR bit in the GPDIR register must be properly configured.

<sup>‡</sup> For this device, the external interrupts (EXT\_INT[7–4]) go through the general-purpose input/output (GPIO) module. When used as interrupt inputs, the GP[7–4] pins must be configured as inputs (via the GPDIR register) and enabled (via the GPEN register) in addition to enabling the interrupts in the interrupt enable register (IER).

#### Figure 3. CPU (DSP Core) and Peripheral Signals

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

#### signal groups description (continued)

<sup>†</sup> For proper device operation, these pins must be externally pulled up with a 10-k $\Omega$  resistor.

**Figure 4. Peripheral Signals**

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

### signal groups description (continued)

Figure 4. Peripheral Signals (Continued)

### **DEVICE CONFIGURATIONS**

On this device, bootmode and certain device configurations/peripheral selections are determined at device reset. Also, other device configurations (e.g., EMIF input clock source) are software-configurable via the device configurations register (DEVCFG) [address location 0x019C0200] after device reset.

#### device configurations at device reset

Table 15 describes the C6711D device configuration pins, which are set up via internal or external pullup/pulldown resistors through the HPI data pins (HD[4:3], HD8, HD12) and CLKMODE0 pin. These configuration pins must be in the desired state until reset is released.

For proper device operation, *do not* oppose the HD [14, 13, 11:9, 7, 1, 0] pins with external pull–ups/pulldowns at reset.

For more details on these device configuration pins, see the Terminal Functions table of this data sheet.

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

### Table 15. Device Configurations Pins at Device Reset (HD[4:3], HD8, HD12, and CLKMODE0)<sup>†</sup>

| CONFIGURATION<br>PIN                                                                                                                                                                                                                                                 | GDP/ZDP  | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HD12‡                                                                                                                                                                                                                                                                | C15      | <ul> <li>EMIF Big Endian mode correctness (EMIFBE)</li> <li>0 - The EMIF data will always be presented on the ED[7:0] side of the bus, regardless of the endianess mode (Little/Big Endian).</li> <li>1 - In Little Endian mode (HD8 =1), the 8-bit or 16-bit EMIF data will be present on the ED[7:0] side of the bus.<br/>In Big Endian mode (HD8 =0), the 8-bit or 16-bit EMIF data will be present on the ED[31:24] side of the bus [default].</li> <li>EMIF Big Endian mode correctness is <i>not</i> supported on the C6711/11B/11C device.<br/>This new functionality does <i>not</i> affect systems using the current default value of HD12=1. For more detailed information on the big endian mode correctness, see the <i>EMIF Big Endian Mode Correctness</i> portion of this data sheet.</li> </ul> |  |  |

| HD8‡                                                                                                                                                                                                                                                                 | B17      | Device Endian mode (LEND)<br>0 – System operates in Big Endian mode<br>1 – System operates in Little Endian mode (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| HD[4:3]<br>(BOOTMODE)‡                                                                                                                                                                                                                                               | C19, C20 | Bootmode Configuration Pins (BOOTMODE)         00 -       HPI boot/Emulation boot         01 -       CE1 width 8-bit, Asynchronous external ROM boot with default         timings (default mode)         10 -       CE1 width 16-bit, Asynchronous external ROM boot with default         timings         11 -       CE1 width 32-bit, Asynchronous external ROM boot with default         timings         11 -       CE1 width 32-bit, Asynchronous external ROM boot with default         timings         For more detailed information on these bootmode configurations, see the <i>bootmode</i> section of this data sheet.                                                                                                                                                                                 |  |  |

| CLKMODE0       C4       Clock generator input clock source select         0       – Reserved. Do not use.         1       – CLKIN square wave [default]         For proper device operation, this pin must be either left unconnected or exter with a 1-kΩ resistor. |          | <ul> <li>0 – Reserved. Do not use.</li> <li>1 – CLKIN square wave [default]</li> <li>For proper device operation, this pin must be either left unconnected or externally pulled up</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

<sup>†</sup> All other HD pins *or* HD [15:13, 11:9, 7:5, 2:0] have pullups/pulldowns (IPUs or IPDs). For proper device operation, *do not* oppose the HD [14, 13, 11:9, 7, 1, 0] pins with external pull–ups/pulldowns at reset; however, the HD[15, 6, 5, 2] pins *can* be opposed and driven during reset.

<sup>‡</sup> To ensure a proper logic level during reset when these pins are *both* routed out *and* 3–stated or not driven, it is recommended an external 10-kΩ pullup/pulldown resistor be included to sustain the IPU/IPD, respectively.

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

## **DEVICE CONFIGURATIONS (CONTINUED)**

### **DEVCFG** register description

The device configuration register (DEVCFG) allows the user control of the EMIF input clock source for the device. For more detailed information on the DEVCFG register control bits, see Table 16 and Table 17.

### Table 16. Device Configuration Register (DEVCFG) [Address location: 0x019C0200 – 0x019C02FF]

| 31                    |  |       |                       |       |                       | 16 |

|-----------------------|--|-------|-----------------------|-------|-----------------------|----|

|                       |  |       | Reserved <sup>†</sup> |       |                       |    |

|                       |  |       | RW-0                  |       |                       |    |

| 15                    |  | 5     | 4                     | 3     |                       | 0  |

| Reserved <sup>†</sup> |  | -     | EKSRC                 |       | Reserved <sup>†</sup> |    |

| RW-0                  |  | R/W-0 |                       | R/W-0 |                       |    |

**Legend:** R/W = Read/Write; -n = value after reset

† Do not write non-zero values to these bit locations.

#### Table 17. Device Configuration (DEVCFG) Register Selection Bit Descriptions

| BIT # | NAME     | DESCRIPTION                                                                                                                                                                                                                                                                       |  |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:5  | Reserved | Reserved. Do not write non-zero values to these bit locations.                                                                                                                                                                                                                    |  |

| 4     | EKSRC    | <ul> <li>EMIF input clock source bit.</li> <li>Determines which clock signal is used as the EMIF input clock.</li> <li>0 = SYSCLK3 (from the clock generator) is the EMIF input clock source (default)</li> <li>1 = ECLKIN external pin is the EMIF input clock source</li> </ul> |  |

| 3:0   | Reserved | Reserved. <i>Do not</i> write non-zero values to these bit locations.                                                                                                                                                                                                             |  |

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

### **TERMINAL FUNCTIONS**

The terminal functions table identifies the external signal names, the associated pin (ball) numbers along with the mechanical package designator, the pin type (I, O/Z, or I/O/Z), whether the pin has any internal pullup/pulldown resistors and a functional pin description. For more detailed information on device configuration, see the Device Configurations section of this data sheet.

SPRS292B - OCTOBER 2005 - REVISED JUNE 2006

|                      |                           |       |              | Terminal Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|----------------------|---------------------------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SIGNAL<br>NAME       | PIN<br>NO.<br>GDP/<br>ZDP | TYPET | IPD/<br>IPU‡ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      |                           |       |              | CLOCK/PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CLKIN                | A3                        | I     | IPD          | Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CLKOUT2<br>(/GP0[2]) | Y12                       | O/Z   | IPD          | For this device, the CLKOUT2 pin is multiplexed with the GP[2] pin.<br>Clock output at half of device speed ( <b>O</b> / <b>Z</b> ) [default] (SYSCLK2 internal signal from the clock<br>generator) or this pin can be programmed as GP[2] (I/O/Z).<br>When the CLKOUT2 pin is enabled, the CLK2EN bit in the EMIF global control register<br>(GBLCTL) controls the CLKOUT2 pin (All devices).<br>CLK2EN = 0: CLKOUT2 is disabled<br>CLK2EN = 1: CLKOUT2 enabled to clock [default] |  |

| CLKOUT3              | D10                       | 0     | IPD          | Clock output programmable by OSCDIV1 register in the PLL controller.                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| CLKMODE0             | C4                        | I     | IPU          | Clock generator input clock source select<br>0 – Reserved. Do not use.<br>1 – CLKIN square wave [default]<br>For proper device operation, this pin must be either left unconnected or externally pulled up with<br>a 1-kΩ resistor.                                                                                                                                                                                                                                                 |  |

| PLLHV                | C5                        | А     |              | Analog power (3.3 V) for PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                      |                           |       |              | JTAG EMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| TMS                  | B7                        | I     | IPU          | JTAG test-port mode select                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |