# **Microcomputer Components**

SAB 80C517A/83C517A-5 8-Bit CMOS Single-Chip Microcontroller

Addendum to User's Manual SAB 80C517/80C537 05.94

#### Edition 05.94

This edition was realized using the software system FrameMaker<sup>®</sup>.

#### Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1994.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

|                                                                                                       | 7A/83C517A-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision His                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Previous Ver                                                                                          | sion: 11.92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Page                                                                                                  | Subjects (major changes since last revision 11.92)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 3-8<br>4-1<br>5-3<br>5-10/5-11                                                                        | SORELL adresses corrected<br>$\overline{\text{HWPD}}$ pin number corrected<br>$T_{\text{S}}/T_{\text{C}}$ in table 5-1 corrected<br>CC4EN bit names and table 5-3 corrected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Device Spec<br>Revision His                                                                           | cifications SAB 80C517A/83C517A-5<br>story: 05.94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Previous Rel                                                                                          | eases: 01.94/08.93/11.92/10.91/04.91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Page                                                                                                  | Subjects (changes since last revision 04.91)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

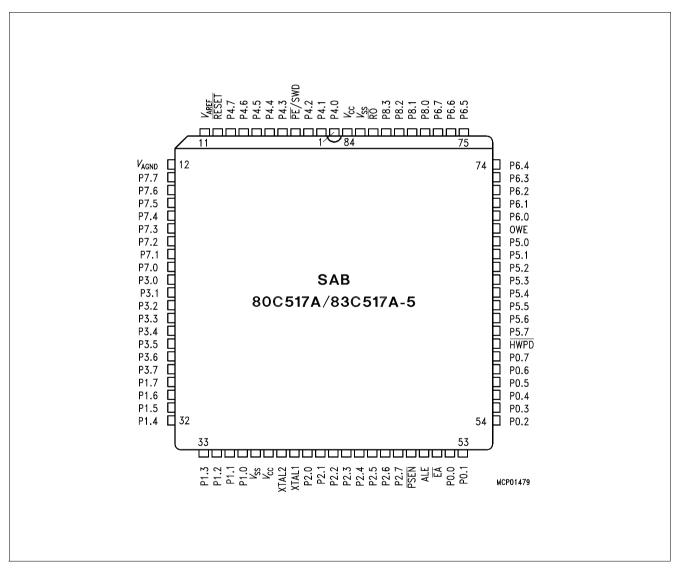

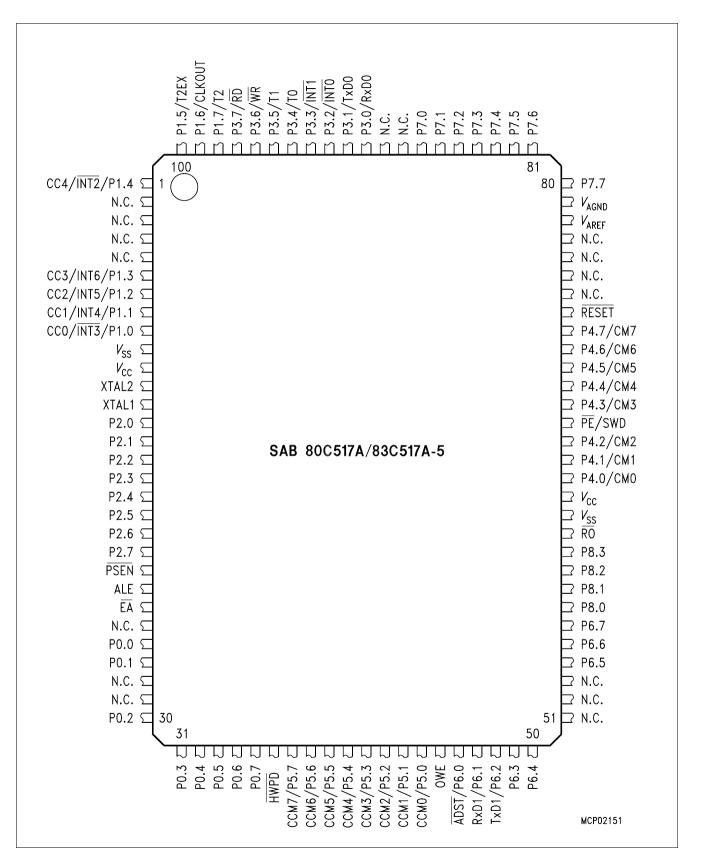

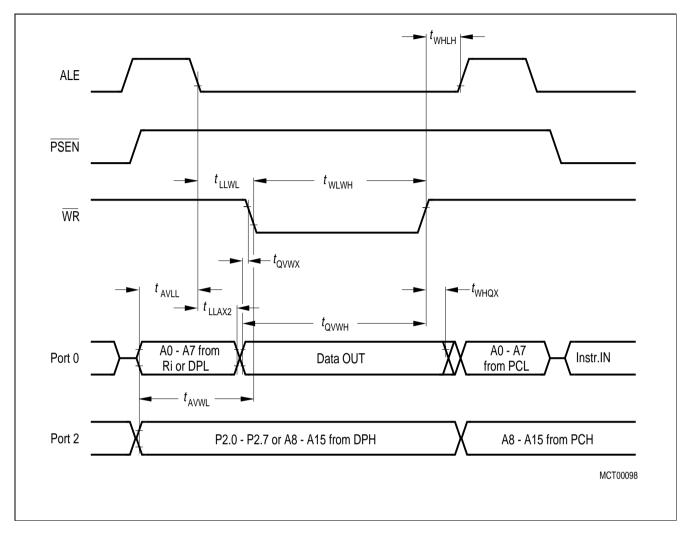

| 5<br>4<br>6-14<br>several<br>2<br>25,26,30<br>33<br>39<br>57<br>60<br>62<br>65<br>several<br>66<br>68 | Pin configuration P-MQFP-100-2 added<br>Pin differences updated<br>Pin numbers for P-MQFP-100-2 package added<br>Correction of P-MRFP-100 into P-MQFP-100-2<br>Ordering information for – 40 to + 110 °C versions<br>Correction of register names SORELL, SCON, ADCON, ICRON and SBUF<br>Figure 4 corrected<br>Figure 8 corrected<br>PE/SWD function description completed<br>Correct ordering numbers<br>Test condition for $V_{OH}$ , $V_{OH1}$ corrected<br>$t_{PXIZ}$ name corrected<br>$t_{AVIV}$ , $t_{AZPL}$ values corrected<br>Minimum clock frequence is now 3.5 MHz<br>$t_{QVWH}$ (data setup before $\overline{WR}$ ) corrected and added<br>$t_{LLAX2}$ corrected |  |  |

| Page                                                                                                  | Subjects (changes since last version 08.93)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

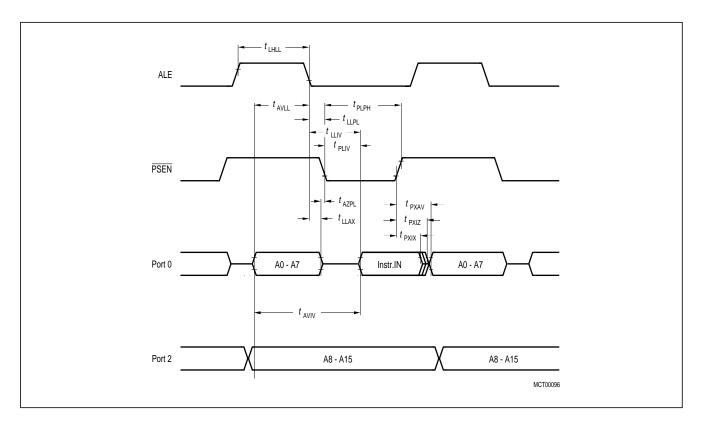

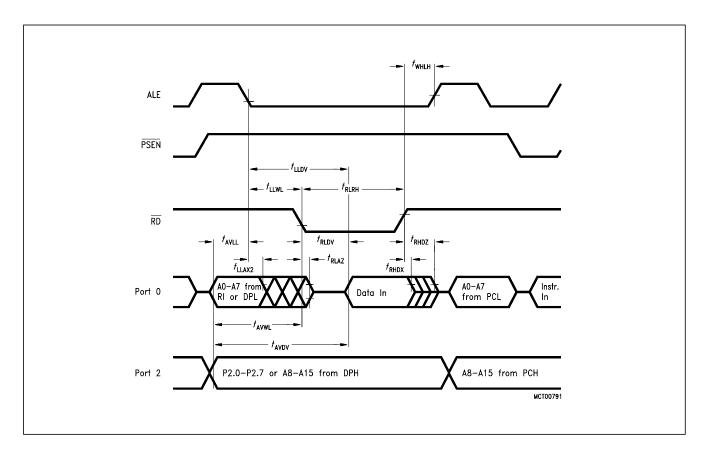

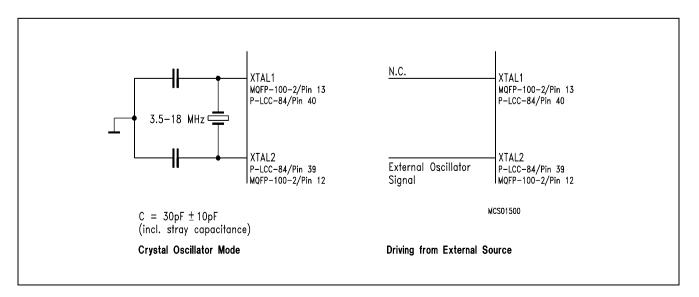

| 25<br>51<br>65<br>67<br>74                                                                            | Corrected SFR name S0RELL<br>Below "Termination of HWPD Mode": 4th paragraph with ident corrected<br>Description of $t_{LLIV}$ corrected<br>Program Memory Read Cycle: $f_{PXAV}$ added<br>Oscillator circuit drawings: MQFP-100-2 pin numbers added.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Page                                                                                                  | Subjects (changes since last revision 01.94)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 47                                                                                                    | Minor changes on several pages<br>Table 6 corrected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Conten                                                          | ts Pa                                                                                                                                                                                                                                                                                                                 | ge                                    |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 1                                                               | Introduction1                                                                                                                                                                                                                                                                                                         | -1                                    |

| 2                                                               | Fundamental Structure2                                                                                                                                                                                                                                                                                                | !-1                                   |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3 | Memory Organization3Program Memory, ROM Protection3Data Memory3Special Function Registers3Architecture for the XRAM3Accesses to XRAM3Control of XRAM in the SAB 80C517A3-Behaviour of Port0 and Port23-                                                                                                               | 8-2<br>8-3<br>8-4<br>8-9<br>8-9<br>15 |

| <b>4</b><br>4.1<br>4.2<br>4.3                                   | System Reset       4         Additional Hardware Power Down Mode in the SAB 80C517A       4         Hardware Power Down Reset Timing       4         Fast internal Reset after Power-On       4                                                                                                                       | ŀ-1<br>⊦-4                            |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.5   | On-Chip Peripheral Components5Digital I/O Port Circuitry510-bit A/D-Converter5Additional Compare Mode for the Concurrent Compare Unit5New Baud Rate Generators for Serial Channel 0 and Serial Channel 15Serial Channel 0 Baud Rate Generator5Serial Channel 1 Baud Rate Generator5Modified Oscillator Watchdog Unit5 | 5-1<br>5-3<br>5-8<br>14<br>14<br>17   |

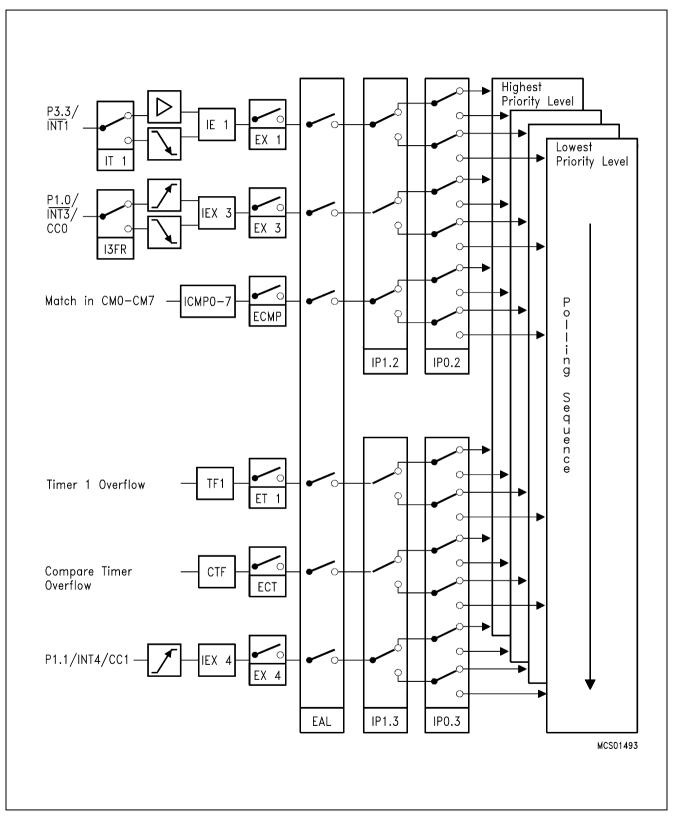

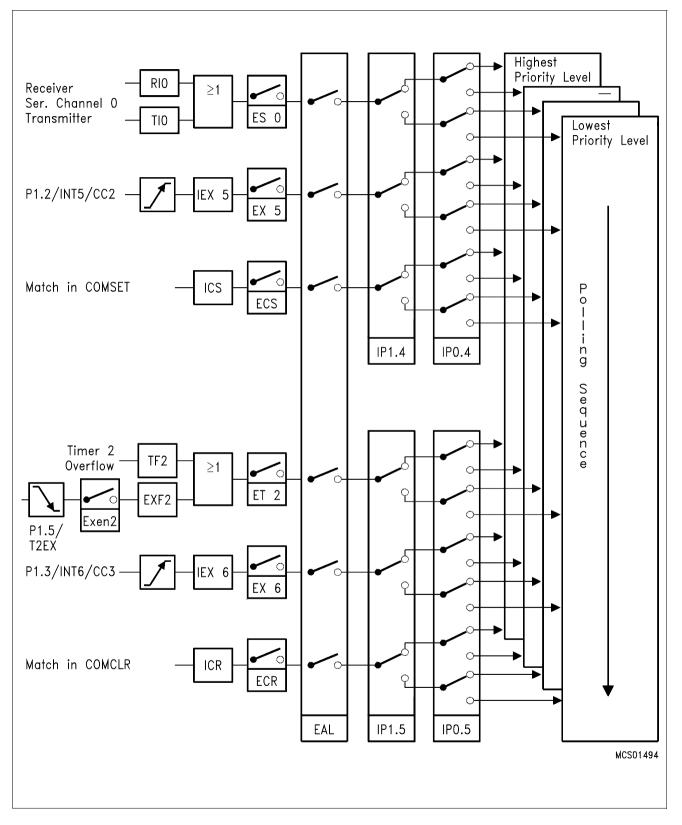

| <b>6</b><br>6.1<br>6.2<br>6.3                                   | Interrupt System       6         Additional Interrupt for Compare Registers CM0 to CM7       6         Interrupt Structure       6         Priority Level Structure       6                                                                                                                                           | 6-1<br>6-4                            |

| 7                                                               | Device Specification7                                                                                                                                                                                                                                                                                                 | '-1                                   |

# 1 Introduction

The SAB 80C517A is a superset of the high end microcontroller SAB 80C517.

While maintaining all architectural and operational characteristics of the SAB 80C517 the SAB 80C517A incorporates more on-chip RAM as well as some enhancements in the compare / capture unit. The oscillator watchdog got an improved functionality. Also the operating frequency is higher than that of the SAB 80C517.

#### SAB 80C517A / 83C517A-5

In this manual, any reference made to the SAB 80C517A applies to both versions, the SAB 80C517A and the SAB 83C517A-5, unless otherwise noted. Furthermore only new features of the SAB 80C517A in addition to the features of the SAB 80C517A/83C517A-5 are described. For additional reference, the user's manual of the SAB 80C517/80C537 (Ord. No. B258-H6075-G1-X-7600) should be used.

Listed below is a summary of the main features of the SAB 80C517A:

- SAB 80C517A/83C517A-5, up to 18 MHz operation frequency

- 32 K×8 ROM (SAB 83C517A-5 only, ROM-Protection available)

- 256×8 on-chip RAM

- 2K×8 on-chip RAM (XRAM)

- Superset of SAB 80C51 architecture:

- $-1 \,\mu s$  instruction cycle time at 12 MHz

- 666 ns instruction cycle time at 18 MHz

- 256 directly addressable bits

- Boolean processor

- 64 Kbyte external data and program memory addressing

- Four 16-bit timer/counters

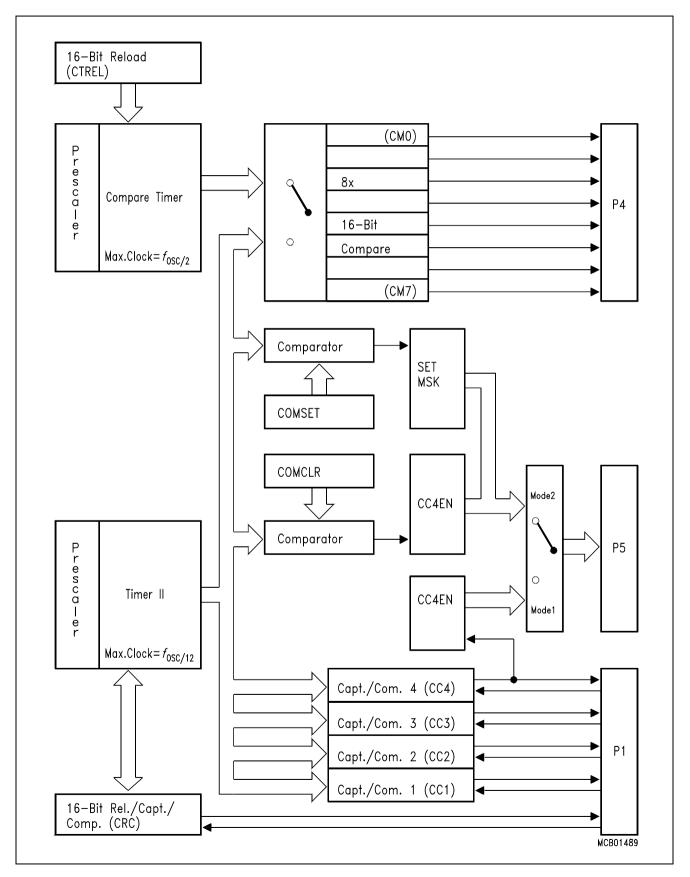

- Powerful 16-bit compare/capture unit (CCU) with up to 21 high-speed or PWM output channels and 5 capture inputs

- Versatile "fail-safe" provisions

- Fast 32-bit division, 16-bit multiplication, 32bit normalize and shift by peripheral MUL/ DIV unit (MDU)

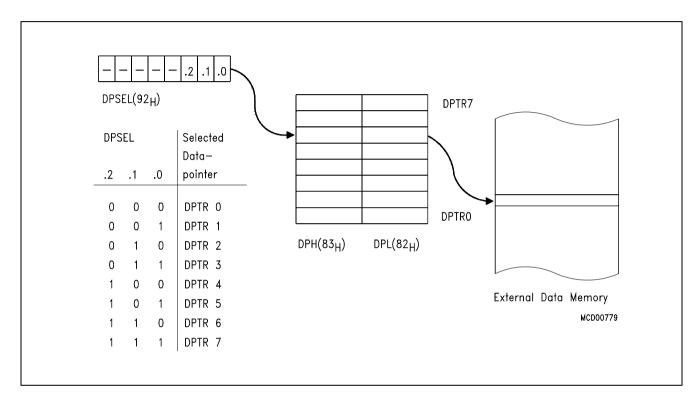

- Eight data pointers for external memory addressing

- Seventeen interrupt vectors, four priority levels selectable

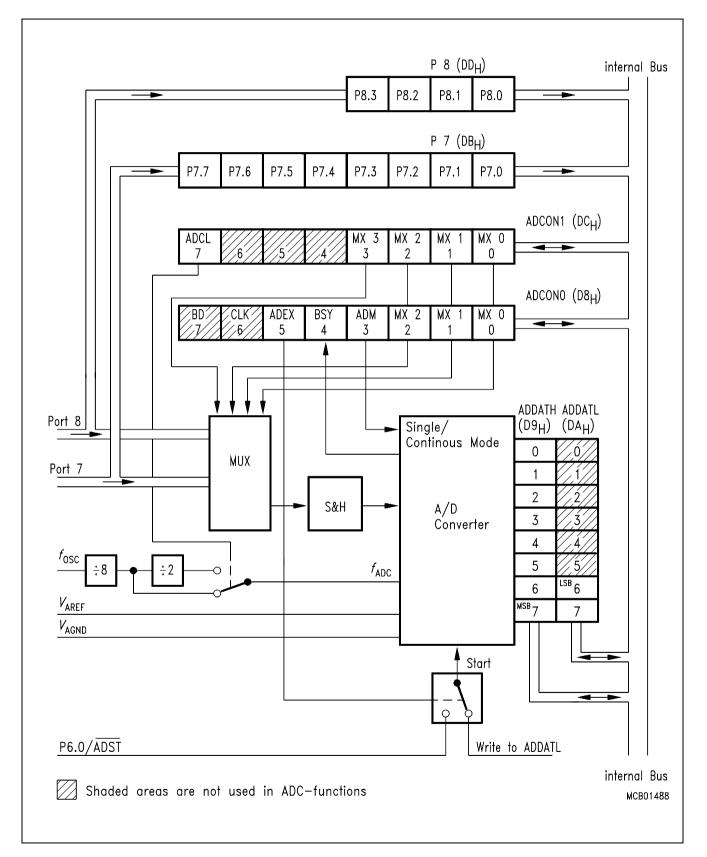

- genuine 10-bit A/D converter with 12 multiplexed inputs

- Two full duplex serial interfaces with programmable Baudrate-Generators

- Fully upward compatible with SAB 80C515, SAB 80C517, SAB 80C515A

- Extended power saving modes

- Fast Power-On Reset

- Nine ports: 56 I/O lines, 12 input lines

- Three temperature ranges available: 0 to 70 °C (T1)

- $-40 \text{ to } + 85 \,^{\circ}\text{C}$  (T3)

- $-40 \text{ to } + 110 ^{\circ}\text{C}$  (T4)

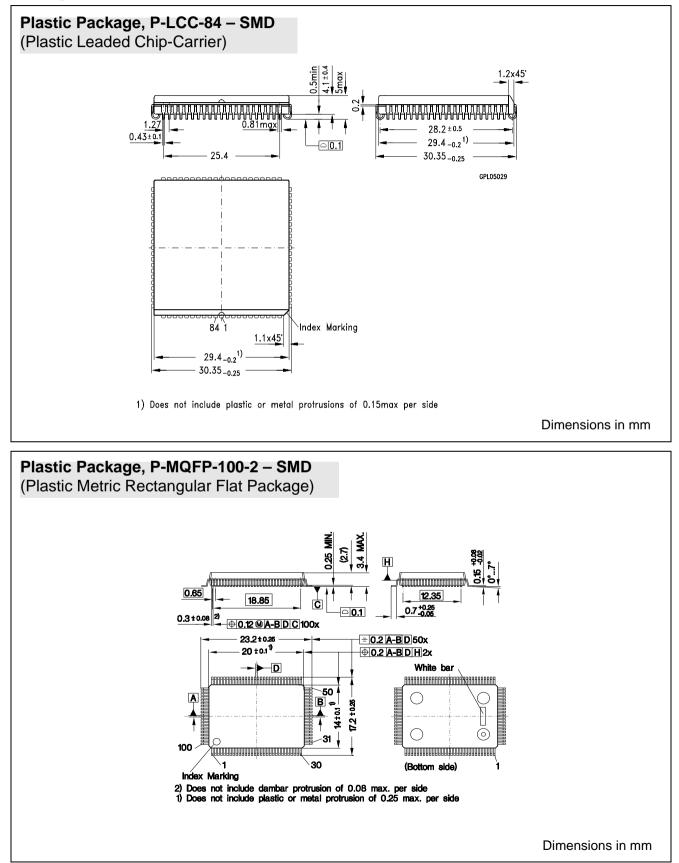

- Plastic packages: P-LCC-84

P-MQFP-100-2

The pin functions of the SAB 80C517A are identical with those of the SAB 80C517/80C537 with one exception:

| Package      | SAB 80C517A | SAB 80C517 / 80C537 |

|--------------|-------------|---------------------|

| PLCC-84/60   |             |                     |

|              | HWPD        | V <sub>SS</sub>     |

| PMRFP-100/72 |             |                     |

#### 2 Fundamental Structure

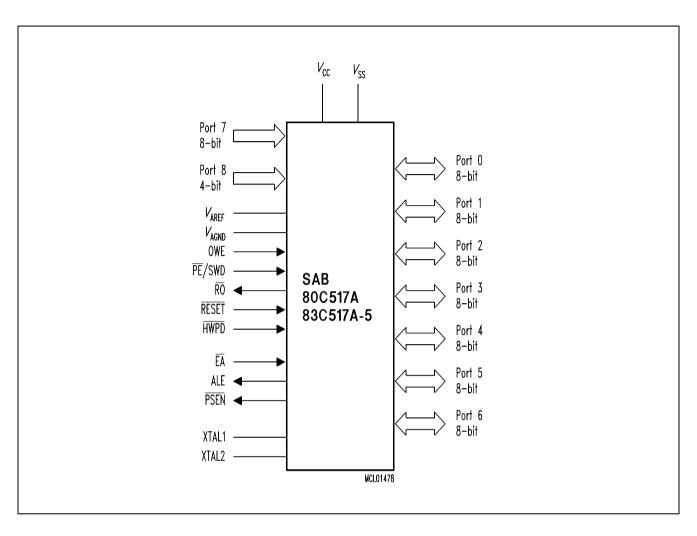

The SAB 80C517A/83C517A-5 is a high-end member of the Siemens SAB 8051 family of microcontrollers. It is designed in Siemens ACMOS technology and based on the SAB 8051 architecture. ACMOS is a technology which combines high-speed and density characteristics with low-power consumption or dissipation.

While maintaining all the SAB 80C517 features and operating characteristics the SAB 80C517A is expanded in its "fail-safe" characteristics and timer capabilities.

Furthermore, the SAB 80C517A additionally contains 2 kByte of on-chip RAM (called XRAM), a 10bit A/D converter with 12 multiplexed inputs, enhanced Baud Rate Generators and the capabilities of the Compare Capture Unit are improved.

The SAB 80C517A is identical with the SAB 83C517A-5 except that it lacks the on-chip program memory. The SAB 80C517A / 83C517A-5 is supplied in a 84-pin plastic leaded chip carrier package (P-LCC-84) and in a 100-pin plastic metric rectangular flat package (P-MRFP-100).

The essential enhancements to the SAB 80C517 are:

- Additional 2KByte RAM on chip.

- 32 kByte on-chip program memory (SAB 83C517A-5 only)

- 12-channel 10-bit A/D Converter

- Additional Compare Mode for Concurrent Compare function at Port 5; up to eight pins on P5 can be either set or reset on a compare match in two additional compare registers.

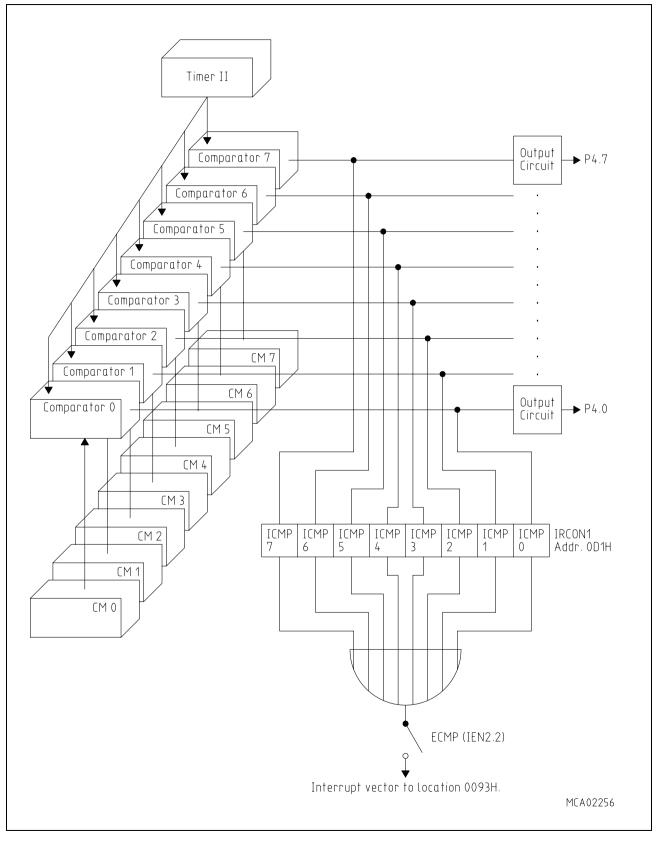

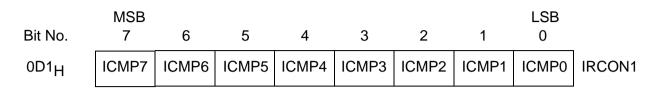

- Dedicated interrupt vector for the 16-bit compare registers CM0-CM7: Interrupt requested on a compare match in one of the eight compare channels (eight request flags are available)

- New baud rate generator for Serial Channel 0

- Expanded baud rate range for Serial Channel 1

- Hardware controlled Power Down Mode

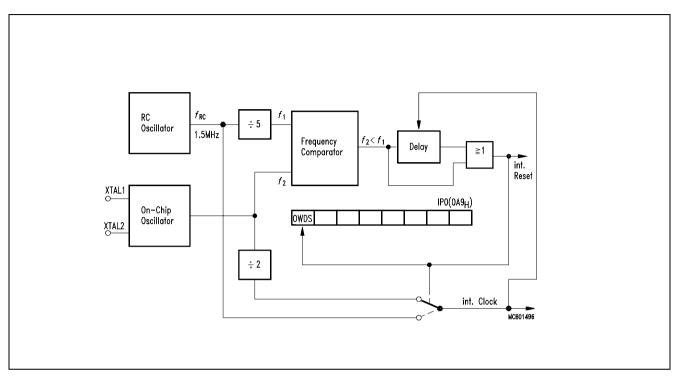

- Improved functionality of the Oscillator Watchdog

- High speed operation of the device (up to 18 MHz crystal frequency)

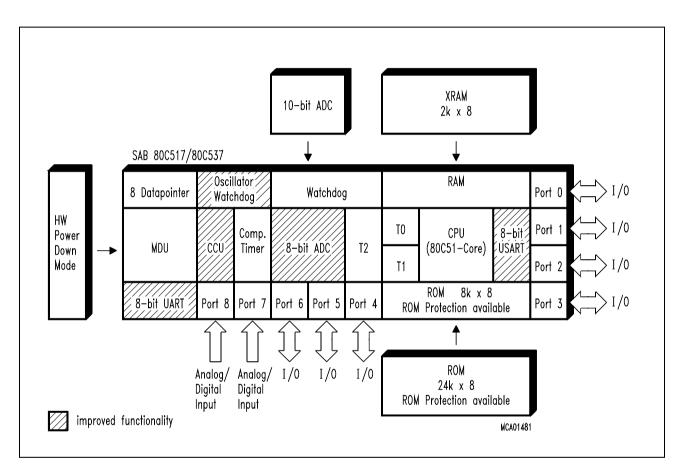

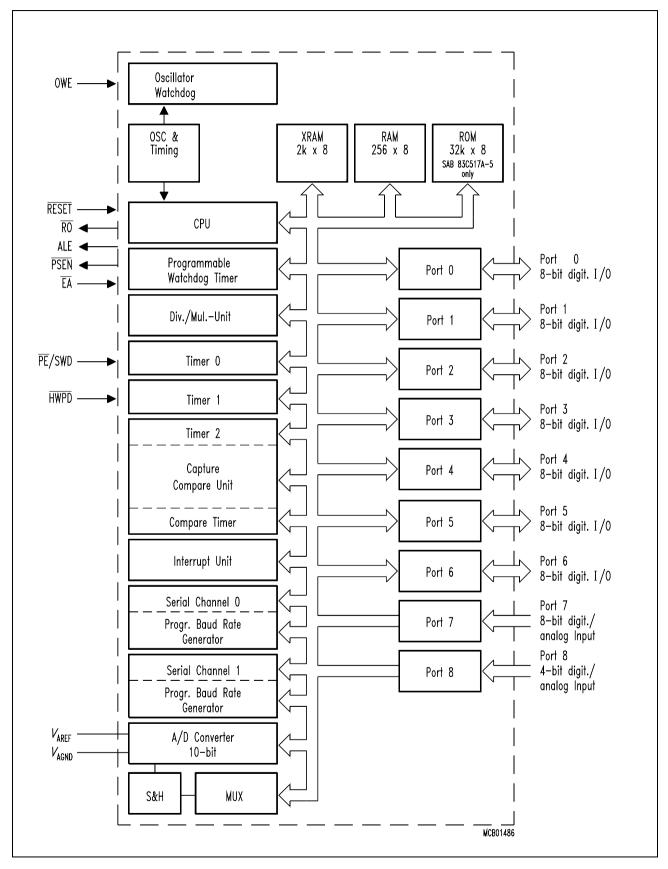

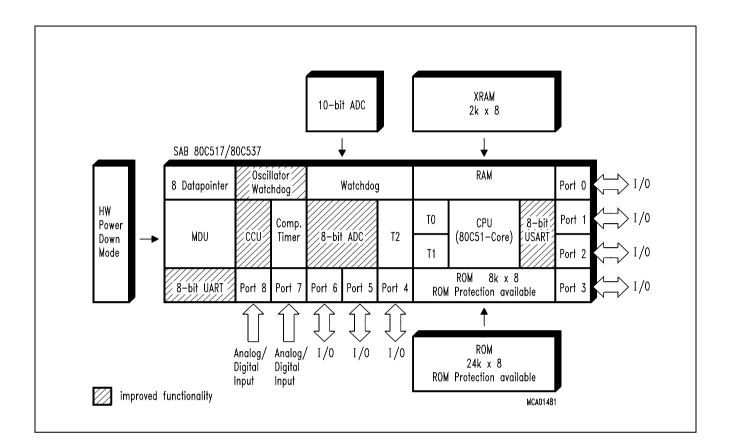

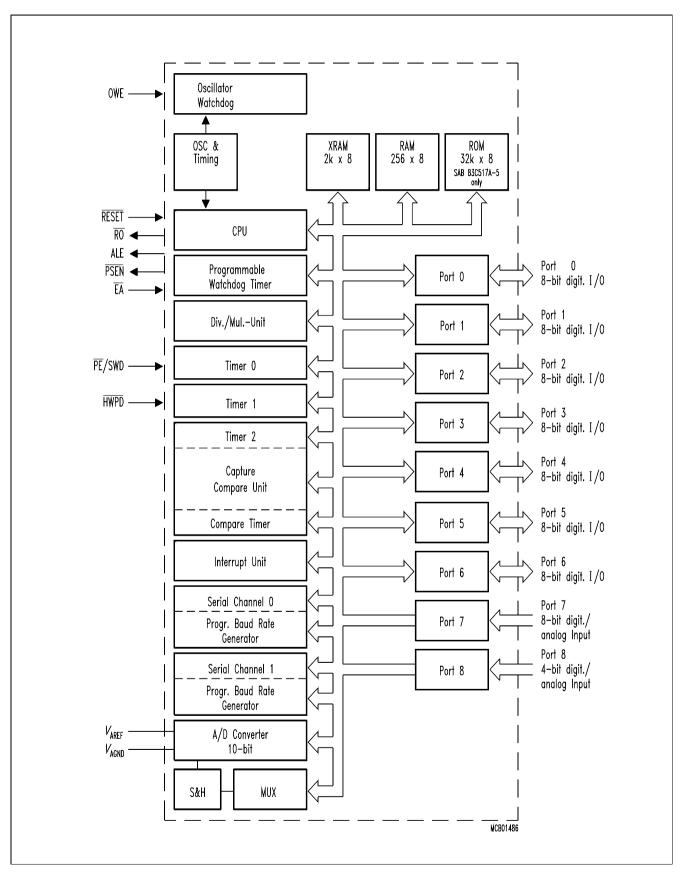

Figure 2-1 shows a block diagram of the SAB 80C517A

Figure 2-1, Block Diagram of the SAB 80C517A

# 3 Memory Organization

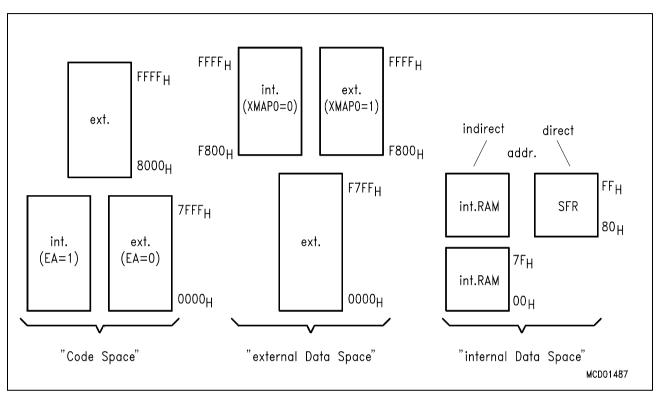

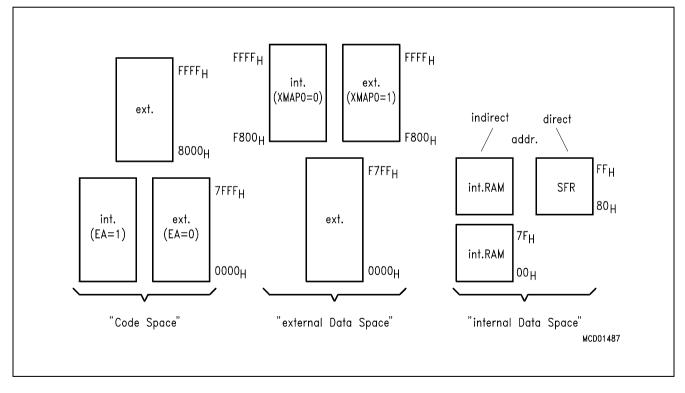

According to the SAB 8051 architecture, the SAB 80C517A has separate address spaces for program and data memory. **Figure 3-1** illustrates the mapping of address spaces.

Figure 3-1 Memory Map

#### 3.1 Program Memory, ROM Protection

The SAB 83C517A-5 has 32 Kbyte of on-chip ROM, while the SAB 80C517A has no internal ROM. The program memory can externally be expanded up to 64 Kbyte. Pin  $\overline{EA}$  controls whether program fetches below address 8000H are done from internal or external memory.

As a new feature the SAB 83C517A-5 offers the possibility of protecting the internal ROM against unauthorized access. This protection is implemented in the ROM-Mask. Therefore, the decision ROM-Protection 'yes' or 'no' has to be made when delivering the ROM-Code. Once enabled, there is no way of disabling the ROM-Protection.

Effect : The access to internal ROM done by an externally fetched MOVC instruction is disabled. Nevertheless, an access from internal ROM to external ROM is possible.

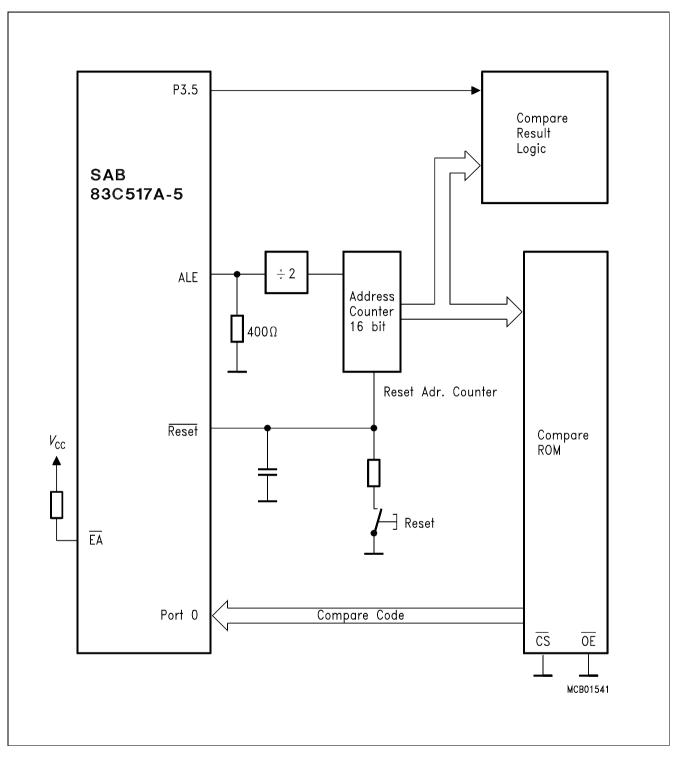

To verify the read protected ROM-Code a special ROM-Verify-Mode is implemented. This mode also can be used to verify unprotected internal ROM.

| <b>ROM-Protection</b> | ROM-Verification Mode<br>(see 'AC Characteristics')                                     | Restrictions                                                                                                                                       |

|-----------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| no                    | ROM-Verification Mode 1<br>(standard 8051 Verification Mode)<br>ROM-Verification Mode 2 | _                                                                                                                                                  |

| yes                   | ROM-Verification Mode 2                                                                 | <ul> <li>standard 8051 Verification<br/>Mode is disabled</li> <li>externally applied MOVC<br/>accessing to internal ROM<br/>is disabled</li> </ul> |

# 3.2 Data Memory

The data memory space consists of an internal and an external memory space. The SAB 80C517A contains another 2 kByte of On-Chip RAM above the 256 Bytes internal RAM of the base type SAB 80C517. This RAM is called XRAM in this document.

- External Data Memory

Up to 64 Kbyte external data memory can be addressed by instructions that use 8-bit or 16bit indirect addressing. For 8-bit addressing MOVX instructions in combination with registers R0 and R1 can be used. A 16-bit external memory addressing is supported by eight 16-bit datapointers. Registers XPAGE and SYSCON are controlling whether data fetches at addresses F800<sub>H</sub> to FFFF<sub>H</sub> are done from internal XRAM or from external data memory.

Internal Data Memory

The internal data memory is divided into four physically distinct blocks:

- the lower 128 bytes of RAM including four banks containing eight registers each

- the upper 128 byte of RAM

- the 128 byte special function register area

- a 2Kx8 area which is accessed like external RAM (MOVX-instructions), called XRAM implemented on chip at the address range fromF800<sub>H</sub> to FFFF<sub>H</sub>. Special Function Register SYSCON controls whether data is read or written (to) XRAM or external RAM

# 3.3 Special Function Registers

All registers, except the program counter and the four general purpose register banks, reside in the special function register area. The 81 special function registers include arithmetic registers, pointers, and registers that provide an interface between the CPU and the on-chip peripherals. There are also 128 directly addressable bits within the SFR area. All special function registers are listed in **table 3-1** and **table 3-2**.

In **table 3-1** they are organized in numeric order of their addresses. In **table 3-2** they are organized in groups which refer to the functional blocks of the SAB 80C517A.

| Address                                                                                                                                              | Register                                                                   | Contents<br>after Reset                                                                                                                  | Address                                                                                                                                                                 | Register                                                                         | Contents<br>after Reset                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 80 <sub>H</sub><br>81 <sub>H</sub><br>82 <sub>H</sub><br>83 <sub>H</sub><br>84 <sub>H</sub><br>85 <sub>H</sub><br>86 <sub>H</sub><br>87 <sub>H</sub> | P0 <sup>1)</sup><br>SP<br>DPL<br>DPH<br>(WDTL)<br>(WDTH)<br>WDTREL<br>PCON | FFH<br>07H<br>00H<br>00H<br>-<br>-<br>00H<br>00H                                                                                         | <b>A0</b> <sub>H</sub><br>A1 <sub>H</sub><br>A2 <sub>H</sub><br>A3 <sub>H</sub><br>A4 <sub>H</sub><br>A5 <sub>H</sub><br>A6 <sub>H</sub><br>A7 <sub>H</sub>             | P2 <sup>1)</sup><br>COMSETL<br>COMSETH<br>COMCLRL<br>COMCLRH<br>SETMSK<br>CJRMSK | FF <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>               |

| 88<br>89<br>80<br>80<br>80<br>80<br>80<br>80<br>80<br>80<br>80<br>80<br>80<br>80<br>80                                                               | <b>TCON</b> <sup>1)</sup><br>TMOD<br>TL0<br>TL1<br>TH0<br>TH1<br>-<br>-    | <b>00</b> H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>-<br>-                                                                          | A8 <sub>H</sub><br>A9 <sub>H</sub><br>AA <sub>H</sub><br>AB <sub>H</sub><br>AC <sub>H</sub><br>AC <sub>H</sub><br>AC <sub>H</sub><br>AE <sub>H</sub><br>AF <sub>H</sub> | IEN0 <sup>1)</sup><br>IP0<br>SORELL<br>-<br>-<br>-<br>-<br>-                     | <b>00H</b><br>00H<br>D9H<br>-<br>-<br>-<br>-                                                                                 |

| 90 <sub>H</sub><br>91 <sub>H</sub><br>92 <sub>H</sub><br>93 <sub>H</sub><br>94 <sub>H</sub><br>95 <sub>H</sub><br>96 <sub>H</sub><br>97 <sub>H</sub> | <b>P1</b> <sup>1)</sup><br>XPAGE<br>DPSEL<br>-<br>-<br>-<br>-              | FF <sub>H</sub><br>00 <sub>H</sub><br>XXXXX000 <sub>B</sub><br>-<br>-<br>-<br>-<br>-                                                     | <b>B0<sub>H</sub></b><br>B1 <sub>H</sub><br>B2 <sub>H</sub><br>B3 <sub>H</sub><br>B4 <sub>H</sub><br>B5 <sub>H</sub><br>B6 <sub>H</sub><br>B7 <sub>H</sub>              | <b>P3</b> <sup>1)</sup><br>SYSCON<br>-<br>-<br>-<br>-<br>-<br>-                  | FF <sub>H</sub><br>XXXX XX01 <sub>B</sub><br>-<br>-<br>-<br>-<br>-<br>-<br>-                                                 |

| 98 <sub>H</sub><br>99 <sub>H</sub><br>9A <sub>H</sub><br>9B <sub>H</sub><br>9C <sub>H</sub><br>9D <sub>H</sub><br>9E <sub>H</sub><br>9F <sub>H</sub> | SOCON <sup>1)</sup><br>SOBUF<br>IEN2<br>S1CON<br>S1BUF<br>S1RELL<br>-<br>- | <b>00</b> <sub>H</sub><br>XX <sub>H</sub><br>XX00 00X0 <sub>B</sub><br>0X00 0000 <sub>B</sub><br>XX <sub>H</sub><br>00 <sub>H</sub><br>- | B8H<br>B9H<br>BAH<br>BBH<br>BCH<br>BDH<br>BEH<br>BFH                                                                                                                    | IEN1 <sup>1)</sup><br>IP1<br>SORELH<br>S1RELH<br>-<br>-<br>-<br>-                | <b>00<sub>H</sub></b><br>XX00 0000 <sub>B</sub><br>XXXX XX11 <sub>B</sub><br>XXXX XX11 <sub>B</sub><br>-<br>-<br>-<br>-<br>- |

Table 3-1, Special Function Register

1) : Bit-addressable Special Function Register

| Address         | Register                   | Contents<br>after Reset | Address         | Register                | Contents<br>after Reset |

|-----------------|----------------------------|-------------------------|-----------------|-------------------------|-------------------------|

| C0 <sub>H</sub> | IRCON0 <sup>1)</sup>       | 00 <sub>H</sub>         | E0 <sub>H</sub> | ACC <sup>1)</sup>       | 00 <sub>H</sub>         |

| C1 <sub>H</sub> | CCEN                       | 00 <sub>H</sub>         | E1 <sub>H</sub> | CTCON                   | 0X00 0000B              |

| C2 <sub>H</sub> | CCL1                       | 00 <sub>H</sub>         | E2 <sub>H</sub> | CML3                    | 00 <sub>H</sub>         |

| C3 <sub>H</sub> | CCH1                       | 00 <sub>H</sub>         | E3 <sub>H</sub> | CMH3                    | 00 <sub>H</sub>         |

| C4 <sub>H</sub> | CCL2                       | 00 <sub>H</sub>         | E4 <sub>H</sub> | CML4                    | 00 <sub>H</sub>         |

| C5 <sub>H</sub> | CCH2                       | 00 <sub>H</sub>         | E5 <sub>H</sub> | CMH4                    | 00 <sub>H</sub>         |

| C6 <sub>H</sub> | CCL3                       | 00 <sub>H</sub>         | E6 <sub>H</sub> | CML5                    | 00 <sub>H</sub>         |

| C7 <sub>H</sub> | CCH3                       | 00 <sub>H</sub>         | E7 <sub>H</sub> | CMH5                    | 00 <sub>H</sub>         |

| C8 <sub>H</sub> | <b>T2CON</b> <sup>1)</sup> | 00 <sub>H</sub>         | E8 <sub>H</sub> | <b>P4</b> <sup>1)</sup> | FFH                     |

| C9 <sub>H</sub> | CC4EN                      | 00 <sub>H</sub>         | E9 <sub>H</sub> | MD0                     | XXH                     |

| CAH             | CRCL                       | 00 <sub>H</sub>         | EAH             | MD1                     | XXH                     |

| CBH             | CRCH                       | 00 <sub>H</sub>         | EBH             | MD2                     | XXH                     |

| CCH             | TL2                        | 00 <sub>H</sub>         | ECH             | MD3                     | XXH                     |

| CDH             | TH2                        | 00 <sub>H</sub>         | EDH             | MD4                     | XXH                     |

| CEH             | CCL4                       | 00 <sub>H</sub>         | EEH             | MD5                     | ХХ <sub>Н</sub>         |

| CF <sub>H</sub> | CCH4                       | 00 <sub>H</sub>         | EFH             | ARCON                   | 0XXX XXXX <sub>B</sub>  |

| D0 <sub>H</sub> | <b>PSW</b> <sup>1)</sup>   | 00 <sub>H</sub>         | F0              | B <sup>1)</sup>         | 00 <sub>H</sub>         |

| D1 <sub>H</sub> | IRCON1                     | 00 <sub>H</sub>         | F1 <sub>H</sub> | _                       | -                       |

| D2 <sub>H</sub> | CML0                       | 00 <sub>H</sub>         | F2 <sub>H</sub> | CML6                    | 00 <sub>H</sub>         |

| D3 <sub>H</sub> | CMH0                       | 00 <sub>H</sub>         | F3 <sub>H</sub> | CMH6                    | 00 <sub>H</sub>         |

| D4 <sub>H</sub> | CML1                       | 00 <sub>H</sub>         | F4 <sub>H</sub> | CML7                    | 00 <sub>H</sub>         |

| D5 <sub>H</sub> | CMH1                       | 00H                     | F5 <sub>H</sub> | CMH7                    | 00 <sub>H</sub>         |

| D6 <sub>H</sub> | CML2                       | 00 <sub>H</sub>         | F6 <sub>H</sub> | CMEN                    | 00 <sub>H</sub>         |

| D7 <sub>H</sub> | CMH2                       | 00 <sub>H</sub>         | F7 <sub>H</sub> | CMSEL                   | 00 <sub>H</sub>         |

| D8 <sub>H</sub> | ADCON0 <sup>1)</sup>       | 00 <sub>H</sub>         | F8 <sub>H</sub> | P5 <sup>1)</sup>        | FFH                     |

| D9 <sub>H</sub> | ADDATH                     | 00H                     | F9 <sub>H</sub> | _                       | -                       |

| DAH             | ADDATL                     | 00 <sub>H</sub>         | FAH             | P6                      | FFH                     |

| DBH             | P7                         | XX <sub>H</sub>         | FBH             | _                       | -                       |

| DCH             | ADCON1                     | XXXX 0000B              | FCH             | _                       | -                       |

| DDH             | P8                         | XX <sub>H</sub>         | FDH             | _                       | -                       |

| DEH             | CTRELL                     | 00 <sub>H</sub>         | FEH             | -                       | -                       |

| DF <sub>H</sub> | CTRELH                     | 00 <sub>H</sub>         | FFH             | -                       | -                       |

# Table 3-1, Special Function Register (cont'd)

1) : Bit-addressable Special Function Register

| Block                                            | Symbol                                                                                                                     | Name                                                                                                                                                                                                                                                                                                                         | Address                                                                                                                                                                                                                                                           | Contents after<br>Reset                                                                                                                                                                                                                     |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XRAM                                             | XPAGE                                                                                                                      | Page Address. Reg. for extended onchip RAM                                                                                                                                                                                                                                                                                   | 91 <sub>H</sub>                                                                                                                                                                                                                                                   | 00 <sub>H</sub>                                                                                                                                                                                                                             |

|                                                  | SYSCON                                                                                                                     | XRAM Control Reg.                                                                                                                                                                                                                                                                                                            | B1 <sub>H</sub>                                                                                                                                                                                                                                                   | XXXX XX01B <sup>3)</sup>                                                                                                                                                                                                                    |

| CPU                                              | ACC<br>B<br>DPH<br>DPL<br>DPSEL<br>PSW<br>SP                                                                               | Accumulator<br>B-Register<br>Data Pointer, High Byte<br>Data Pointer, Low Byte<br>Data Pointer Select Register<br>Program Status Word Register<br>Stack Pointer                                                                                                                                                              | <b>E0</b> <sub>H</sub> <sup>1)</sup><br><b>F0</b> <sub>H</sub> <sup>1)</sup><br>83 <sub>H</sub><br>82 <sub>H</sub><br>92 <sub>H</sub><br><b>D0</b> <sub>H</sub> <sup>1)</sup><br>81 <sub>H</sub>                                                                  | 00H<br>00H<br>00H<br>00H<br>XXXXX000B <sup>3)</sup><br>00H<br>07H                                                                                                                                                                           |

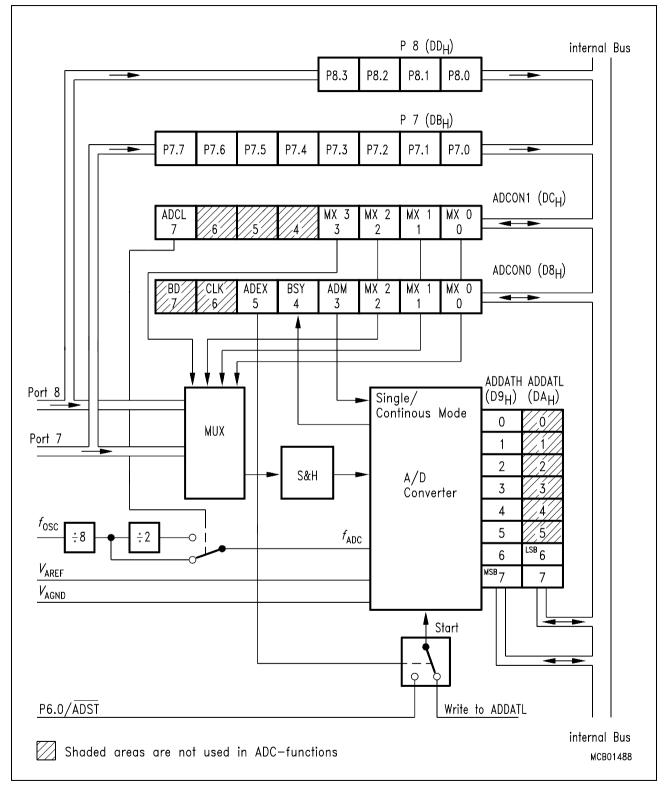

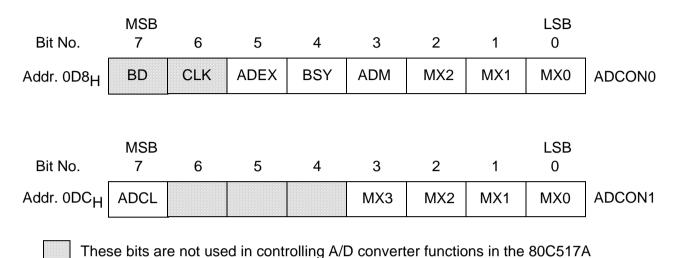

| A/D-<br>Converter                                | ADCON0<br>ADCON1<br>ADDATH<br>ADDATL                                                                                       | A/D Converter Control Register 0<br>A/D Converter Control Register 1<br>A/D Converter Data Register High Byte<br>A/D Converter Data Register Low Byte                                                                                                                                                                        | <b>D8<sub>H</sub></b> <sup>1)</sup><br>D <sub>H</sub><br>D9 <sub>H</sub><br>DA <sub>H</sub>                                                                                                                                                                       | <sup>00</sup> н<br>00 <sub>Н</sub><br>00 <sub>Н</sub><br>00 <sub>Н</sub>                                                                                                                                                                    |

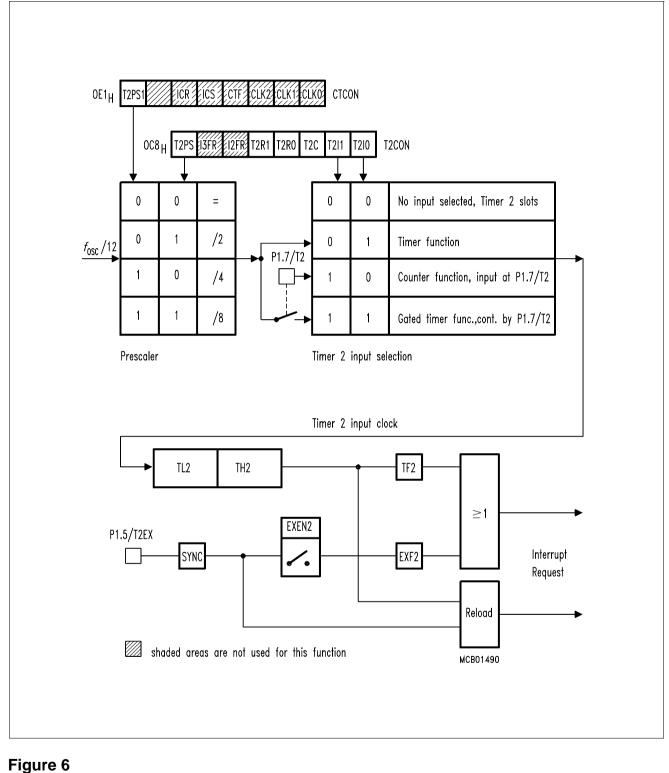

| Interrupt<br>System                              | IEN0<br>CTCON <sup>2)</sup><br>IEN1<br>IEN2<br>IP0<br>IP1<br>IRCON0<br>IRCON1<br>TCON <sup>2)</sup><br>T2CON <sup>2)</sup> | Interrupt Enable Register 0<br>Com. Timer Control Register<br>Interrupt Enable Register 1<br>Interrupt Enable Register 2<br>Interrupt Priority Register 0<br>Interrupt Priority Register 1<br>Interrupt Request Control Register<br>Interrupt Request Control Register<br>Timer Control Register<br>Timer 2 Control Register | A8 <sub>H</sub> <sup>1)</sup><br>E1 <sub>H</sub><br>B8 <sub>H</sub> <sup>1)</sup><br>9A <sub>H</sub><br>A <sub>9H</sub><br>B9 <sub>H</sub><br>C0 <sub>H</sub> <sup>1)</sup><br>D1 <sub>H</sub><br>88 <sub>H</sub> <sup>1)</sup><br>0C8 <sub>H</sub> <sup>1)</sup> | 00 <sub>H</sub><br>0X00 0000 <sub>B</sub> <sup>3)</sup><br>00 <sub>H</sub><br>XX00 00X0 <sub>B</sub> <sup>3)</sup><br>00 <sub>H</sub><br>XX00 0000 <sub>B</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub> |

| MUL/DIV<br>Unit                                  | ARCON<br>MD0<br>MD1<br>MD2<br>MD3<br>MD4<br>MD5                                                                            | Arithmetic Control Register<br>Multiplication/Division Register 0<br>Multiplication/Division Register 1<br>Multiplication/Division Register 2<br>Multiplication/Division Register 3<br>Multiplication/Division Register 4<br>Multiplication/Division Register 5                                                              | EF <sub>H</sub><br>E9 <sub>H</sub><br>EAH<br>EBH<br>ECH<br>EDH<br>EEH                                                                                                                                                                                             | 0XXX XXXXB<br>XXH<br>XXH<br>XXH<br>XXH<br>XXH<br>XXH<br>XXH                                                                                                                                                                                 |

| Compare/<br>Capture-<br>Unit<br>(CCU),<br>Timer2 | CCEN<br>CC4EN<br>CCH1<br>CCH2<br>CCH3<br>CCH4<br>CCL1                                                                      | Comp./Capture Enable Reg.<br>Comp./Capture 4 Enable Reg.<br>Comp./Capture Reg. 1, High Byte<br>Comp./Capture Reg. 2, High Byte<br>Comp./Capture Reg. 3, High Byte<br>Comp./Capture Reg. 4, High Byte<br>Comp./Capture Reg. 1, Low Byte                                                                                       | C1 <sub>H</sub><br>C9 <sub>H</sub><br>C3 <sub>H</sub><br>C5 <sub>H</sub><br>C7 <sub>H</sub><br>CF <sub>H</sub><br>C2 <sub>H</sub>                                                                                                                                 | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H                                                                                                                                                                                               |

# Table 3-1, Special Function Register (cont'd)

1) Bit-addressable special function registers

2) This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

3) X means that the value is indeterminate

| Table 3-1, Special | Function Register |

|--------------------|-------------------|

|--------------------|-------------------|

| Block      | Symbol  | Name                             | Address                       | Contents after<br>Reset              |

|------------|---------|----------------------------------|-------------------------------|--------------------------------------|

| Compare/   | CCL2    | Comp./Capture Reg. 2, Low Byte   | C4 <sub>H</sub>               | 00 <sub>H</sub>                      |

| Capture-   | CCL3    | Comp./Capture Reg. 3, Low Byte   | C6 <sub>H</sub>               | 00 <sub>H</sub>                      |

| Unit (CCU) | CCL4    | Comp./Capture Reg. 4, Low Byte   | CEH                           | 00 <sub>H</sub>                      |

| (cont´d)   | CMEM    | Compare Enable Register          | F6 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CMH0    | Compare Reg. 0, High Byte        | D3 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CMH1    | Compare Reg. 1, High Byte        | D5 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CMH2    | Compare Reg. 2, High Byte        | D7 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CMH3    | Compare Reg. 3, High Byte        | E3 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CMH4    | Compare Reg. 4, High Byte        | E5 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CMH5    | Compare Reg. 5, High Byte        | E7H                           | 00 <sub>H</sub>                      |

|            | CMH6    | Compare Reg. 6, High Byte        | F3 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CMH7    | Compare Reg. 7, High Byte        | F5H                           | 00 <sub>H</sub>                      |

|            | CML0    | Compare Register 0, Low Byte     | D2 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CML1    | Compare Register 1, Low Byte     | D4 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CML2    | Compare Register 2, Low Byte     | D6 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CML3    | Compare Register 3, Low Byte     | E2 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CML4    | Compare Register 4, Low Byte     | E4 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CML5    | Compare Register 5, Low Byte     | E6 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CML6    | Compare Register 6, Low Byte     | F2 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CML7    | Compare Register 7, Low Byte     | F4 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CMSEL   | Compare Input Select             | F7H                           | 00 <sub>H</sub>                      |

|            | CRCH    | Com./Rel./Capt. Reg. High Byte   | CBH                           | 00 <sub>H</sub>                      |

|            | CRCL    | Com./Rel./Capt. Reg. Low Byte    | CAH                           | 00 <sub>H</sub>                      |

|            | COMSETL | Compare register, Low Byte       | A1 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | COMSETH | Compare register, High Byte      | A2 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | COMCLRL | Compare register, Low Byte       | A3 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | COMCLRH | Compare register, High Byte      | A4 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | SETMSK  | mask register, concerning COMSET | A5 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CLRMSK  | mask register, concerning COMCLR | A6 <sub>H</sub>               | 00 <sub>H</sub>                      |

|            | CTCON   | Com. Timer Control Reg.          | E1 <sub>H</sub>               | 0X00 0000 <sub>B</sub> <sup>3)</sup> |

|            | CTRELH  | Com. Timer Rel. Reg., High Byte  | DFH                           | 00 <sub>H</sub>                      |

|            | CTRELL  | Com. Timer Rel. Reg., Low Byte   | DEH                           | 00 <sub>H</sub>                      |

|            | TH2     | Timer 2, High Byte               | CDH                           | 00 <sub>H</sub>                      |

|            | TL2     | Timer 2, Low Byte                | CCH                           | 00 <sub>H</sub>                      |

|            | T2CON   | Timer 2 Control Register         | C8 <sub>H</sub> <sup>1)</sup> | 00 <sub>H</sub>                      |

1) Bit-addressable special function registers

2) This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

3) X means that the value is indeterminate

| Block               | Symbol                                                                                                                 | Name                                                                                                                                                                                                                                                                                                                                                             | Address                                                                                                                                                                                                                                                            | Contents after<br>Reset                                                                                                                                                                                                                                                 |

|---------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ports<br>Pow. Save  | P0<br>P1<br>P2<br>P3<br>P4<br>P5<br>P6<br>P7<br>P8<br>PCON                                                             | Port 0<br>Port 1<br>Port 2<br>Port 3<br>Port 4<br>Port 5<br>Port 6<br>Port 7, Analog/Digital Input<br>Port 8, Analog/Digital Input, 4-bit<br>Power Control Register                                                                                                                                                                                              | 80 <sub>H</sub> <sup>1)</sup><br>90 <sub>H</sub> <sup>1)</sup><br>A0 <sub>H</sub> <sup>1)</sup><br>B0 <sub>H</sub> <sup>1)</sup><br>E8 <sub>H</sub> <sup>1)</sup><br>F8 <sub>H</sub> <sup>1)</sup><br>FA <sub>H</sub><br>DB <sub>H</sub><br>DD <sub>H</sub><br>87H | FF <sub>H</sub><br>FF <sub>H</sub><br>FF <sub>H</sub><br>FF <sub>H</sub><br>FF <sub>H</sub><br>FF <sub>H</sub><br>-<br>-                                                                                                                                                |

| Modes               |                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                    | <sup>oo</sup> H                                                                                                                                                                                                                                                         |

| Serial<br>Channels  | ADCON0 <sup>2)</sup><br>PCON <sup>2)</sup><br>S0BUF<br>S0CON<br>S0RELL<br>S0RELH<br>S1BUF<br>S1CON<br>S1RELL<br>S1RELH | A/D Converter Control Reg.<br>Power Control Register<br>Serial Channel 0 Buffer Reg.<br>Serial Channel 0 Control Reg.<br>Serial Channel 0 Reload Reg., low byte<br>Serial Channel 0 Reload Reg., high byte<br>Serial Channel 1 Buffer Reg.<br>Serial Channel 1 Control Reg.<br>Serial Channel 1 Reload Reg., low byte<br>Serial Channel 1 Reload Reg., high byte | <b>D8<sub>H</sub></b> <sup>1)</sup><br>87 <sub>H</sub><br>99 <sub>H</sub><br><b>98<sub>H</sub></b> <sup>1)</sup><br>0AA <sub>H</sub><br>BA <sub>H</sub><br>9C <sub>H</sub><br>9B <sub>H</sub><br>9D <sub>H</sub><br>BB <sub>H</sub>                                | 00 <sub>H</sub><br>00 <sub>H</sub><br>XX <sub>H</sub><br>00 <sub>H</sub><br>D9 <sub>H</sub><br>XXXX XX11 <sub>B</sub> <sup>3)</sup><br>XX <sub>H</sub> <sup>3)</sup><br>0X00 0000 <sub>B</sub> <sup>3)</sup><br>00 <sub>H</sub><br>XXXX XX11 <sub>B</sub> <sup>3)</sup> |

| Timer 0/<br>Timer 1 | TCON<br>TH0<br>TH1<br>TL0<br>TL1<br>TMOD                                                                               | Timer Control Register<br>Timer 0, High Byte<br>Timer 1, High Byte<br>Timer 0, Low Byte<br>Timer 1, Low Byte<br>Timer Mode Register                                                                                                                                                                                                                              | 88 <sub>H</sub> <sup>1)</sup><br>8C <sub>H</sub><br>8D <sub>H</sub><br>8A <sub>H</sub><br>8B <sub>H</sub><br>89 <sub>H</sub>                                                                                                                                       | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                                                                                                                                                                             |

| Watchdog            | IEN0 <sup>2)</sup><br>IEN1 <sup>2)</sup><br>IP0 <sup>2)</sup><br>IP1 <sup>2)</sup><br>WDTREL                           | Interrupt Enable Register 0<br>Interrupt Enable Register 1<br>Interrupt Priority Register 0<br>Interrupt Priority Register 1<br>Watchdog Timer Reload Reg.                                                                                                                                                                                                       | <b>A8<sub>H</sub></b> <sup>1)</sup><br><b>B8<sub>H</sub></b> <sup>1)</sup><br>A9 <sub>H</sub><br>B9 <sub>H</sub><br>86 <sub>H</sub>                                                                                                                                | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>XX00 0000 <sub>B</sub> <sup>3)</sup><br>00 <sub>H</sub>                                                                                                                                                        |

# Table 3-1, Special Function Register

1) Bit-addressable special function registers

2) This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

3) X means that the value is indeterminate

#### 3.4 Architecture for the XRAM

The contents of the XRAM is not affected by a reset or HW Power Down. After power-up the contents is undefined, while it remains unchanged during and after a reset or HW Power Down if the power supply is not turned off.

The additional On-Chip RAM is logically located in the "external data memory" range at the upper end of the 64 KByte address range ( $F800_H$ -FFFF<sub>H</sub>). It is possible to enable and disable (only by reset) the XRAM. If it is disabled the device shows the same behaviour as the parts without XRAM, i.e. all MOVX accesses use the external bus to physically external data memory.

#### 3.4.1 Accesses to XRAM

Because the XRAM is used in the same way as external data memory the same instruction types must be used for accessing the XRAM.

#### Note:

If a reset occurs during a write operation to XRAM, the effect on XRAM depends on the cycle which the reset is detected at (MOVX is a 2-cycle instruction):

Reset detection at cycle 1: The new value will not be written to XRAM. The old value is not affected.

Reset detection at cycle 2: The old value in XRAM is overwritten by the new value.

#### Accesses to XRAM using the DPTR

There are a Read and a Write instruction from and to XRAM which use one of the 16-bit DPTR for indirect addressing. The instructions are:

| MOVX | A, @DPTR | (Read)  |

|------|----------|---------|

| MOVX | @DPTR, A | (Write) |

Normally the use of these instructions would use a physically external memory. However, in the SAB 80C517A the XRAM is accessed if it is enabled and if the DPTR points to the XRAM address space (DPTR  $\geq$  F800<sub>H</sub>).

#### Accesses to XRAM using the Registers R0/R1

The 8051 architecture provides also instructions for access to external data memory range which use only an 8-bit address (indirect addressing with registers R0 or R1). The instructions are:

| MOVX | A, @ Ri | (Read)  |

|------|---------|---------|

| MOVX | @Ri, A  | (Write) |

In application systems, either a real 8-bit bus (with 8-bit address) is used or Port 2 serves as page register which selects pages of 256-Byte. However, the distinction, whether Port 2 is used as general purpose I/0 or as "page address" is made by the external system design. From the device's point of view it cannot be decided whether the Port 2 data is used externally as address or as I/0 data!

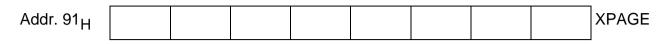

Hence, a special page register is implemented into the SAB 80C517A to provide the possibility of accessing the XRAM also with the MOVX @Ri instructions, i.e. XPAGE serves the same function for the XRAM as Port 2 for external data memory.

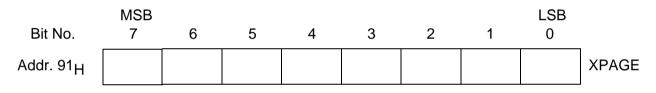

#### **Special Function Register XPAGE**

The reset value of XPAGE is 00<sub>H</sub>.

XPAGE can be set and read by software.

**Figures 3-2** to **3-4** show the dependencies of XPAGE- and Port 2 - addressing in order to explain the differencies in accessing XRAM, ext. RAM or what is to do when Port 2 is used as an I/O-port.

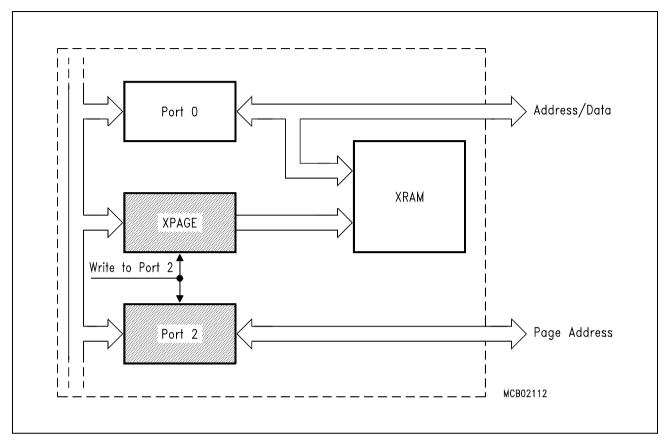

#### Figure 3-2 Write Page Address to Port 2

MOV P2, pageaddress will write the page address to Port 2 and XPAGE-Register.

When external RAM is to be accessed in the XRAM address range (F800<sub>H</sub> - FFF<sub>H</sub>) XRAM has to be disabled. When additional external RAM is to be addressed in an address range  $\leq$  XRAM (F800<sub>H</sub>) XRAM may remain being enabled and there is no need to overwrite XPAGE by a second move.

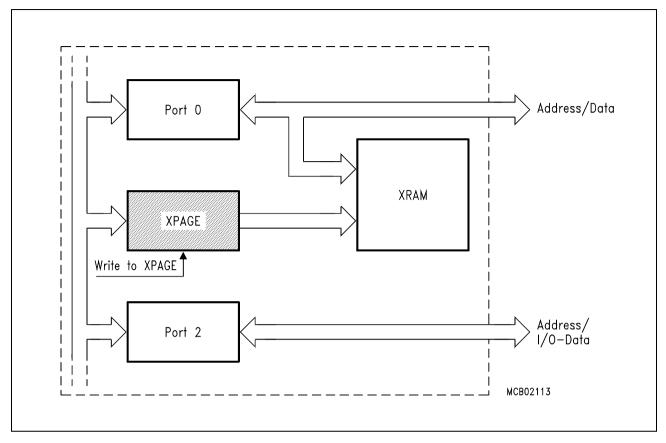

#### Figure 3-3 Write Page Address to XPAGE

The page address is only written to XPAGE-register. Port 2 is available for addresses or I/O-Data. See **figure 3-4** to see what happens when Port 2 is used as I/O-Port.

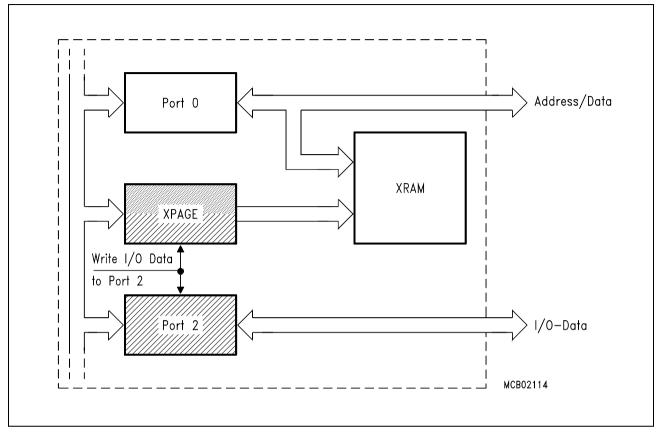

#### Figure 3-4 Use of Port 2 as I/O-Port

At a write to Port 2, XRAM address in XPAGE-register will be overwritten because of the concurrent write to Port 2 and XPAGE-register. So whenever XRAM is used and the XRAM address differs from the byte written to Port 2 latch it is absolutely nessesary to rewrite XPAGE with page address.

# Example:

I/O-Data at Port 2 shall be 0AAH. A Byte shall be fetched from XRAM at address 0F830H

MOV R0, #30HMOV P2, #0AAH; P2 shows 0AA<sub>H</sub>MOV XPAGE, #0F8H; P2 still shows 0AA<sub>H</sub> but XRAM is addressedMOVX A, @R0; the contents of XRAM at 0F830<sub>H</sub> is moved to accu

The register XPAGE provides the upper address byte for accesses to XRAM with MOVX @Ri instructions. If the address formed from XPAGE and Ri is less than the XRAM address range, then an external access is performed. For the SAB 80C517A the contents of XPAGE must be greater or equal than F8<sub>H</sub> in order to use the XRAM. Of course, the XRAM must be enabled if it shall be used with MOVX @Ri instructions.

Thus, the register XPAGE is used for addressing of the XRAM; additionally its contents are used for generating the internal XRAM select. If the contents of XPAGE is less than the XRAM address range then an external bus access is performed where the upper address byte is provided by P2 and not by XPAGE!

Therefore, the software has to distinguish two cases, if the MOVX @Ri instructions with paging shall be used:

| a) Access to XRAM:                              | The upper address byte must be written to XPAGE or P2;    |

|-------------------------------------------------|-----------------------------------------------------------|

|                                                 | both writes selects the XRAM address range.               |

| <ul><li>b) Access to external memory:</li></ul> | The upper address byte must be written to P2; XPAGE       |

|                                                 | will be loaded with the same address in order to deselect |

|                                                 | the XRAM.                                                 |

The behaviour of Port0, Port2 and the RD/WR signals depends on the state of pin EA and on the control bits XMAP0 and XMAP1 in register SYSCON.

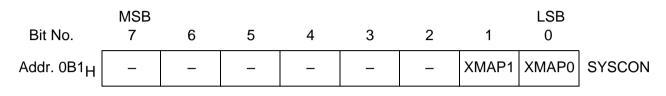

# 3.4.2 Control of XRAM in the SAB 80C517A

There are two control bits in register SYSCON which control the use and the bus operation during accesses to the additional On-Chip RAM in XDATA range ( $\triangle$  XRAM).

#### **Special Function Register SYSCON**

| Bit   | Function                                                                                                                                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XMAP0 | Global enable/disable bit for XRAM memory.<br>XMAP0 = 0: The access to XRAM (= On-Chip XDATA memory) is enabled.<br>XMAP0 = 1: The access to XRAM is disabled. All MOVX accesses are performed by<br>the external bus.                                                                                                                                   |

| XMAP1 | Control bit for RD/WR signals during accesses to XRAM; this bit has no effect if<br>XRAM is disabled (XMAP0 = 1) or if addresses outside the XRAM address range are<br>used for MOVX accesses.<br>XMAP1 = 0: The signals RD and WR are not activated during accesses to XRAM.<br>XMAP1 = 1: The signals RD and WR are activated during accesses to XRAM. |

Reset value of SYSCON is XXXX XX01B.

The control bit XMAP0 is a global enable/disable bit for the additional On-Chip RAM (XRAM). If this bit is set, the XRAM is disabled, all MOVX accesses use external memory via the external bus. In this case the SAB80C517A can't use the additional On-Chip RAM and is compatible with the types without XRAM.

A hardware protection is done by an unsymetric latch at XMAP0-bit. A unintentional disabling of XRAM could be dangerous since indeterminate values could be read from external bus. To avoid this the XMAP-bit is forced to '1' only by reset. Additional during reset an internal capacitor is loaded. So the reset state is a disabled XRAM. Because of the load time of the capacitor XMAP0-bit once written to '0' (that is, discharging capacitor) cannot be set to '1' again by software. On the other hand any distortion (software hang up, noise,...) is not able to load this capacitor, too. That is, the stable status is XRAM enabled. The only way to disable XRAM after it was enabled is a reset.

The clear instruction for the XMAP0-bit should be integrated in the program initialization routine before XRAM is used. In extremely noisy systems the user may have redundant clear instructions.

The control bit XMAP1 is relevant only if the XRAM is accessed. In this case the external  $\overline{RD}$  and  $\overline{WR}$  signals at P3.6 and P3.7 are not activated during the access, if XMAP1 is cleared. For debug purposes it might be useful to have these signals available. This is performed if XMAP1 is set.

# 3.4.3 Behaviour of Port0 and Port2

The behaviour of Port 0 and P2 during a MOVX access depends on the control bits in register SYSCON and on the state of pin  $\overline{EA}$ . The **table 3-3** lists the various operating conditions. It shows the following characteristics:

- a) Use of P0 and P2 pins during the MOVX access.

- Bus: The pins work as external address/data bus. If (internal) XRAM is accessed, the data read from the XRAM can not be seen on the bus.

- I/0: The pins work as Input/Output lines under control of their latch.

- b) Activation of the  $\overline{RD}$  and  $\overline{WR}$  pin during the access.

- c) Use of internal or external XDATA memory.

The shaded areas describe the standard operation as each 80C51 device without on-chip XRAM behaves.

|           |           |                        | <u>EA</u> = 0          |                        |                        | <u>EA</u> = 1                 |                        |

|-----------|-----------|------------------------|------------------------|------------------------|------------------------|-------------------------------|------------------------|

|           |           |                        | XMAP1, XMAP0           |                        |                        | XMAP1, XMAP0                  |                        |

|           |           | 00                     | 10                     | X1                     | 00                     | 10                            | X1                     |

| MOVX<br>© | DPTR      | a)P0/P2→Bus            | a)P0/P2→Bus            | a)P0/P2→Bus            | a)P0/P2→Bus            | a)P0/P2→Bus                   | a)P0/P2→Bus            |

|           | <<br>XRAM | D)RU/WR active         | D)RU/WR active         | D)RD/WK aclive         | D)RU/WK aciive         | D)RU/WR active                | D)RD/WR active         |

|           | address   | is used                       | is used                |

|           | range     |                        |                        |                        |                        |                               |                        |

|           | DPTR      | a)P0/P2→Bus            | a)P0/P2—>Bus           | a)P0/P2→Bus            | a)P0/P2→I/O            | a)P0/P2→Bus                   | a)P0/P2→Bus            |

|           | ۸I        | (WR-Data only)         | (WR-Data only)         |                        |                        | ( <u>WR</u> -Data only)       |                        |

|           | XRAM      | b) <u>RD/WR</u>        | b) <u>RD/WR</u> active | b) <u>RD/WR</u> active | b) <u>RD/WR</u>        | b) <u>RD/WR</u> active        | b) <u>RD/WR</u> active |

|           | address   | inactive               | c)XRAM is used         | c) ext.memory          | inactive               | c)XRAM is used                | c) ext.memory          |

|           | range     | c)XRAM is used         |                        | is used                | c)XRAM is used         |                               | is used                |

| MOVX      | XPAGE     | a)P0→Bus               | a)P0—>Bus              | a)P0→Bus               | a)P0—>Bus              | a)P0—>Bus                     | a)P0→Bus               |

| @ Ri      | v         | P2→I/O                 | P2→J/O                 | P2→I/O                 | P2→I/O                 | P2→I/O                        | P2→I/O                 |

|           | XRAM      | b) <u>RD/WR</u> active        | b) <u>RD/WR</u> active |

|           | addr.page | c)ext.memory           | c)ext.memory           | c)ext.memory           | c)ext.memory           | c)ext.memory                  | c)ext.memory           |

|           | range     | is used                       | is used                |

|           | XPAGE     | a)P0→Bus               | a)P0—>Bus              | a)P0→Bus               | a)P0/P2→I/O            | a)P0→Bus                      | a)P0—>Bus              |

|           | ۸I        | a only)                | (WR-Data only)         | P2→I/O                 |                        | ( <u>WR</u> -Data only)       | P2→I/O                 |

|           | XRAM      |                        | P2→I/O                 |                        |                        | P2→I/O                        |                        |

|           | addr.page | b) <mark>RD/WR</mark>  | b) <u>RD/WR</u> active | b) <u>RD/WR</u> active | b) <u>RD/WR</u>        | b) <u>RD/WR</u> active        | b) <u>RD/WR</u> active |

|           | range     | inactive               |                        |                        | inactive               |                               |                        |

|           |           | c)XRAM is used         | c)XRAM is used         | c)ext.memory           | c)XRAM is used         | c)XRAM is used c)XRAM is used | c)ext.memory           |

|           |           |                        |                        | is used                |                        |                               | is used                |

|           |           |                        |                        |                        |                        |                               |                        |

modes compatible to 8051-family

Table 3-3: Behaviour of P0/P2 and RD/WR During MOVX Accesses

#### 4 System Reset

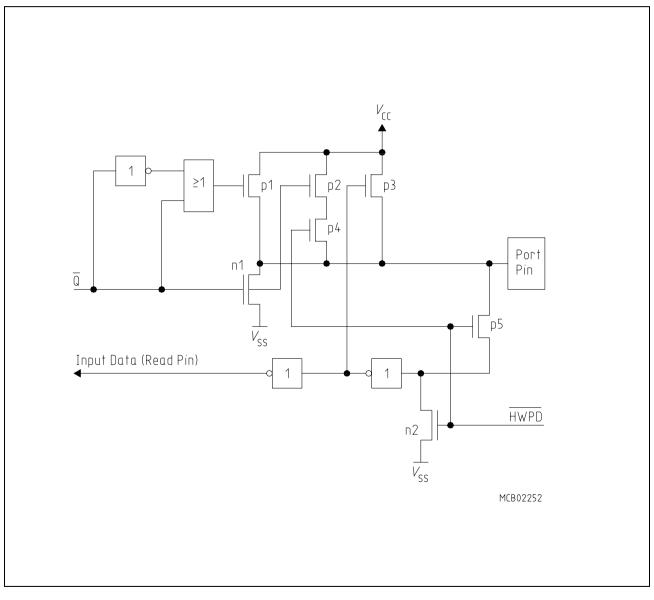

#### 4.1 Additional Hardware Power Down Mode in the SAB 80C517A

The SAB 80C517A has an additional Power Down Mode which can be initiated by an external signal at a dedicated pin. This pin is labeled HWPD and is a floating input line (active low). This pin substitutes one of the VSS pins of the base types SAB 80C517 (PLCC84: Pin60; P-MQFP-100-2: Pin36). Because this new power down mode is activated by an external hardware signal this mode is referred to as Hardware Power Down Mode in opposite to the program controlled Software Power Down Mode.

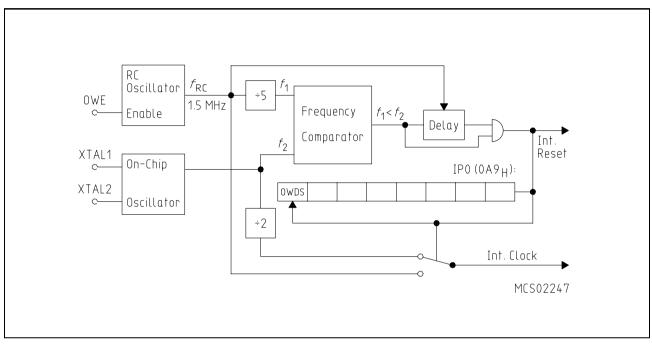

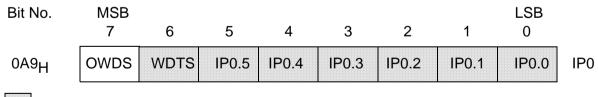

For a correct function of the Hardware Power Down Mode the oscillator watchdog unit including its internal RC oscillator is needed. Therefore this unit must be enabled by pin OWE (OWE = High), if the Hardware Power Down Mode shall be used. However, the control pin  $\overline{PE}$ /SWD has no control function for the Hardware Power Down Mode; it enables and disables only the use of all software controlled power saving modes (Slow Down Mode, Idle Mode, Software Power Down Mode).

The function of the new Hardware Power Down Mode is as follows:

The pin  $\overline{\text{HWPD}}$  controls this mode. If it is on logic high level (inactive) the part is running in the normal operating modes. If pin  $\overline{\text{HWPD}}$  gets active (low level) the part enters the Hardware Power Down Mode; as mentioned above this is independent of the state of pin  $\overline{\text{PE}}/\text{SWD}$ .

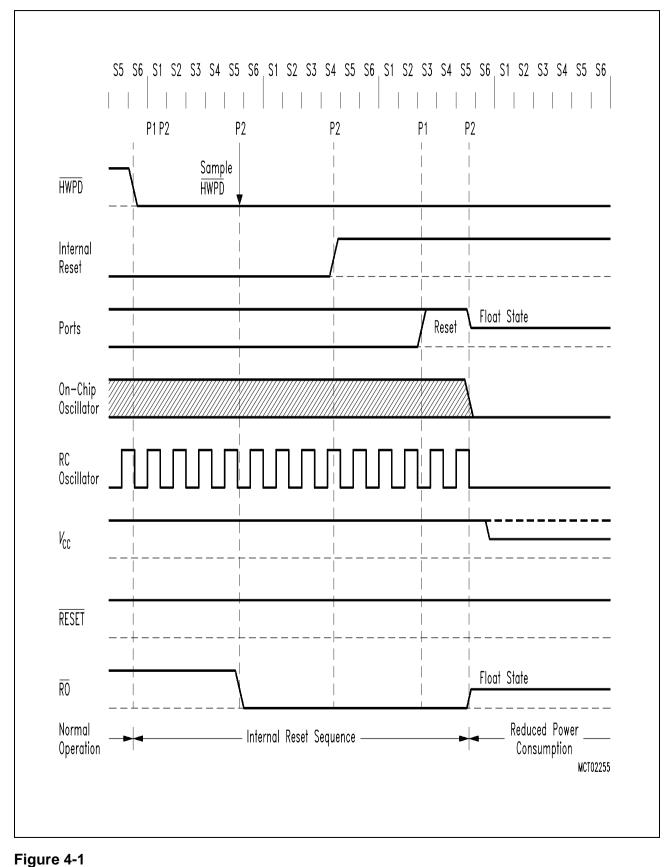

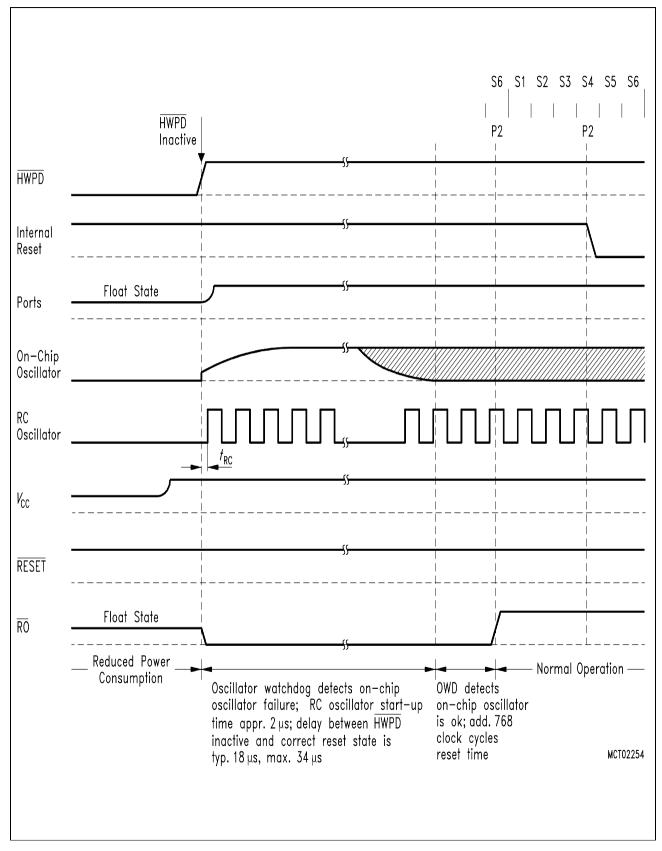

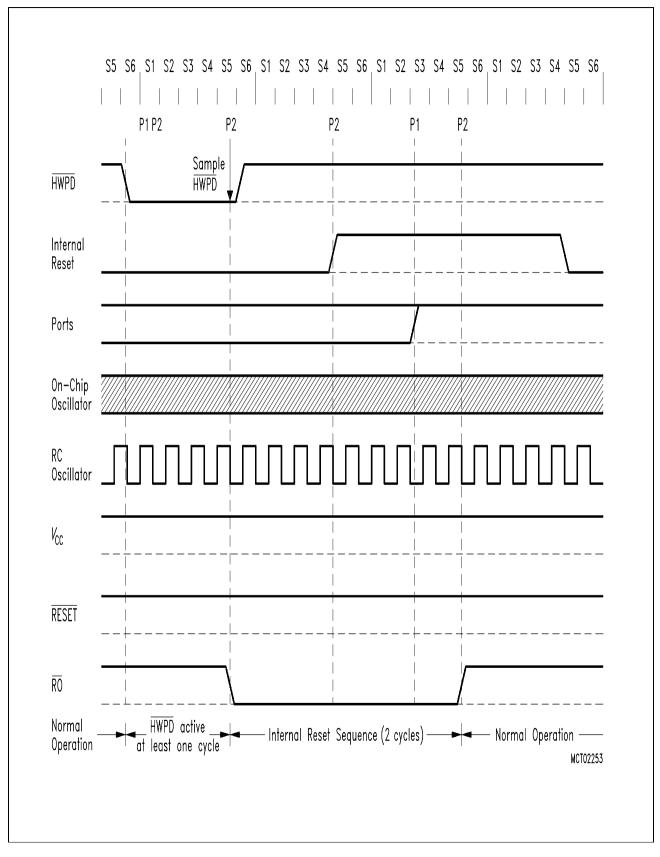

HWPD is sampled once per machine cycle. If it is found active, the device starts a complete internal reset sequence. This takes two machine cycles; all pins have their default reset states during this time. This reset has exactly the same effects as a hardware reset; i.e.especially the watchdog timer is stopped and its status flag WDTS is cleared. In this phase the power consumption is not yet reduced. After completion of the internal reset both oscillators of the chip are disabled, the on-chip oscillator as well as the oscillator watchdog's RC oscillator. At the same time the port pins and several control lines enter a floating state as shown in **table 4-1**. In this state the power consumption is reduced.

**Table 4-1** also lists the voltages which may be applied at the pins during Hardware Power DownMode without affecting the low power consumption.

| Pins                                  | Status                                                                                                             | Voltage Range at Pin During<br>HW-Power Down                   |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| P0, P1, P2, P3, P4,<br>P5, P6, P7, P8 | Floating outputs /<br>Disabled input function                                                                      | $V_{\rm SS} \leq V_{\rm IN} \leq V_{\rm CC}$                   |

| ĒĀ                                    | active input                                                                                                       | $V_{\rm IN}$ = $V_{\rm CC}$ or $V_{\rm IN}$ = $V_{\rm SS}$     |

| PE/SWD                                | active input, Pull-up resistor disabled during HW power down                                                       | $V_{\rm IN} = V_{\rm CC}$ or $V_{\rm IN} = V_{\rm SS}$         |

| XTAL1                                 | active output                                                                                                      | pin may not be driven                                          |

| XTAL2                                 | disabled input function                                                                                            | $V_{\rm SS} \leq V_{\rm IN} \leq V_{\rm CC}$                   |

| PSEN, ALE                             | Floating outputs /<br>Disabled input function<br>(for test modes only)                                             | $V_{\rm SS} \leq V_{\rm IN} \leq V_{\rm CC}$                   |

| VAREF, VAGND                          | active supply pins                                                                                                 | $V_{\rm AGnd} \leq V_{\rm IN} \leq V_{\rm CC}$                 |

| OWE                                   | active input; must be at high level for<br>start-up after HW PD; pull up resistor<br>disabled during HW-power down | $V_{\rm IN} = V_{\rm CC}$<br>or<br>$(V_{\rm IN} = V_{\rm SS})$ |

| Reset                                 | active input; must be on high level if<br>HW PD is used                                                            | $V_{\rm IN} = V_{\rm CC}$                                      |

| R0                                    | Floating output                                                                                                    | $V_{\rm SS} \le V_{\rm IN} \le V_{\rm CC}$                     |

# Table 4-1, Status of all Pins During Hardware Power Down Mode

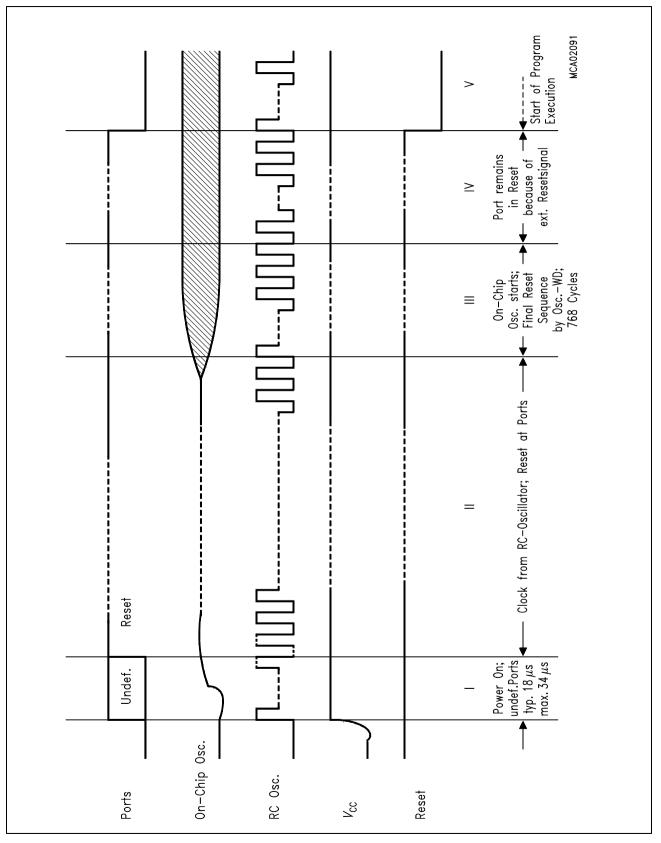

The power down state is maintained while pin HWPD is held active. If HWPD goes to high level (inactive state) an automatic start up procedure is performed:

- First the pins leave their floating condition and enter their default reset state as they had immediately before going to float state.

- Both oscillators are enabled (only if OWE = high). While the on-chip oscillator (with pins XTAL1 and XTAL2) usually needs a longer time for start-up, if not externally driven (with crystal approx. 1 ms), the oscillator watchdog's RC oscillator has a very short start-up time (typ. less than 2 microseconds).

- Because the oscillator watchdog is active it detects a failure condition if the on-chip oscillator hasn't yet started. Hence, the watchdog keeps the part in reset and supplies the internal clock from the RC oscillator.

- Finally, when the on-chip oscillator has started, the oscillator watchdog releases the

part from reset after it performed a final internal reset sequence and switches the clock supply

to the on-chip oscillator. This is exactly the same procedure as when the oscillator watchdog

detects first a failure and then a recovering of the oscillator during normal operation.

Therefore, also the oscillator watchdog status flag is set after restart from Hardware Power

Down Mode.

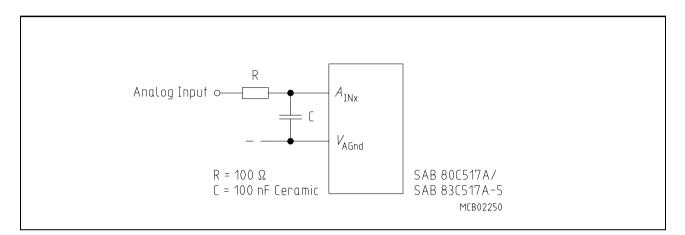

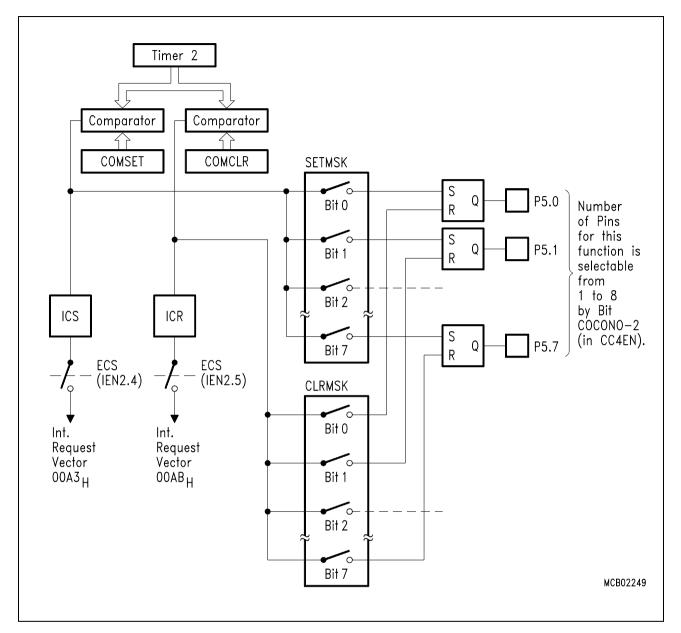

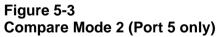

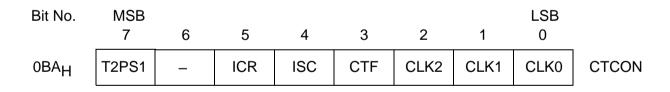

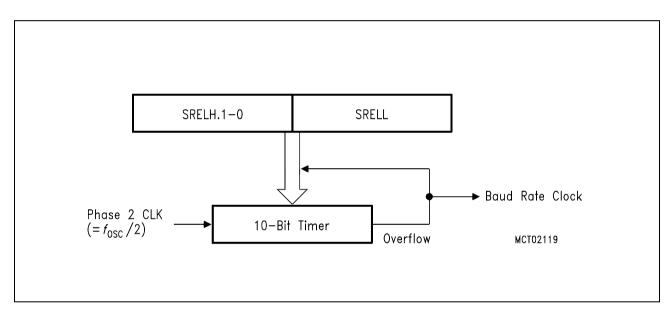

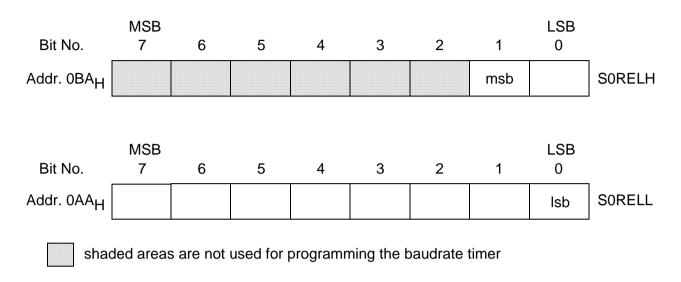

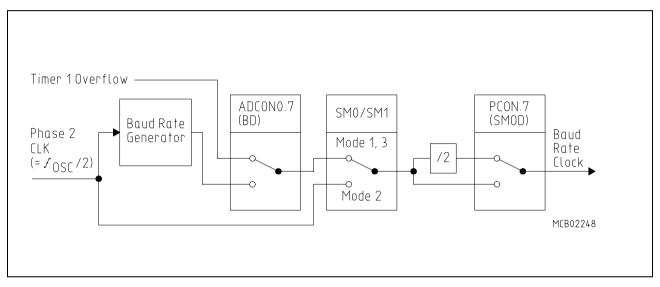

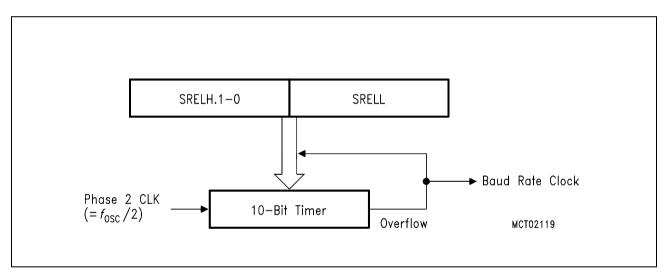

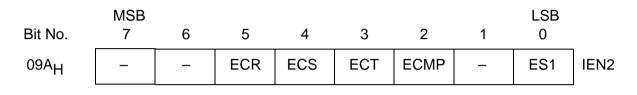

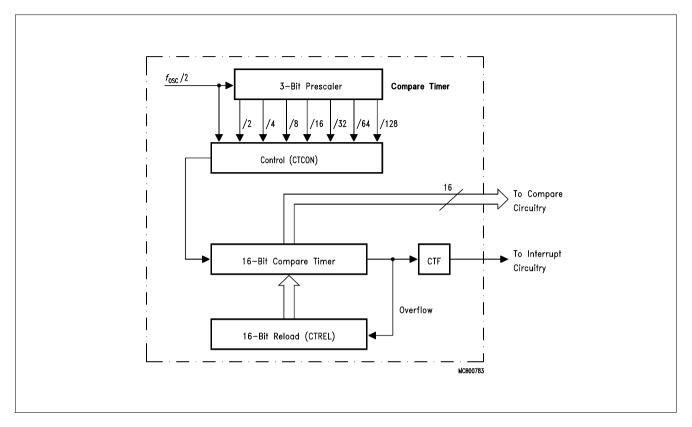

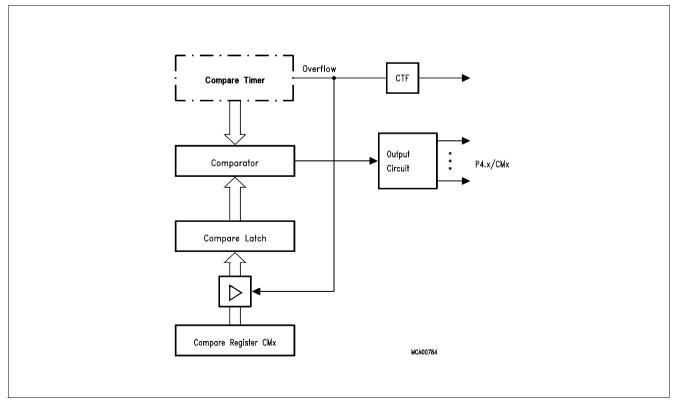

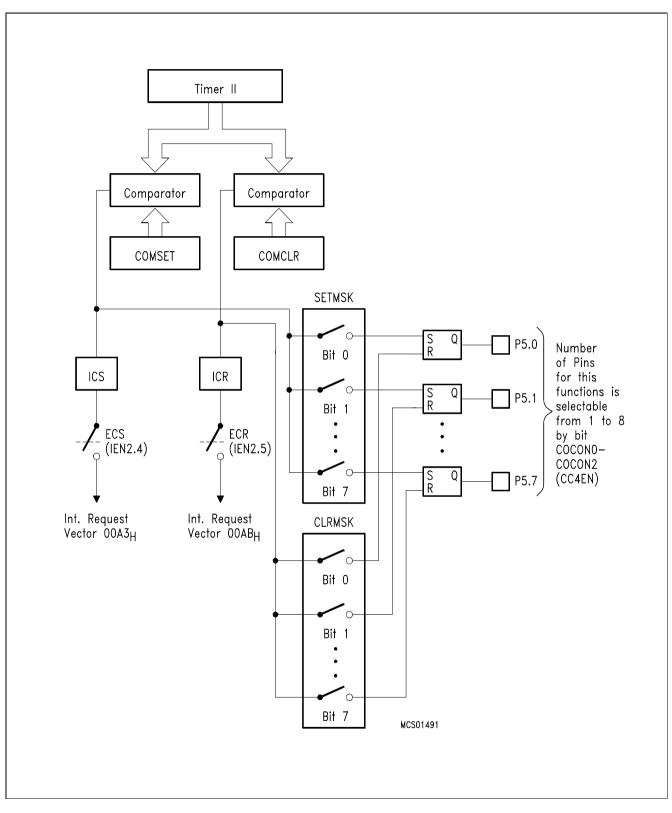

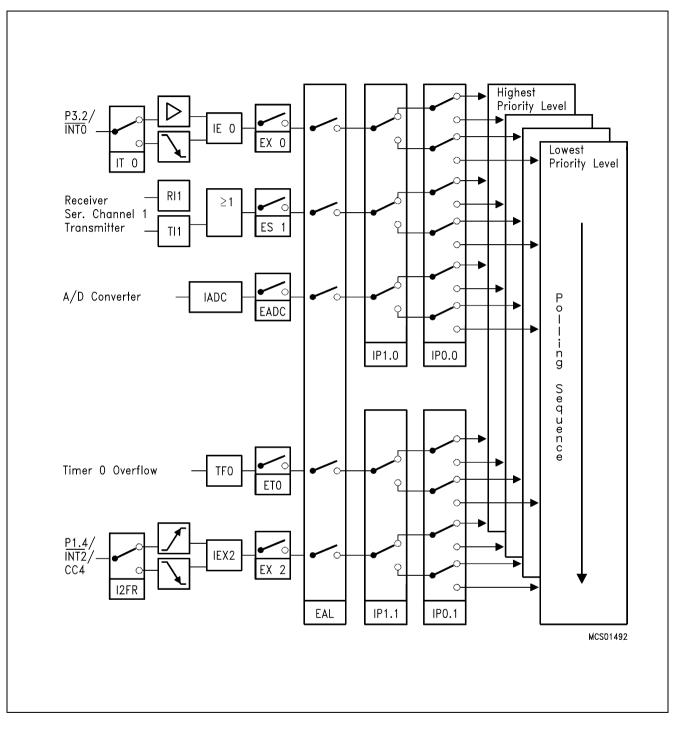

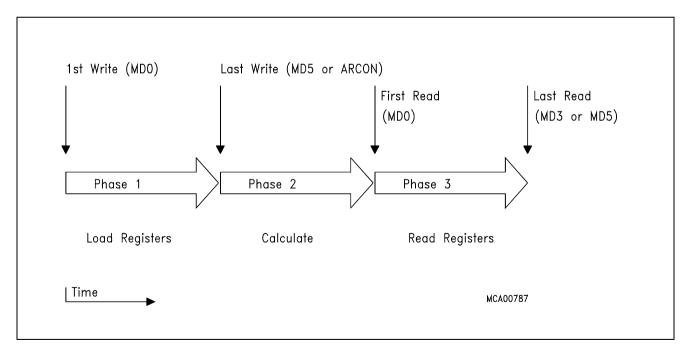

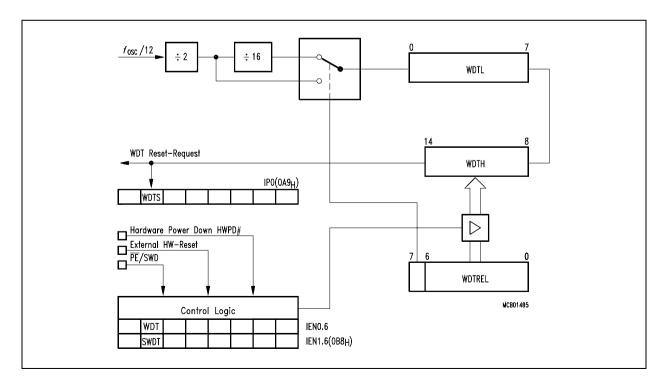

When automatic start of the watchdog was enabled ( $\overline{PE}/SWD$  connected to  $V_{cc}$ ), the Watchdog Timer will start, too (with its default reload value for time-out period).