April 1988 Revised July 1999

### FAIRCHILD

SEMICONDUCTOR

### 74F138 1-of-8 Decoder/Demultiplexer

### **General Description**

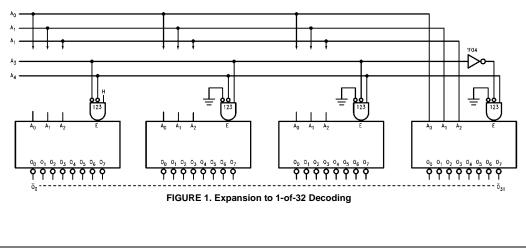

The F138 is a high-speed 1-of-8 decoder/demultiplexer. This device is ideally suited for high-speed bipolar memory chip select address decoding. The multiple input enables allow parallel expansion to a 1-of-24 decoder using just three F138 devices or a 1-of-32 decoder using four F138 devices and one inverter.

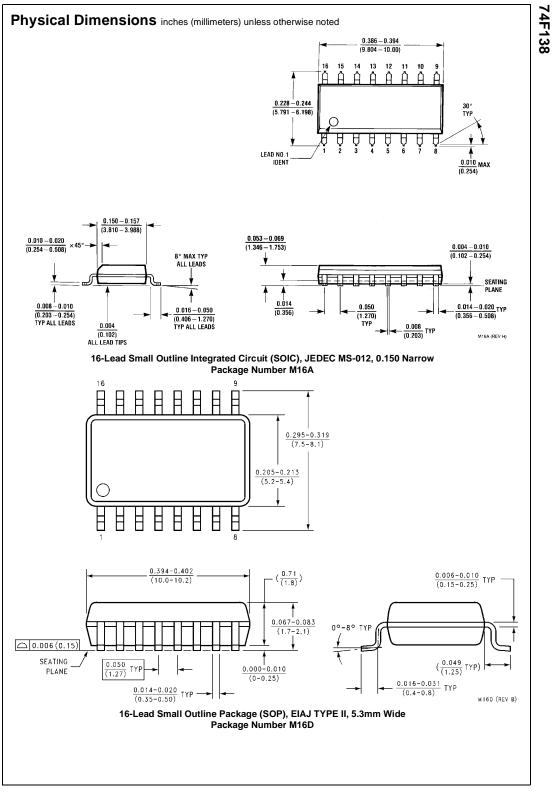

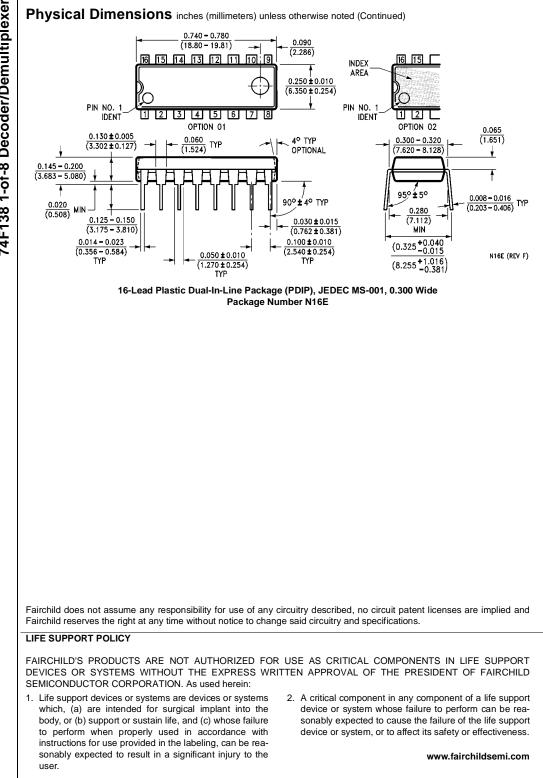

### **Ordering Code:**

| Order Number                                                                                             | Package Number | Package Description                                                         |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| 74F138SC                                                                                                 | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |  |  |  |  |  |

| 74F138SJ                                                                                                 | M16D           | 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |  |  |  |  |  |

| 74F138PC                                                                                                 | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |  |  |  |  |  |

| Devices also available in Tane and Reel. Specify by appending the suffix letter "X" to the ordering code |                |                                                                             |  |  |  |  |  |

**Features**

Demultiplexing capability

■ Multiple input enable for easy expansion

Active LOW mutually exclusive outputs

Specify by appending the suffix letter "X" to the ordering code

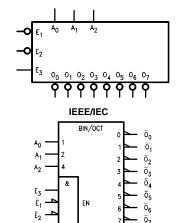

### **Logic Symbols**

### **Connection Diagram**

| $ \begin{array}{c} A_{0} \\ A_{1} \\ A_{2} \\ \bar{E}_{1} \\ \bar{E}_{2} \\ \bar{E}_{3} \\ \bar{D}_{7} \\ GND \end{array} $ | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 0 | $\begin{array}{c} 16 & - v_{CC} \\ 15 & - \bar{0}_0 \\ 14 & - \bar{0}_1 \\ 13 & - \bar{0}_2 \\ 12 & - \bar{0}_3 \\ 11 & - \bar{0}_4 \\ 10 & - \bar{0}_5 \\ 9 & - \bar{0}_6 \end{array}$ |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                             | Ů                                    |   | J 06                                                                                                                                                                                    |

© 1999 Fairchild Semiconductor Corporation DS009478

# 74F138

#### **Unit Loading/Fan Out** U.L. Input I<sub>IH</sub>/I<sub>IL</sub> Pin Names Description HIGH/LOW Output IOH/IOL $A_0 - A_2$ Address Inputs 1.0/1.0 $20 \ \mu\text{A/-0.6 mA}$ $\overline{E}_1, \overline{E}_2$ Enable Inputs (Active LOW) 1.0/1.0 $20\,\mu\text{A/--}0.6~\text{mA}$ Enable Input (Active HIGH) 1.0/1.0 20 µA/-0.6 mA $E_3$ $\overline{O}_{0}-\overline{O}_{7}$ Outputs (Active LOW) 50/33.3 –1 mA/20 mA

### **Truth Table**

| Inputs |                |                |                |                |                |                |                | Outp             | outs             |                  |                  |                  |            |

|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------|------------------|------------------|------------------|------------------|------------|

| Ē1     | E <sub>2</sub> | E <sub>3</sub> | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | 0 <sub>0</sub> | 0 <sub>1</sub> | $\overline{O}_2$ | $\overline{O}_3$ | $\overline{O}_4$ | $\overline{O}_5$ | $\overline{O}_6$ | <u>0</u> 7 |

| Н      | Х              | Х              | Х              | Х              | Х              | Н              | Н              | Н                | Н                | Н                | Н                | Н                | Н          |

| Х      | н              | Х              | Х              | Х              | Х              | н              | Н              | н                | Н                | н                | Н                | н                | н          |

| Х      | Х              | L              | Х              | Х              | Х              | н              | н              | н                | Н                | н                | Н                | Н                | н          |

| L      | L              | н              | L              | L              | L              | L              | Н              | н                | Н                | н                | Н                | н                | н          |

| L      | L              | н              | Н              | L              | L              | н              | L              | н                | Н                | н                | Н                | Н                | н          |

| L      | L              | н              | L              | Н              | L              | н              | Н              | L                | Н                | н                | Н                | н                | н          |

| L      | L              | н              | н              | Н              | L              | н              | Н              | н                | L                | н                | Н                | н                | н          |

| L      | L              | н              | L              | L              | Н              | н              | н              | н                | Н                | L                | Н                | Н                | н          |

| L      | L              | н              | н              | L              | н              | н              | н              | Н                | н                | н                | L                | н                | н          |

| L      | L              | н              | L              | Н              | н              | н              | Н              | н                | Н                | н                | Н                | L                | н          |

| L      | L              | Н              | н              | Н              | н              | н              | Н              | н                | н                | н                | Н                | н                | L          |

H = HIGH Voltage Level

L = LOW Voltage Level X = Immaterial

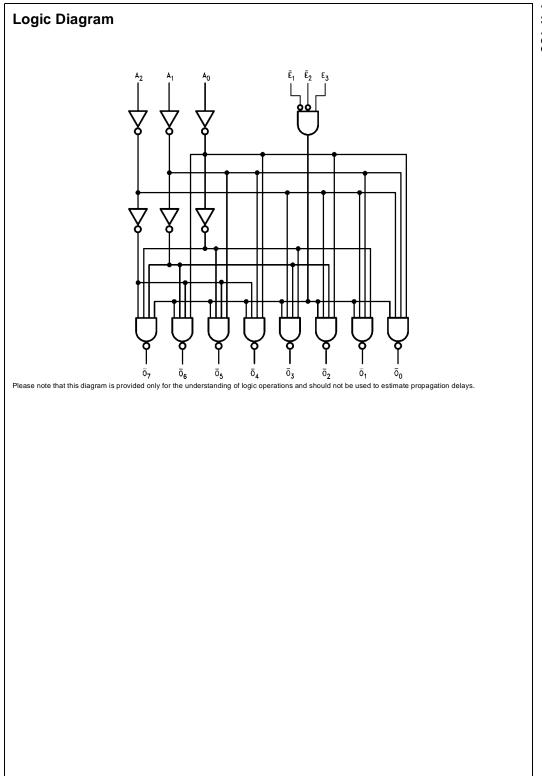

### **Functional Description**

The F138 high-speed 1-of-8 decoder/demultiplexer accepts three binary weighted inputs  $(A_0, A_1, A_2)$  and, when enabled, provides eight mutually exclusive active LOW outputs  $(\overline{O}_0 - \overline{O}_7)$ . The F138 features three Enable inputs, two active LOW ( $\overline{E}_1, \overline{E}_2$ ) and one active HIGH (E<sub>3</sub>). All outputs will be HIGH unless  $\overline{E}_1$  and  $\overline{E}_2$  are LOW and  $E_3$  is HIGH. This multiple enable function allows easy parallel

expansion of the device to a 1-of-32 (5 lines to 32 lines) decoder with just four F138 devices and one inverter (See Figure 1). The F138 can be used as an 8-output demultiplexer by using one of the active LOW Enable inputs as the data input and the other Enable inputs as strobes. The Enable inputs which are not used must be permanently tied to their appropriate active HIGH or active LOW state.

74F138

74F138

### Absolute Maximum Ratings(Note 1)

| Storage Temperature                         | $-65^{\circ}C$ to $+150^{\circ}C$    |

|---------------------------------------------|--------------------------------------|

| Ambient Temperature under Bias              | -55°C to +125°C                      |

| Junction Temperature under Bias             | $-55^{\circ}C$ to $+150^{\circ}C$    |

| V <sub>CC</sub> Pin Potential to Ground Pin | -0.5V to +7.0V                       |

| Input Voltage (Note 2)                      | -0.5V to +7.0V                       |

| Input Current (Note 2)                      | -30 mA to +5.0 mA                    |

| Voltage Applied to Output                   |                                      |

| in HIGH State (with $V_{CC} = 0V$ )         |                                      |

| Standard Output                             | –0.5V to V <sub>CC</sub>             |

| 3-STATE Output                              | -0.5V to +5.5V                       |

| Current Applied to Output                   |                                      |

| in LOW State (Max)                          | twice the rated I <sub>OL</sub> (mA) |

| ESD Last Passing Voltage (Min)              | 4000V                                |

|                                             |                                      |

## Recommended Operating Conditions

| Free Air Ambient | Temperature |

|------------------|-------------|

| Supply Voltage   |             |

0°C to +70°C +4.5V to +5.5V

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

### **DC Electrical Characteristics**

| Symbol           | Parameter                            |                                           | Min        | Тур | Max  | Units | Vcc | Conditions                                           |

|------------------|--------------------------------------|-------------------------------------------|------------|-----|------|-------|-----|------------------------------------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage                   |                                           | 2.0        |     |      | V     |     | Recognized as a HIGH Signal                          |

| VIL              | Input LOW Voltage                    |                                           |            |     | 0.8  | V     |     | Recognized as a LOW Signal                           |

| V <sub>CD</sub>  | Input Clamp Diode Voltage            |                                           |            |     | -1.2 | V     | Min | I <sub>IN</sub> = -18 mA                             |

| V <sub>OH</sub>  |                                      | 10% V <sub>CC</sub><br>5% V <sub>CC</sub> | 2.5<br>2.7 |     |      | V     | Min | $I_{OH} = -1 \text{ mA}$<br>$I_{OH} = -1 \text{ mA}$ |

| V <sub>OL</sub>  |                                      | 10% V <sub>CC</sub>                       | 2.1        |     | 0.5  | v     | Min | $I_{OL} = 20 \text{ mA}$                             |

| IIH              | Input HIGH<br>Current                |                                           |            |     | 5.0  | μA    | Max | V <sub>IN</sub> = 2.7V                               |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test |                                           |            |     | 7.0  | μΑ    | Max | V <sub>IN</sub> = 7.0V                               |

| ICEX             | Output HIGH<br>Leakage Current       |                                           |            |     | 50   | μA    | Max | V <sub>OUT</sub> = V <sub>CC</sub>                   |

| V <sub>ID</sub>  | Input Leakage<br>Test                |                                           | 4.75       |     |      | v     | 0.0 | $I_{ID} = 1.9 \ \mu A$<br>All Other Pins Grounded    |

| I <sub>OD</sub>  | Output Leakage<br>Circuit Current    |                                           |            |     | 3.75 | μΑ    | 0.0 | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded |

| IIL              | Input LOW Current                    |                                           |            |     | -0.6 | mA    | Max | $V_{IN} = 0.5V$                                      |

| I <sub>OS</sub>  | Output Short-Circuit Current         |                                           | -60        |     | -150 | mA    | Max | $V_{OUT} = 0V$                                       |

| ICCH             | Power Supply Current                 |                                           |            | 13  | 20   | mA    | Max | V <sub>O</sub> = HIGH                                |

| I <sub>CCL</sub> | Power Supply Current                 |                                           |            | 13  | 20   | mA    | Max | $V_0 = LOW$                                          |

### **AC Electrical Characteristics**

| Symbol           | Parameter                                                |     | $T_{A} = +25^{\circ}C$ $V_{CC} = +5.0V$ $C_{L} = 50 \text{ pF}$ |     | T <sub>A</sub> = 0°C<br>V <sub>CC</sub> =<br>C <sub>L</sub> = | Units |    |  |

|------------------|----------------------------------------------------------|-----|-----------------------------------------------------------------|-----|---------------------------------------------------------------|-------|----|--|

|                  |                                                          | Min | Тур                                                             | Max | Min                                                           | Max   |    |  |

| t <sub>PLH</sub> | Propagation Delay                                        | 3.5 | 5.6                                                             | 7.5 | 3.5                                                           | 8.5   |    |  |

| t <sub>PHL</sub> | $A_n$ to $\overline{O}_n$                                | 4.0 | 6.1                                                             | 8.0 | 4.0                                                           | 9.0   | ns |  |

| t <sub>PLH</sub> | Propagation Delay                                        | 3.5 | 5.4                                                             | 7.0 | 3.5                                                           | 8.0   |    |  |

| t <sub>PHL</sub> | $\overline{E}_1$ or $\overline{E}_2$ to $\overline{O}_n$ | 3.0 | 5.3                                                             | 7.0 | 3.0                                                           | 7.5   | ns |  |

| t <sub>PLH</sub> | Propagation Delay                                        | 4.0 | 6.2                                                             | 8.0 | 4.0                                                           | 9.0   |    |  |

| t <sub>PHL</sub> | $E_3$ to $\overline{O}_n$                                | 3.5 | 5.6                                                             | 7.5 | 3.5                                                           | 8.5   | ns |  |